Устройство для определения переходов и экстремумов

Иллюстрации

Показать всеРеферат

О ТГИ С А Н И Е ()690488

ИЗОБРЕТЕН ИЯ

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 19.10.76 (21) 2412989/18-24 с присоединением заявки №вЂ” (23) Приоритет— (51) М Кл 2.

CI 06 F 15/20

Государственный хомнтет

СССР оо делам нзооретеннй

N отнритнй

Опубликовано 05.10.79. Бюллетень №37 (53) УДК 681.14 (088.8) Дата опубликования описания 15.10.79 (72) Авторы изобретения

И. А. Малицкий, В. А. Озеров, Л. А. Шойхет и В. П. Яворский

Киевский институт автоматики имени XXV съезда КПСС(71) Заявитель (54) УСТРОЛСТВО ДЛЯ ОПРЕДЕЛЕНИЯ

ПЕРЕХОДОВ И ЭКСТРЕМУМОВ

Изобретение относится к области измерительной техники.

Известны устройства для определения экстремумов, используемые в радиотехнических устройствах и приборах для статистического учета и анализа, содержащие регистры, элементы И, ИЛИ (1).

Недостатком известных устройств является низкая надежность.

Наиболее близким по технической сущности к данному является устройство для определения переходов и экстремумов, содержащее первый и-разрядный запоминающий регистр, первую группу из п элементов

И и первый элемент ИЛИ, причем единичйые выходы первого п-разрядного запоминающего регистра соединены с первыми входами соответствующих элементов И первой группы, вторые входы которых подключены к первому входу устройства 12).

В случае изменения входной величины так, что ее значения попадают не в соседний разряд (поддиапазон), -а через один или несколько разрядов, функционирование указанного выше устройства нарушается (происходят сбои) . Данное устройство не позволяет определять переходы значений входной величины между разрядами ее значений.

Целью настоящего изобретения является повышение надежности устройства.

Поставленная цель достигается тем, что в устройство введены п-разрядный запоми нающий регистр, вторая группа из п(п — 1) элементов И, второй элемент ИЛИ и триггер, причем выходы элементов И первой группы соединены с единичными входами соответствующих разрядов второго п-разрядного запоминающего регистра, нулевые входы которых подключены ко второму входу устройСтва, единичные выходы второго и-разрядных запоминающих регистров соединены с первыми входами элементов И второй то группы, вторые входы которых подключены к единичным выходам соответствующих разрядов первого и-разрядного заломинающего регистра, выходы элементов И второй группы соединены с соответствующими входами

2с ервого и второго элементов ИЛИ, Выход второго элемента ИЛИ подключен к единичнойту входу триггера, выход первого элемента ИЛИ соединен с нулевым входом триггера.

600>! 88

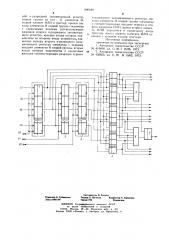

На чертеже представя;.- .и блок-схема устройства для определения переходов и экстремумов.

Устройство для определения переходов и экстремумов содержит первый и-разрядный запоминающий регистр 1 единичные выходы которого через первую группу из и элементов И 2 соединены со вторым и разрядным запоминающим регистром 3. 11ерная группа из и элементов И 2 служит для параллельного перенося информации из первого п-разрядного запоминающего регистра во второй и-разрядный запомни(!!Оц(ИЙ регистр 3, для чего другие входы первой гр: .пы из и элементов И 2 соединен(-.. первым входом устройства Y 1, по кото(их,(, приходит команда «перезапись». Ну.: ые входы пеpBol о и второго п -1эаз ряд f f1 х 3 я по миня (Ощих регистров и 3 подклю п.lll>I соответсTвенно к третьему Y 3 и второму Y 2 вх(.дям уст)эойств а. 1.ди ни I (п>lе Ll ьl xo>I ы г!ср вого и второго и-разрядных запомни;1ющих регистро!1 1 и 3 coc(L(f f fe«f>I со второй группой из и (и — 1) э. !е(>!е1!тов И 4, 0(lpe, LQ. Is!loll!I! >Ill вид перехода, тяк, ITo !1-й разряд второго и-разрядного заломи!!я!Ощс го, регистры 3 соединен с первыми входами (и — — 1) элементов И второй гру(шы 4, ко вторым входам которых подключены все разряди! первого и-разрядного запоминяюп(сго регистра !, кроме п-го.

Выходы элементов И второй группы 4 служат для регистрации переходов и соединены со входами первого элемента ИЛИ 5, когда разность номеров разрядов перво"o и вт Ор О ГО и - 1э а 3 p яд н ь! х 3 я по м и н я 10 щ их p е -гистров lи3,,подключенных к элементу И второй группы 4, положительна, в против!>юм случае выходы элементов И второй группы

4 соединены со входами второго элемента

ИЛИ 6. Выходы первого и второго элементов

ИЛИ 5 и 6 подкл(очены соответственно к нулевому и единичному входам триггера 7, с нулевого выходя которого снимается сигнал для регистрации экстремумов вход!ой вел ич и ны.

Диапазон измененпя контролируемой величины разбивается на и разрядов. Сигнал отвечя(ощ;!й! определенному разряду входной величины (Х1, Х2, ХЗ, ... Хп) подается на соответствующий единичный вход первого и-разрядного запоминающего регистра . !.

При этом на первом п-разрядном запоминающем регистре срабатывает триггер, соответствующий этому разряду, однов эеменно по второму входу Y 2 устройства приходит импульс сброса второго п-разрядного запоминающего регистра 3> затем по верхнему входу устройства Y l поступает импульс «разрешение перезаписи». По этой команде открывается соответствующий э.leмент И первой группы 2 и происходит параллельHûé перенос информации с первого иразрядного запоминягощего регистра во второй 3. 11осле этого по гретьемч входу

Y 3 приходит импульс сброся первого и-разрядпого запоминающего регистра

Если при изменении входной величины значение ее окажется в любом другом диапазоне, то на соответствующий единичный вход первого п-разрядного запоминаюп!его регистра поступает сигнал, который запоминается этим регистром. Таким образом, на первом п-разрядном запоми(гаюп(ем регистре 1 будет храниться информации о разряде, в котором находилась входная величина во время последнего измерения, g во втором п-разрядном запоминающем регистре 3 — информация о предыдущем измерении. Состояния обоих п-разрядных запоминающих регистров сравнив".,þòñH 1Ia элементах И второй группы 4. состо(ццей из и (и — — 1) элементов, каждый из которых соответствует определенному переходу. Выходы второй групп»l из и (п — I) элементов И 4 (!спользу(отс>! для регистрации переходов и связи с первым и вторым элементами ИЛИ соответственно 5 и 6, причем сигналы с выходов элементов И второй группы 4, фиксирующие переходы контролируемой величины с меньшего разрлда в боль>> 3 ший, поступают на первый элемент ИЛИ 5, а с большего в меньший — «a второй. эле.мент ИЛИ 6. Сигнал с первого элемента

ИЛИ 5 поступает на нулевой вход триггера 7 а с выхода второго элемента ИЛИ 6

36 ня единичный вход. Таким образом, при увеличении зйячения входной величины сигналы будут ":(oeòós(àòü только на нулевой вход триггера 7 и он будет находиться в одном устойчивом состоянии, а при уменьшении значения входной величины сигналы бу33 дут поступать на единичный вход триггера 7 и он опрокидывается в другое устойчивое состояние. Момент опрокидывания триггера будет соответствовать экстремальному значению входной величины.

Использование второго п-разрядного

@г! запоминающего регистра, второй группы из и (п — i ) элементов И, второго элемента

ИЛИ и триггера позволяет повысить надежность устройства, что выгодно отличает предлагаемое устройство от указанного прототипа.

Формула изо>бретеная

Удтро!!ство для определения переходов и экстремумов, содержащее первый п-разрядный запоминающий регистр, первую группу из и элементов И и первый элемент

ИЛИ, причем единичные выходы первого п-разрядного запоминакэщего регистра соединены с первыми входами соответствующих элементов И первой группы, вторые входы которых подключены к первому входу устройства, отличающееся тем, что, с целью повышения надежности, э него введены вто690488

Составитель И. Хазова

Текред О. Луговая 1(орректор А. Гриценко

Тирам 780 Подам иое

Редактор Э. Губницкая

Заказ 5967I46

ЦН И И П И Государственного комитета СССР . по делам изобретений н открытий

113035, Москва, )К вЂ” 35; Раушская наб., д. 4/5

Филиал ППЯ к Патента, r. Ужгород, ул. Проектная, 4

3 рой и-разрядный запоминающий регистр. вторая группа из п(п — 1) элементов И, второй элемент ИЛИ и триггер, причем выходы элементов И первой группы соединены с единичными входами соответствующих разрядов второго п-разрядного запоминающего регистра, нулевые входы которых подключены ко второму входу устройства, единичные выходы второго и-разрядного запоминающего регистра соединены с первыми входами элементов И второй группы, вторые входы которых подключены к единичным выходам соответствующих разрядов первого и-разрядного запоминающего регистра, вы ходы элементов И второй группы соединены с соответствующими входами первого и второго элементов ИЛИ, выход второго элемента ИЛИ подключен к единичному входу триггера, выход первого элемента ИЛИ соединен с нулевым входом триггера.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 4!6698, кл. G 06 Г !5/36, l973.

10 2. Авторское свидетельство СССР № 438005, кл. G 05 В l3//02, !973.