Устройство для лексического анализа

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. санд-ну— (22) Заявлено 300376 (21) 2339850/18-24 с присоединением заявки М— (23) Приоритет—

Опубликовано 051 079 Бюллетень М 37

Дата опубликования описания 08.1 07 9

Союз Советских

Социалистических

Республик >690497 (51)м. Кл.

G 06 F 15/38

Государственный комитет

СССР по делам изобретений и открытий (5З) УДК 681. 325 (088 .8 ) (72) . Автор изобретения

В .А . Платонов (71) Заявитель таганрогский радиотехнический институт им. B.ä. калмыкова (54) УСТРОЙСТВО ДЛЯ ЛЕКСИЧЕСКОГО АНАЛИЗА

Устройство относится к области вычислительной техники и может быть использовано в устройствах ввода циф- ровых вычислительных машин.

Известно устройство для транслирования программ, содержащее блок Управления, блок подсветки, блок хранения символов языка, блок выделения команды, блок хранения адресов, блок хранения описаний, формирователи, блок вывода (1) .

Однако данное устройство имеет большой объем оборудования.

Наиболее близким к данному изобретению техническим решением является селекторный канал, содержащий первый, второй и третий элементы ИЛИ-И, выходы которых являются соответственно выходами функциональных символов, переменных, чисел устройства, блок оперативной памяти, выход которого соединен с первыми входами первого, второго и третьего злементон ИЛИ-И, дешифратор входных символов, соединенный двусторонними связями с блоком оперативной памяти, вход дешифратора входных символов является входом устройства (2).

Недостатком устройства является то, что при вводе символов их коды без всяких лексических преобразований передаются в оперативную память вычислительной машины.

Затем в процессоре вычислительной машины произнодится анализ введенного текста с помощью специальной программы-транслятора. При этом, прежде всего, выполняется лексический анализ, при котором из последовательности кодов выделяются первичные семантические структуры — слова (функциональные символы, разделители, переменные, числа и др.). После этого производится синтаксический и семантический анализ входной информации.

Выполнение программы транслятора уменьшает быстродействие вычислительной машины.

Пелью изобретения является увеличение быстродействия.

Постанленная цель достигается тем, что устройство содержит четыре элемента И, первый и второй триггеры, едини .ными выходами соединенные с перными входами соответственно первого и третьего элементов И, а нулевыми выходами — c первыми входами соответственно второго и четвертого элементов И, первый ныход дешифратора входных символов соединен с вто690497 рым входом первого элемента ИЛИ-И, выход которого соединен. с нулевым входом первого триггера, второй выход дешифратора входных символов соединен с единичным входом первого триггера, третий выход дешифратора входных символов соединен с вторыми входами первого и второго элементов

И, выходы которых соединены с третьим и вторым входами соответственно первого и второго элементов ИЛИ-И, четвертый выход дешифратора входных символов соединен с единичным входом второго триггера и третьим входом второго элемента ИЛИ-И, четвертый вход которого соединен с выходом

15 третьего элемента И и нулевым входом второго триггера, пятый выход дешифратора входных символов соединен с вторыми входами третьего и четвертого элементов И, выход четвертого элемента И соединен с вторым входом третьего элемента ИЛИ-И.

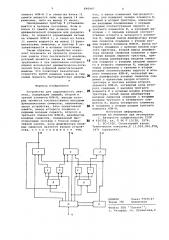

На чертеже представлена блок-схема устройства. устройство содержит элементы 25

ИЛИ-И 1-3, элементы И 4-7, триггеры

8 и 9, дешифратор 10 входных символов, блок 11 оперативной памяти.

Элементы И 4-7 и ИЛИ-И 1-3 служат.для обеспечения выполнения логи- Я ческих условий при передаче управляющих сигналов.

Триггеры 8 и 9 служат для запоминания состояния устройства лексического анализа. Триггер 8 фиксирует 3$ состояние, когда формируется буквенный функциональный символ (kiri, tg, sgrt и т.п.), триггер 9 когда формируется переменная (a15, у10 и т.д.), Дешифратор 10 служит для анализа,щ поступающих на его вход с входа 12 устройства литер и выдачи управляющих сигналов на формирование в блоке

11 слов из этих литер и на передачу этих слов (функциональных символов, разделителей, переменных и чисел) на соответствующие выходы 13-15., Блок 11 оперативной памяти используется для накопления, хранения и выдачи, слов текста задачи. Своим входом и выходом он соединен с дешифратором 10 входных символов, другой выход соединен с соответствующими входами элементов ИЛИ-И 1-3.

Решаемая задача, записанная на алгоритмическом языке в виде кодов Я литер, из которых составлены слова, поступает последовательно литера за литерой в дешифратор 10, где каждая поступающая литера сравнивается с предыдущей литерой, записанной в бло- @ ке 11 оперативной памяти. В зависимости от сочетания литер в блоке 10,,элементах И 4-7 и ИЛИ-И 1 — 3 вырабатываются следующие управляющие сигналы.

Если поступающая литера буква, а в блоке 11 оперативной памяти были также записаны буквы, то поступающая буква записывается в блок 11 памяти и триггер 8 устанавливается в единичное состояние. Если же в блоке 11 памяти был записан знак арифметической операции или разделитель, то подается управляющий сигнал на элемент ИЛИ-И 1 и слово из блока 11 папамяти выдается на выход 13 функциональных символов„ а триггер 8 устанавливается в нулевое состояние.

Если поступающая литера цифра, а в блоке 11 памяти была буква, то подается управляющий сигнал на элемент

ИЛИ-И 2 и слово из блока 11 памяти выдается на выход 14 переменных, одновременно подается сигнал на единичный вход триггера, 9. Если в блоке 11 памяти — цифра, то поступающая цифра записывается в блок 11 памяти. Если в блоке 11 памяти был знак арифметической операции или разделитель, то подается управляющий сигнал на элемент ИЛИ-И 1 и слово из блока 11 памяти выдается на выход 13 функциональных символов, а триггер 8 устанавливается в нулевое состояние.

Если поступающая литера — знак арифметической операции, а в блоке

11 памяти была записана буква, то подается управляющий сигнал на элемент ИЛИ-И 2 и слово из блока 11 памяти выдается на выход 14 переменных, одновременно триггер 9 устанавливается в единичное состояние. Если в блоке 11 памяти были записаны цифры, то в зависимости от состояния триггера

9 подается управляющий сигнал на элементы ИЛИ-И 2 или ИЛИ-И 3 и слово из блока 11 памяти выдается либо на выход 14 переменных, как индекс переменной, либо на выход 15 числа. Если триггер 9 находится в единичном состоянии, то одновременно с выдачей слова на выход 14 переменных, он устанавливается в нулевое состояние.

Если в блоке 11 памяти был записан разделитель, то подается управляющий сигнал на элемент ИЛИ-И 1 и слово из блока 11 памяти выдается на выход

13 функциональных символов, а триггер 8 устанавливается в нулевое состояние.

Если поступающая литера была разделителем, а в блоке 11 памяти была записана буква, то в зависимости от состояния триггера 8 подается управляющий сигнал на элемент ИЛИ-И 1 или

ИЛИ-И 2 и слово из блока 11 памяти выдается либо на.выход 13 функциональных символов, либо на выход 14 переменных.

Если в блоке 11 памяти была записана цифра, то в зависимости от состояния триггера 9 подается управляющий сигнал на элемент ИЛИ-И 2 и

690497

Формула изобретения элемент ИЛИ-И 3 и слово из блока 11 памяти выдается либо на выход 14 переменных, либо на выход 15 чисел, Одновременно триггер 9 устанавливается в нулевое состояние. Если в блоке 11 памяти был записан знак арифметической операции или разделитель, то подается управляющий сигнал на элемент ИЛИ-И 1, и слово из блока

11 памяти выдается на выход 13 функциональных символов, а триггер 8 ус- 1р танавливается в нулевое состояние, Таким образом, устройство позволяет исключить из процесса трансляции задачи этап лексического анализа, которыЯ является одним из наиболее трудоемких и при выполнении которого обычно используют арифметическо-логический блок цифровой вычислительной машины. Это позволяет значительно сократить время решения задачи и тем самым повысить быстродействие машины, Устройство для лехсического ана- ü6 лиза, содержащее первый, второй и третий элементы ИЛИ-И, выходы которых являются соответственно выходами функциональных символов, переменных, чисел устройства, блок оперативной 30 памяти, выход которого соединен с первыми входами первого, второго и третьего элементов ИЛИ-И, дешифратор входных символов, соединенный двусторонними связями с блоком опера- 3$ тивной памяти, вход дешифратора входных .символов является входом устройства, о т л и чающее с я тем, что, с целью повышения быстродействия, оно содержит четыре элемента И, первый и второй триггеры, единичными выходами соединенные с первыми входами соответственно первого и третьего элементов И, а нулевыми выходами — с первыми входами соответственно второго и четвертого элементов И, первый выход дешифратора входных символов соединен с вторым входом первого элемента ИЛИ-И, выход когорого соединен с нулевым входом первого триггера, второй выход дешифрагора входных символов соединен с единичным входом первого триггера, третий выход дешифратора входных символов соединен с вторыми входами первого и второго элементов И, выходы которых соединены с третьим и вторым входами соответственно первого и второго элементов ИЛИ-И, четвертый выход дешифратора входных символов соединен с единичным входом второго триггера и третьим входом второго элемента ИЛИ-И, четвертый вход кото" рого соединен с выходом третьего элемента И и Нулевым входом второго триггера, пятый выход дешифратора входных символов соединен с вторыми входами третьего и четвертого элементов И, выход четвертого элемента

И соединен с вторым входом третьего элемента ИЛИ-И.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

М 436356, кл. G 06 F 15/20, 1974.

2. ЕС-1020. Селекторный канал.

Техническое описание,Е 13.055.001.Т03, 1971 (прототип).

ЦНИИПИ Заказ 5968/47

Тираж 780 Подписное

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4