Полупостоянное запоминающее устройство

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДИТВЛЬСТВУ

Союз Соввтских

Социалистических

Ресяубпик

690562 (61) Дополнительное к авт. свил-ву (22) Заявлено 26,01.76 (21) 23 19188/18-24 с присоединением заявки № (23) Приоритет (51) М. Кл

G 11 С 7/00

G 11 С 11/00

Йщаерстнанный неинтат

СССР на данаи нэфратаннд н аткрьпнй

Опубликовано 05.10.79 Бюллетень № 37 (53) УДК

681.327.66 (088.8) Дата опубликования описания 05,10.79 (72) Авторы изобретения

К. А. Пупков, В. Ю. Толкачев и 10 В. Толкачев

Московский институт электронного машиностроения (54) ПОЛУПОСТОЯННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к устройствам вычислительной техники и может быть использовано в микропрограммных устройствах управления (ЭВМ) электронно-вычислительной машиной, Известны полупроводниковые полупостоянные запоминающие устройства с электрической записью информации, в которых, однако, стирание ранее записанной информации производится облучением накопителя (1j.

Наиболее близким по технической сущное. ти к изобретению является полупостоянное запоминающее устройство, содержащее накопитель, выходные шины которого подключены к входам элементов НЕ, регистр записи и регистр адреса, синхронизирующие входы которых подключены к выходу тактового генератора, триггер перезаписи, формирователя стирания и записи, выходы которых связаны с входными шинами накопителя, и дешифратор адреса словарной строкй, выходные шины которого подключены к входам буферных ключей (2).

Недостатками этого устройства является низкая надежность, поскольку при перезаписи стирание символа производится независимо от его значения, что может привести к снижению срока службы накопителя или да5 же выходу его из строя при критичности его элементов, и низкое быстродействие, связанное с позлементным считыванием информации из накопителя..

Целью настоящего изобретения является

10 повышение надежности и быстродействия устройства.

Эта цель достигается тем, что в устройство введены две группы элементов И, причем пер-. вые входы элементов И первой группы связаIЗ, ны с выходными шинами накопителя, вторые входы элементов И первой группы связаны с нулевым выходом триггера перезаписи, третьи входы элементов И первой группы связаны с нулевыми выходами регистра записи, едизВ ничные выходы которого соединены с первыми входами элементов И второй группы, вторые входы которых соединены с единич. ным выходом триггера перезаписи, третьи...

690562

3 в.:оды элементов И второй группы соединены с выходили элементов НЕ, выходы элементов И Нерпой группы подключены к входам формйрМатюлей стирания, выходы элементов И втй1йй бэппы — к входам формирователей задней;

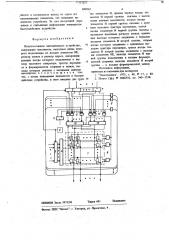

На чертв@е фйдставлена блок-схема полупостоянноГб за11бминающего устройства, Устройствб сбДержит накопитель 1 на элементах 2 С йа11аэрушающим считываниЕм информации, иййрймер ионотронных полевых транзисторах, регистр адреса 3, дешифратор адреса словарной строки 4, тактовый генератор 5, группу .буферных ключей 6, регистр записи 7, группу элементов НЕ 8, первую

9 и вторую 10 группы элементов И, триггер перезаписи 11, формирователи стирания .12 и формирователи записи 13.

При необходимости перезаписи информации в накопителе 1 запускается тактовыи генера20 тор 5, период следования выходных импульсов которого определяет длительность цикла перезаписи. Триггер перезаписи 11 переходит из одного устойчивого состояния в другое два

25 раза в течение одного цикла перезаписи, причем момент первого переброса совпадает с " начат1ом цикла перезаписи, а момент второго переброса делит его пополам на полупериод стирания и полунериод записи.. Итак, в ис30 ходком состоянии, то есть к началу очередного цикла перезаписи, в триггере перезаписи

11 записан нуль, в регистре записи 7 — код, подлежащий записи в некоторую словарную строку накопителя 1, а в регистре адреса 3—

35 код, соответствующий номеру зтои словарнон строки. В течение полупериода стирания на нулевом выходе триггера перезаписи 11 потенциал соответствует логической единице, по зтъму" сигналы могут появиться только на выходах первой группы 9 элементов И. Пусть в i-м разряде, выбранной дешифратором 4 словарной строки, была записана единица, а записать из i-ro триггера регистра записи 7 необходимо нуль. В этом и только в этом

;случае на все три входа i-го элемента И из .группы 9 поступают единицы: с нулевого выхода i-ro триггера регистра записи 7, с нулевого триггера перезаписи 11 и с выхода i ro запоминающего элемента накопителя 1, Поэтому на выходе i-го элемента И из группы 9 тоже появится единица, которая, поступая на вход i-го формирователя стирания (12j„), вызывает генерацию импульса стирания, в результате чего i-й запоминающий элемент данной словарной строки переходит в состояние нуля.

В койце полупериода стирания триггер перезаписи ll перебрасывается иэ нуля в единицу. И во второй половине цикла перезаписи, 4 то есть полупериоде записи, на единичном выходе триггера перезаписи 11 потенциал соответствует единице, поэтому сигналы могут появиться только на выходах второй группы 10 элементов И. Пусть в I-м разряде, выбранной

1 дешифратором 4 словарной строки, был записан нуль, а записать из i-ro триггера регистра записи 7 необходимо единицу. В этом и только в этом .случае на все три входа

i-ro элемента И из группы 10 поступают единицы: с единичного выхода i-го триггера регистра записи 7, с единичного выхода триггера перезаписи 11 и с выхода i-го элемента НЕ из группы 8, на выход которого поступает нуль с выхода i-го запоминающего элемента накопителя 1. Поэтому на выходе

i-го элемента И из группы 10 тоже появится единица, которая поступая на вход i-го формирователя записи (13„), вызывает генерацию импульса записи, в результате чего

1-й запоминающий элемент данной словарной строки переходит в состояние единицы. Таким образом, если предшествующий символ в запоминающем элементе и вновь записываемый символ из соответствующего разряда регистра записи 7 не совпадают, то есть единица-нуль или нуль-единица, то импульс перезаписи будет проходить через этот запоминающий элемент только в одном из двух полупериодов, то есть соответственно в полупериоде стирания или в полупериоде записи. Если же рассматриваемые символы совпадают, то есть нуль-нуль или единица-единица, то ни в полупериоде стирания, ни в полупериоде записи через запоминающий элемент импульсы перезаписи проходить не будут, и он в течение всего цикла перезаписи остается без изменения.

Импульсы стирания и записи имеют противоположную полярность. Длительность импульса на выходе дешифратора адреса словарной строки 4 равна длительности цикла перезаписи, и этот импульс не только производит считывание информации из выбранной словарной строки, но также открывает соответствующий буферный ключ из группы 6, через который проходит импульс перезаписи в данном цикле. В конце данного цикла перезаписи триггер перезаписи 11 снова перебрасывается в нуль, а сиихрдимпульсом с выхода тактового генератора 5 осуществляется запись информационного кода в регистр записи 7 и адреснога кода — в регистр адреса 3. Эти коды поступают иэ внешних Во отношениюкописываемому устройству блоков. Полупостоянное запоминающее устройство пришло в исходное состояние. Полупостоянное запоминающее устройство выгодно отличается от прототипа, так .как увеличивается срок службы нако690562

° °

Подписное

КНИИПИ Заказ 5975/50 Тираж 681

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4 пителя и исключается выход из строя его запоминающих элементов, что повышает надежность устройства. 3а счет построчной перезаписи и считывания информации повышается быстродействие устройства.

Формула изобретени я

Полупостоянное запоминающее устройство, содержащее накопитель, выходные шины которого подключены ко входам элементов НЕ, регистр записи и регистр адреса, синхронизирующие входы которого подключены к выходу тактового генератора, триггер перезаписи и формирователи стирания и записи, выходы которых связаны с входными шинами . накопителя, о т л и ч а ю щ е е с я тем, что, с целью повышения надежности и быстродействия устройства, в него введены две труп пы элементов И, причем первые входы элементов И первой группы связаны с выходными шинами накопителя, вторые входы элементов И первой группы связаны с нулевым выходом триггера перезаписи, третьи входы элементов И первой группы связаны с нулевыми выходами регистра записи, единичные выходы которого соединены с первыми входами элементов И второй группы, вторые входы которых соединены с единичным выходом триггера перезаписи, третьи входы элементов И второй группы соединены с выходами элементов НЕ, выходы элементов И первой группы подключены к входам формирователей стирания, выходы элементов И второй группы — к входам формирователей записи.

Источники информации, принятые во внимание при экспертизе

1. "Электроника, 1975, т. 48, У 17, с. 80.

>0 2. Патент CIUA Р 3886532, кл. 340 †17