Запоминающее устройство с автономным контролем

Иллюстрации

Показать всеРеферат

Г s. .. -:. -Я

ИЗОБРЕТЕНИЯ

Союз Советских

Сециалистических

Республик

rir>690567 (61) Дополнительное к авт. свид-ву (22) Завалено 33„06.75 (21) 216 3481/18-24 (51)М. Кл.

G 11 С 29/00

Государственный квинтет

СССР по делам изобретений и открытий (23) Приоритет (53) УДК 681. 327. 6 (088.8) Олубликоввие 05.1079. Бюллетень ЙЯ 37

Дата опубликоваиия описания 0 5,10.79

{72) Авторы изобретения

В.С.Голоборщенко, В.К. Ерохов ец; П.И.Луговцов и В.Д. Трофимов (71) заявитель (54) ЗАПОИИНИОЩЕЕ УСТРОЙСТВО С ABTOHOMHbN

КОНТРОЛЕИ

Изобретение относится к вычислительной технике и может быть использовано при построении запоминающих устройств на различной основе (например, на ферритовых сердечниках, тонких магнитных пленках, полупроводниковых интегральных микросхемах и т.д.).

Известны запоминающие устройства, которые обеспечивают проверку работоспособности ЗУ с помощью специальных контрольных тестов f.1).

Наиболее близким по технической сущности к предложенному изобретению является устройство, содержащее накопитель, одни выходы которого соединены с соответствующими выходами разрядных формирователей записи, а другие - с соответствующими 2П выходами дешифратора адреса, входы которого подключены к выходам регистра адреса, соединенными с входами блока индикации регистра адреса, первый вход регистра адреса подклю- g5 чен к первому входу блока управления, второй выход блока управления соединен с первым входом- счетчика команд контроля, второй вход которого подключен к соответствующему выходу ре гис тра адреса, - выходы н ако пи т ел я подключены к соответствующим входам усилителей воспроизведения, выходы которых соединены с соответствующими входами регистра числа, первый вход которого соединен с выходом элемента ИЛИ, первые выходы регистра числа соединены с соответствующими входами разрядных формирователей записи и блока индикации регистра числа, а вторые - с соответствующими входами блока анаЛиза считанной контрольной информации, первый вход которого соединен с третьим выходом блока управлениК, второй входсоответствующим выходом регистра адреса (2).

Однако зто устройство характеризуется невысоким быстродействием и низкой степенью автономности в режиме контроля. Потеря быстродействия определяется временем записи исправленного числа в резервную ячейку, а адреса резервной ячейки в имеющиеся исправные разряды отказавшей ячейки. При отсутствии в отказавшей ячейке исправных разрядов контроль вообще не возможен. Кроме этого, контроль не может осущест6 90567 вляться автономно, так как на вход. этого устройства необходимо извне подавать команды в режиме контроля.

Цель изобретения - повышение быстродействия запоминающего устройства.

Поставленная цель достигается тем, что в устройство введены генератор одиночных импульсов, генератор импульсов, элемент И, триггер неисправности, триггер контроля, блок формирования контрольной информации, дешифратор команд контроля, блок индикации команд контроля, блок индикации триггера неисправности, и триггер контроля, при этом выход триггера контроля соединен с первым входом элемента И, входом блока индикации триггера контроля и первым входом блока управления, первый выход триггера неисправности соединен со вторым входом элемента И и вторым входом блока управления, а второй выход - со входом блока индикации триггера неисправности, выход элемента И соЕдинен со входом генератора импульсов, выход которого под- 25 ключен ко второму входу регистра адреса„ вход дешифратора команд контроля соедйнен с выходом счетчика команд контроля у один выход дешиф ратора команд кОнтроля соединен с пер"д вым входом триггера контроля,а другие выходы - с соответствующими выходами блока управления, блока индикации команд контроля, блока формирования контрольной информации и блока анализа считанной контрольной информации, выход которого соединен с первым входом триггера неисправности, выход генератора одиночных им" пульсов соединен со вторыми входа ми тригтеРа контроля и триггера неисправности,: первый выход блока формирования контрольной информации соединен;са вторым входом элемента

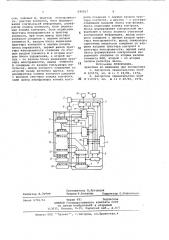

ИЛИ, второй — со вторым входом регистра числа. На чертеже представлена блоксхема устройства-, которое содержит генератор одиночйых импульсов 1, триггер контроля 2, триггер неисправности 3, блок управления 4, элемент И 5, генератор импульсов б, регистр адреса 7, счетчик команд контроля 8, дешифратор команд кон-. троля 9, блок формирования контрольной информации 10, регистр числа

1l элемент ИЛИ 12, разрядные формирователи записи 13, дешифратор адреса 14, накопитель 15, усилители воспроизведения 16, блок анализа 60 считанной контрольной информации 17, блок индикации триггера контроля 18, блок индикации триггера неисправности 19, блок индикации команд контроля 20, блок индикации регнст- 65 ра числа 21, блок индикации регистра адреса 22.

Для автономного кон троля работоспособности ЗУ резервируется определенный интервал времени (перед началом работы описываемого устройства с устройством-пользователем или в паузах совместной работой этих устройств), в течение которого автоматически форьыруется контрольный тест (гяжелый код), производится его запись, считывание, анализ считанной информации и формирование сигнала исправности в конце контроля. Для ЗУ на ферритовых сердечниках,.например, в основу проверки работоспособности может быть положен тяжелый код- шахматный .

Устройство работает- следующим образом.

По сигналу генератора 1 одиночных импульсов триггер 2 койтроля и триггер 3 неисправности устанавливаются в единичное состояние, сигналы с первых выходов подаются на соотвеТствующие входы блока 4 управления, производя блокировку Зу от приема внешних команд, и через элемент И 5 запускают генератор импульсов 6. Одновременно с этим сигналами с блока управления 4 устанавливаются в исходное (нулевое) состояние регистр ацреса 7, счетчик. команд контроля 8 и регистр числа 11. Нулевому состоянию счетчика команд контроля 8 соответствует возбуждение первого выхода дешифратора команд контроля 9, по сигналу которого в блоке управления 4 формируется команда ЗАПЙСЬ ТЯЖЕЛОГО КОДА . Сигнал возбужденного выхода дешифратора команд контроля 9 совместно с сигналом мпадшего разряда регистра адреса 7 и сигналом с выхода блока управления 4 управляют работой блока 10 формирования контрольной информации, с выхода которого сигналы поступают на нулевой установочный вход (через элемент ИЛИ 12) - или на единичный установочный вход регистра числа ll, Информация из регистра числа ll через разрядные формирователи записи 13 записывается в соответствующую ячейку накопителя

15, которая определяется дешифратором адреса 14 в соответствии с состоянием регистра адреса 7.

Последний периодически изменяет свое состояние под действием сигналов, поступающих на его счетный вход с выхода генератора импульсов

6. Команда ЗАПИСЬ ТЯЖЕЛОГО КОДА выполняется до полного заполнения регистра адреса 7, который во время контроля работает в режиме счетчика . При этом во Все разряды накопителя 15 по всем нечетным адресам б 9056 7

Формула иэобретЕНИя, 60

65 записывается 0, а по всем четным .адресам — 1 . После полного заполнения регистра 7 адреса очередной сигнал с выхода генератора б импульсов устанавливает регистр

7 адреса в нулевое состояние, изменяя при этом на единицу состояние с четчи к а команд кон трол я 8 . Нов ому состоянию последнего соответствует возбуждение второго выхода двшифратора команд контроля, что соответствует формированию команды ™ ЧТЕНИЕ

С ЗАПИСЦО ОБРАТНОГО TEKEJIOIQ КОДА в блоке управлвния 4. По этой команде записанная в накопитель 15 при первом обходе адресов информация (тяжелый код) считывается и червэ . усилители воспроизведения lб и регистр числа 11 поступает в блок 17 анализа считанной контрольной инфор- мации 17. В последнем считаннаяинформация поразрядно сравнивавтсн на соответствие с эталонным сиГналом, который формируется в блоке анализа считанной кон.трольной информации 17 с помощью сигнала возбужденного выхода двшифратора команд контроля 9, сигнала младшего разряда регистра адреса 7 и сигнала с выхода блока управления 4. Если считанная с накопителя 15 информация соответствует записанной при первом обходе адресов, то по выбранному адресу производится запись обратного тяжелого кода. Такай операция производится последовательно по всем адресам., При этом во всв разряды накопйтеля 15 по всем нечетным адресам записываются 1, а по всем четным адресам - 0 . После полйого заполнения регистра адреса

7 последний Опять уст. навЛивается в нулевое состояние, а счетчик команд контроля 8 изменяет свое состояние на "единицу. Новому состоянию последнего соответствует возбуждение третьего выхода дешифратора команд контроля 9, что соответствует формированию команды ЧТЕНИЕ ОБРАТНОГО

ТЯЖЕЛОГО КОДА С ЗаПИСЬЮ НУЛЕИ в бло ке управления 4. Опять с помощью блока анализа..считанной контрольной информации 17 по всем адресам,производится йроверка сохранения информации записанной при втором обходе адресов.

После полного заполнения регистра адреса 7 последний устанавливается в нулевое состояние, а счетчик команд контроля 8 изменяет свое состояние на единицу. Новому состоянию последнего соответствует возбуждение последнего выхода дешифратора контроля 9,в результате чего триггер контроля 2 переключается в нулевое состояние и происходит останов управляемого генератора импульсов б с раэблокировкой блока 4 управления для приема внешних команд. Таков принцип работы ЗУ в режиме автономного контроля.

В случае же искажения записанной контрольной информации блок анализа читанной контрольной информации 17 вырабатывает сигнал сбоя, который поступает на нулевой установочный вход триггера неисправности 3 в результате чего управляемый генератор импульсов б прекращает свою работу, Происходит останов контроля по адресу, в котором обнаружен сбой контрольной информации. При этом блок индикации триггера контроля 18 указывает, что ЗУ находится в режиме контроля блок индикации триггера нвисправнос Ф ти 19 указывает на то, что в ЗУ.имеется неисправность| блок индикации .команд контроля 20 указывает коман- ; ду, которая выполяяпасы- блок индикации регистра числа 21 и блок

20 индикации регистра адреса 22 позволяют определить коды числа и адреса . соответственно в ьюмвнт останова контроля, т.е. помогают локализовать неисправность с точностью до разря25 да числа и адреса.

Запоминающее устройство.с автономным контролем, содержащее накопитель, одни входы которого соединены с соответствующими выходами разрядЗ5 ных Формирователей записи, а другивс соответствующими выходами двшифратора адреса, входы которого подключены к выходам регистра адреса, соединенными с входамй блока .индика4 ции Регистра адреса, пеРвый вход регистра адрес а йодключен к первому выходу блока управления, второй выход блока управления соединен с первым входом счетчика команд контроля, второй вход которого подключен

45 к соответствующему выходу регистра адреса, выходы накопителя .подключены к соответствующим входам усилителей воспроизведения, выходы кбторых соединены с соответствующими вхб50 дами регистра числа, первый вход ко торого соединен,с выходом элемента

ИЛИ, первые, выходы регистра числа соединены с соответствующими входами разрядных формирователей записи и блока ин,цик ции регистра числа, а вторые - с соответствующими входами блока анализа считанной контрольной информации, первый вход которого соединен с третьим выходом блока управления, второй вход — с соответствующим выходом регистра адреса, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия, ояо содержит гвяератор одиночных импульсов, генератор импуль6 9056 7

Составитель П.Луговцов

Техред И,Асталош Корректор О. Кови нская

Редактор Д,Зубов

Тираж 681 Подписное

IJHHHIIH Государственного комитета сссР по делам изобретений и открытий

113035, Иосква, Х-35, Раушская наб., д.4/5

Заказ 6796/61

Фили ал ППП Патент, r . Óæãîðîä, ул, Проектная, 4 сов, элемент И, триггер неисправности, триггер контроля, блок формирования контрольной информации, дешифратор команд контроля, блок индикации команд контроля, блок индикации триггера неисправности и триггер контроля, при этом выход триггера контроля соединен с первым входом элемента И, входом блока индикации триггера контроля и первым входом блока управления, первый выход триггера неисправности соединен со вторым входом элемента И и вторым входом блока управления, а второй выход — со входом блока индикации триггер а неисправности, выход элемента

И соединен со входом генератора импульсов,, выход которого подключен ко второму. входу регистра адреса, вход дешифратора команд контроля соединен с выходом счетчика команд контроля, один выход дешифратора команд контроля соединен с первым входом триггера контроля, а другие — с соответствующими входами блока упр вления, блока индикации команд контроля, блока формирования контрольной информации и блока анализа считанной контрольной информации, выход которого соединен с первым входом триггера неисправности, выход генератора одиночных импульсов соединен со вторыми входами триггера контроля и триггера неисправности, первый вход блока формирования контрольной информации соединен со вторым входом элемента ИЛИ, второй — со вторым входом регистра числа, Источники информации, прин ятые во внимание при эк спертиз е

1. Авторское свидетельство СССР

Р 329578, кл. G 11 С 29/00, 1972.

2. Авторское свидетельство СССР

20 Р 519767, кл. G 11 С 29/00, 1976.