"способ повышения помехоустойчивости цифровых интегрирующих вольтметров и устройство для его осуществления

Иллюстрации

Показать всеРеферат

И САНИ Е < цс))уцди) Союз Советски к

Социалистических .Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свил-ву (22) Заявлено 23,07.73(21) 1946536/18 21 с присоединением заявки,% 1947943/21 (51)М. Кл.

Я 01 R 19/2Е

G 01 R 13/02

Государственный квинтет

СССР оо делам нзобрвтвннй н открытой (23) Приоритет (53) УДК 621.317. .7 (088.8) Опубликовано 15.10.79. Бюллетень 14 38

Дата опубликования описания;>0 10 79 с:

Ю. B. Блинков, И. P. Добровинский, Е. А. Ломтев

A. И. Мартяшин и В. М. Шляндин .;,",:„ З;-,";, :;.:.,p (72) Авторы изобретения

Б3гс ь„ ЯЯ гу, Пензенский политехнический институт (73) Заявитель (54 СПОСОБ ПОВЫШЕНИЯ ПОМЕХОУСТОЙЧИВОСТИ

БИФРОВЫХ ИНТЕГРИРУЮЩИХ ВОЛЬТМЕТРОВ

И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ

1 изобретение касается электроприборостроения и может быть использовано в измерительной технике, автоматике и вычислительно и технике.

Известны способы повышения помехоустойчивости цифровых интегрирующих вольтметров и реализующие их устройства, основанные на подстройке задатчика интервала времени интегрирования под период помехи I 1).

° Недостатком устройств, реализующих указанный способ, являются ограничения, налагаемые на значение максимально допустимой для конкретного устройства амплитуды сигна15 лапомехи. Когда амплитуда помехипревышает значение измеряемого напряжения, интегратору для нормальной работы может потребоваться запас по выходному напряжению

U . Однако наличие такого запаса вЬ! х мокс часто получить сложно, к тому же в этом слу чае для полезного сигнала используется только часть характеристики интегратора, что приводит к потере чувствительности, Наиболее близким по технической сущности к предложенному является способ повышения помехоустойчивости цифровых интегрирующих вольтметров, позволяющий подавить полностью аддитивную периодическую помеху за счет выбора момента начала интегрирования в зависимости от соотношения времени интегрирования и периода помехи 121.

Белью изобретения является повышение максимально допустимого значения амплитуды помехи.

Это Достигается тем, что по предложенному способу повышения помехоустойчивости цифровых интегрирующих вольтметров, основанному на выборе момента начала измерения, при положительной полярности измеряемого напряжения интегрирование начинают при максимальных отрицательных значениях производной от напряжения помехи, а при отрицательной полярности измеряемого напряжения— при максимальных положительных значениях производной от напряжения помехи.

693 769

40 ля осуществления предложенного спооба может быть применено устройство, содержащее блок выделения напряжения помехи, задатчик времени измерения и последовательно соединенный с ним интег- 5 ратор, при этом входы блока выделения помехи и интегратора соединены со вхоgloM устройства.

В устройство для осуществления предложенного способа введены дифференцирующее устройство, инвертирующий усилитель-ограничитель и схема совпадения, выход которой соединен со входом задатчика, а входы - с выходами дифференцирующего устройства и выходом усилителяограничителя, вход которого соединен с входом устройства, при этом вход дифференцирующего устройства соединен с выходом блока выделения напряжения поме20

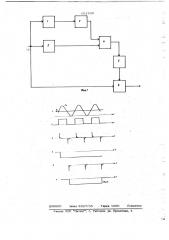

На фиг. 1 — приведена структурная схема устройства для осуществления предложенного способа; на фиг. 2 — временные диаграммы его работы.

Устройство содержит блок 1 выделения напряжения помехи, дифференцирующее устройство 2, инвертирующий усилитель-органичитель 3, определяющий полярность входного напряжения, схему совпа30 дения 4, задатчик 5 времени измерения и интегратор 6. Выход схемы совпадения

4 соединен с входом задатчика 5, а входы схемы совпадения 4 с выходами дифференцируюшего устройства 2 и выходом

35 усилителя-ограничителя 3, вход которого соединен с входом устройства, а выход дифференцирующего устройства соединен с .выходом блока выделения напряжения помехи.

Работает вольтметр следующим образом.

Измеряемое напряжение Ох вместе с аддитивной периодической помехой 0 q (фиг. 2а) подается параллельно на блок 1 выделения напряжения помехи, инвертирующий усилитель-ограничитель 3 и интегратор 6. Блок выделения напряжения помехи выделяет, усиливает и ограничивает сигнал помехи, на выходе его формируются сигналы прямоугольной формы (фиг. 2б).

Они дифференцируются дифференцирующим устройством 2 (фиг. 2в) и подаются на один вход схемы совпадения 4. Сигнал с выхода усилителя-ограничителя 3 подается на второй вход схемы совпадения 4.

При отрицательной полярности измеряемого напряжения сигнал на выходе инвертйрующего усилителя-ограничителя 3 совпапает с импульсами положительной полярности с выхода дифференцирующего устройства 2. При положительной полярности

0у на схеме совпадения 4 совпадает дифференцирующий импульс отрицательной полярности с выхода устройства 2 с отрицательным напряжением с выхода усилителя-ограничителя 3 (фиг. 2г). Импульсы. с выхода схемы совпадении 4 (фиг.

2д) определяют момент начала интегрирования, запускают задатчик времени измерения 5. Измеряемое напряжение с помехой интегрируются интегратором 6 (фиг. 2е).

При реализации предложенного способа получают значительное увеличение допустимой амплитуды напряжения поI мехи.

Формула изобретения

1. Способ повышения помехоустойчивости цифровых интегрирующих вольтметров, основанный на выборе момента начала измерения, отличающийся тем, что, с целью повышения максимально допустимого значения амплитуды помехи, при положительной полярности измеряемого напряжения интегрирование начинают при максимальных отрицательных значениях производной от напряжения помехи, а при отрицательной полярности измеряемого напряжения — при максимальных положительных значениях производной от напряжения помехи.

2. Устройство по п. 1, содержащее блок выделения напряжения помехи, задатчик времени измерения и последовательно соединенный с ним интегратор, при этом входы блока выделения помехи и интегратора соединены с входом устройства, о т л и ч а ю щ е е с я тем, что в него введены дифференцирующее устройство, инвертирующий усилитель-ограничитель и схема совпадения, выход которой соединен с входом задатчика, а входы — с выходами дифференцирующего устройства и выходом усилителя-ограничителя, вход которого соединен с входом устройства, при этом вход дифференциру.ющего устройства соединен с выходом блока выделения напряжения помехи.

Источники информации, принятые во внимание при экспертизе

1. Патент США И 3354453, кл. 340-347, 1967.

2. Авторское свидетельство СССР

% 339872, кл. G 01 R 19/26, 1969.