Канал прямого доступа к памяти электронной вычислительной машины (эвм)

Иллюстрации

Показать всеРеферат

Сеюз Сюеетсиня

Социалистических

Республик

К АВТОРСХОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. саид-ву (22)Заявлено 07.01.77 . (21) 2441680/18 — 24 (51)М. Кл.

6 06 F 3/04 с присоединением заявки РЙ

Государстввнний нювппвт

СССР нв делам нзвбретвннй н вткрытнй (23) Приоритет (53) УД К 681.327. .17 (088.8) Опубликовано 15.10.79. Бюллетень М 38

Дата опубликования описания 15.10.79 (72) Авторы изобретения

10, А. Круглов и А. Н. Пастухов (71) Заявитель (54) КАНАЛ ПРЯМОГО ДОСТУПА К ПАМЯТИ

ЭЛЕКТРОННОЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ

Изобретение относится к области вычисли-" тельной техники, а более конкретно к сйектро метрическим устройствам на базе ЭВМ и предназначено для. использования при работе ЭВМ в режиме статистического анализатора.

Известно устройство, содержащее входные преобразующие блоки, блоки передачи данных, узлы выбора адреса, память 11).

Недостатком известного устройства является невысокая пропускная способность.

Наиболее близким к да щому является уст- ройство, содержащее блок передачи данных и управляющих сигналов, блок управления, соединенные двухсторойней связью, блок формирования адреса памяти, память, первый и второй

fGHQpRT0pbI констант, причем первая группа информационных выходов блока передачи даиных и управляющих сигналов соединена с первой, группой входов блока формирования адреса памяти, первый и второй выходы блока управления соединены соответственно с управляющими входами блока формирования адреса памятй и памяти, группа выходов блока формирова-, ния адреса памяти соединена с группой адресных входов памяти (2).

Недостатком известного устройства является малое быстродействие, которое определяется последовательной .модификацией счетчиков устройства.

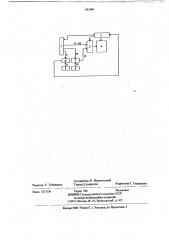

Белью изобретения является повышение пропускной способности. .Поставленная цель достигается тем, что канал содержит первый и второй сумматоры, причем вторая и третья группы информационных выходов блока передачи данных и управляющих сигналов соединены соответственно с первыми входами первого и второго сумматоров, вторые входы которых соединены соответственно с выходами первого и второго генераторов констант, группы выходов первого и второго сумматоров соединены соответственно с второй группой входов блока формирования адреса памяти и группой входов блока управления, На чертеже представлена блок-схема канала, который содержит блок 1 передачи данных и

691840

3 управляющих сигналов, блок управления 2, блок 3 формирования адреса памяти, память 4, генераторы констант 5, 6, сумматоры 7, 8, Блок 1 имеет и выходов цепей передачи данных, причем m старших разрядов указан- 5 ных цепей соединены с m входами первого сумматора 7, другие m входов которого соединены с m выходами первого генератора констант 5. Дополнительно k выходов старших разрядов цепей передачи данных блока 1 соединены с k входами второго сумматора 8, другие k входов которого соединены с k выходами второго генератора. констант 6. Младшие

n-m разрядов цепей передачи данных блока 1

-соединены с n-m входами младших разрядов блока 3, а m входов старших разрядов блока 3 соединяются с m выходами первого сумматора 7. Цепи управления блока 1 соединены с соответствующими входами и выходами блока управления 2, ко входу разрешения регистрации которого подключен выход переполнения второго сумматора 8. Выходы блока управления 2. соединены с соответствующими входами блока 3 и с паматью 4.

Канал работает следующим образом, 25

Код числа через блок 1 передается в блок формирования адреса памяти 3, причем m старших разрядов этого числа предварительно поступают на вход сумматора 7, где происходит сложение этих разрядов с константой, которая поступает на вход сумматора с первого генератора констант 5. После сложения код с выхода первого сумматора поступает на входы стар ших разрядов блока формирования адреса памяти 3. Таким образом, на входы блока форми- З рования адреса памяти 3 поступил код, отличающийся от кода, поступающего в блок 1 на величину константы А. Это позволяет выбрать начало зоны регистрации в любом месте. Одновременно с поступлением m старших разрядов кода на вход первого сумматора 7 k старших разрядов этого .эже кода поступают на вход второго сумматора 8, где складывается с константой В. Константа В определяет верхнюю границу зоны регистрации и образуется вторым генератором констант 6. Причем константа В представляет собой дополнительный код верхней границы зоны регистрации. Если поступающий на вход блока 1 код больше, чем код, определяющий верхнюю гранину зоны регистрации, то при сложении старших разрядов этоio кода с дополнительным кодом верхней границы зоны регистрации произойдет переполнение второго сумматора 8 и сигнал переполнения по шине управления регистрацией поступит на вход блока управления 2 и произойдет запрет регистрации данного кода. Это позволяет защитить участок памяти, лежащий выше верхней границы эоны регистрации. Если же поступающий код меньше константы В, то блок управления 2, не получив по шине управления регистрацией запрещающего сигнала, разрешает регистрацию кода, поступившего на входы бло ка 3.

Таким образом достигается выбор зоны для регистрации информации от входного преобразующего блока (на чертеже не показан).

Введение новых элементов позволяет выбирать любые участки памяти с заданной кратностью в любом месте памяти и защищать участки памяти,не используемые для регистрации, при этом время формирования адреса определяется быстродействием сумматоров, что определяет повышение пропускной способности канала.

Формула изобретения

Канал прямого доступа к памяти электронной вычислительной машины, содержащий блок передачи данных и управляющих сигналов, блок управления, соединенные двухсторонней связью, блок формирования адреса памяти, память, первый и второй генераторы констант, причем первая группа информационных выходов блока передачи данных и управляющих . сигналов соединена с первой группой входов блока формирования адреса памяти, первый и второй выходы блока управления соединены соответственно с управляющими входами блоica формирования адреса памяти и памяти, группа выходов блока формирования адреса памяти соединена с группой адресных входов памяти, отличающийся тем, что, с целью повышения пропускной способности, он содержит первый и вТорой сумматоры, причем втоpas и третья группы информационных выходов блока передачи данных и управляющих сигналов соединены соответственно с первыми входами первого и второго сумматоров, вторые входы которых соединены соответственно с выходами первого и второго генераторов кон- стант,группы выходов первого и второго сумматоров соединены соответственно со второй группой входов блока формирования адреса памяти и с группой входов блока управления.

Источники информации, принятые во внимание при экспертизе

1. Комплекс управляющий вычислительный

М-6000 (ТУ-25-01-7), 1974.

2. Авторское свидетельство СССР У 408308, кл. 6 06 F9/00,,1971 (прототип).

691840

Редактор Э. Губницкая

Заказ 6217/39

Филиал ППП Патент", г. Ужгород, ул. Проектная, 4

Составитель И. Милокостный

Техред Л.Алферова Корректор Т. Скворцова

Тираж 780 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5