Устройство для возведения в степень

Иллюстрации

Показать всеРеферат

Союз Соаетскнк

Соцнапнстнчесннх

Распубпнк 1Ц6 1

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (5 l ) М. Кд.

G 06 F 7/38 (22) Заявлено 06.04.77 (21) 2473849/18 — 24 с присоединением заявки М

Геоударотвевамй аонвтет

СССР ао долам пзобрвтеивй я откеатвй (23) П риоритет (53) УДК681.325 (088.8) Опубликовано 15.10 79. Бюллетень Рй 38

Дата опубликования описания 15.10.79

«»»»» пр 1;7,. 1 II % Ъ 3. т тт 1

В. Б. Дудыкевич и В. Н. Ма 4йович - " "- 1, 1: - -;--.,; „- т

1 (72) Авторы изобретения (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ВОЗВЕДЕНИЯ В СТЕПЕНЬ, Изобретение относится к области вычислительной техники и может быть использовано в цифровых и аналого-цифровых вычислитель-ных машинах, а также в измерительных функциональных преобразователях.

Известные устройства (1) возведения в степень отличаются большой сложностью, которая значительно возрастает при необходимости получения больших степеней, дробных или отрицательньтх степеней. Кроме того, известное устройство не обеспечивает возможность получения дробных и отрицательных степеней, Из известных устройств возведения в степень наиболее близким по технической сущ. ности к предложенному является устройство, содержащее делители частоты, генератор тактовой частоты, первую группу элементов И, потенциальные входы которых соединены с разрядными выходами счетчика и вторую труппу элементов И (2).

Однако и это устройство не имеет возможности. получения дробных и отрицательных степеней, что значительно снижает его функциональные возможности.

Цель изобретения — расширение класса ре,шаемых задач эа счет возможности возведения в дробную и отрицательную степень — достигается тем, что устройство содержит реве1тснвный счетчик, два элемента ИЛИ, ключ, триггер, первый и второй блоки вычитания, причем вход реверсивного счетчика соединен с выходом первого элемента ИЛИ, первый вход которого подключен к выходу первого делите. ля частоты, а второй вход соединен с выходом первого блока вычитания, один вход ко. торого подключен к выходу первого элемента ИЛИ, а другой вход — к выходам элементов И первой группы, импульсные входы которых и потенциальные входы элементов И второй группы соединены с разрядными выходамн реверсивного счетчика, импульсные входы элементов И второй группы соединены с разрядными выходами счетчика, а выходы — с первым..входом второго блока вычитания, второй вход которого и вход счетчика соединены с выходом второго элемента ИЛИ, первый вход которого соединен с выходом второго блока вычитания, а второй вход — с выходом вто1849 (6) (10) и прополучим (13) 45 (5) (6) (12 = (5 — f3 ° (13 (6 4 >

3 69 рого делителя частоты, вход которого и вход первого делителя частоты соединены с выходом ключа, первый и второй входы которого соединены соответственно с выходом генератора тактовой частоты и единичным выходом триггера, нулевой вход которого подключен к выходу счетчика.

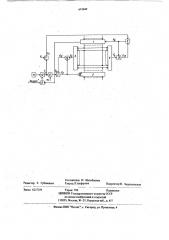

На чертеже представлена структурная схема устройства для возведения в степень.

Устройство содержит счетчик 1, реверсивный счетчик 2, первую 3 и вторую 4 группы элементов И, первый и второй элементы ИЛИ 5, 6, делители частоты 7, 8, триггер 9, ключ 10, генератор тактовой частоты 11, первый 12 и второй 13 блоки вычитания.

Работает устройство следующим образом.

При возведении числа в положительную степень (дробную) элементы устройства устанавливаются в следующие исходные состояния: триггер 9 находится в нулевом состоянии, .ключ 10 закрыт, в счетчик 1 записывается число Йп (число, которое нужно возвести в степень), в реверсивный счетчик 2 записывается число Nm (Йщ — коэффициент пересчета счетчиков 1 и 2), в делителях частоты устанавливаются коэффициенты деления k u m соответственно, а реверсивный счетчик 2 открыт по вычитающей шине управления.

При поступлении на единичный вход триггера 9 сигнала "Запуск",,открывается ключ

10 и импульсы генератора 11 с частотой следования fo поступают на входы делителей частоты 7 и 8. Частота следования импульсов на выходах делителей 7 и 8 определяется вы-, ражениями.

Х = . Ю

1 %

Частота импу71ьсов, поступающих с выходов элементов ИЛИ 5 и 6, определяется суммой частот, поступающих на их входы, (5 (11 (12 (Э)

fá (7 1 (13 (4) где f12 и 113 — частоты на выходах блоков

12 и 13 вычитания. Частоты на выходах блоков 12 и 13 определяются разностью частот, поступающих на их входы где f3 и f4 — частоты на выходах групп 3 и 4 элементов И. ..:Подставляя выражения (2) в (3), (1) в (4), а затем полученные выражения в (5) 1и (6) соответственно будем иметь о

42 М 42 Ъ о

44Э Г 4Э 4>

5 или

Х (9) Э !71 о (40)

Средняя частота f3 (t) следования импульсов на выходе группы 3, определяемая частотой импульсов, поступающих на вход счетчика 2, и числом N1(t), находящимся в счетчике 1, равна

Ю,(, н ((t)

3 14

Средняя частота f4(t) следования импульсов на выходе группы 4,определяемая частотой 1 импульсов, поступающих на вход счетчика 1, и числом N2 (t), находящимся в счетчике 2, равна

1 6 2(1

Ф N

Подставляя (11) в (9) и (12) в изведя очередные преобразования, ((т Ю, 5= „(+) т ((к

6 М (+) 4с (14)

Частота f5, поступающая на вход реверсивного счетчика 2 при работе его в вычитающем режиме, связана с числом N2(t), содержащимся в нем, выражением

35 с4 Й2(+)

d4

Частота f5, поступающая на вход счетчика 1, связана с числом N1(t), содержащимся в нем,, выражением

4О Д И, (+) < . (16)

c1t ь

Подставляя выражения (15) и (16) соответственно в (13) и (14), получим

Qg (4) Й Уо („.)

- -аЬ вЂ” - ((„(Ы т

Дй„(Ы 14п о ,(— NN (1%N (48)

Разделив уравнение (17) на уравнение (18), будем иметь

Ич,ы .

aNÄ (t т Ц ГЦ(((%

Разделив переменные в дифференциальном уравнении (19), получим

55 dNz(t 4 dNt(t( (20)

Время преобразования в устройстве начинается в момент подачи на единичный вход триг691849 гера 9 импульса "Запуск" и кончается в момент переполнения счетчика 1, При этом импульс переполнения счетчика 1 поступает на нулевой вход триггера 9, который закрывает ключ 10,и поступление импульсов генератора 5

11 на последующие схемы прекращается, За это время в суммирующем счетчике 1 число

N1(t) изменяется от йп до Ип1, а в реверсивном счетчике 2 число N (t) изменяется от йп, до М (Na — результирующее число, записанное в счетчике 2). Проинтегрировав выражение (20), подставив пределы изменения переменных, получим

I ни «> < г а и, г н 2 М „ откуда следовательно н„=и (ф (24) З0

Иэ уравнения (24) видно, что предложенное устройство для возведения в степень. обеспечивает возведение в дробную положительную степень числа йп, предварительно записанного в 35 счетчик 1. При возведении числа в отрицательную степень (дробную) требуются следующие изменения в исходных состояниях элементов устройства. в реверсивный счетчик 2 записывается число 1, а управление его происходит по 40 суммирующей шине управления.

Выражение (15) примет вид

d и 2(И . (Z<)

Дифференциальное уравнение (20) изменится 45 следующим образом . (+)

2 — — (гь)

Проинтегрировав выражение (26) с учетом новых пределов изменения переменных, получим:

4 дй <М g a 4(+ 1 С27)

MH 55 или

2 т1 4 ((22) 20 или, произведя необходимые преобразования

-К (281

Таким образом, предложенное устройство поэво ляет получить дробные и отрицательные стенени, что значительно расширяет его функциональные возможности.

Формула изобретения

Устройство для возведения в степень, содержащее делители частоты, генератор тактовой частоты, первую группу элементов И, потен- - -циальные входы которых соединены с разрядными выходами счетчика и вторую группу элементов И, отличающееся тем, что, с целью расширения класса решаемых задач за счет воэможности возведения в дробную и отрицательную степени„оно содержит реверсивный счетчик, два элемента ИЛИ, ключ, триггер, первый и второй блоки вычитания, причем вход реверсивного счетчика соединен с выходом первого элемента ИЛИ, первый вход которого подключен к выходу первого делителя частоты, а второй вход — соединен с выходом первого блока вычитания, один вход которого подключен к выходу первого элемента ИЛИ, а другой вход — к выходам элементов И первой группы, импульсные входы которых и потенциальные входы элементов И второй группы соединены с разрядными выходами реверсивного счетчика, импульсные входы элементов И второй группы соединены с разрядными выходами счетчика, а выходы — с первым входом второго блока вычитания, второй вход которого и вход счет пгка соединены с выходом второго элемента ИЛИ, первый вход которого соединен с выходом второго блока вычитания, а второй вход — с выходом второго делителя частоты, вход которого и вход первого делителя частоты соединены с ,выходом ключа, первый и второй входы кото рого соединены соответственно с выходом генератора тактовой частоты единичным выходом триггера, нулевой вход которого подключен к выходу счетчика.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР N 425175, KJI. 6 06 F 7/38, 1972.

2, Данчеев В. П. Цифро-частотные вычисли-. тельные устройства, М., "Энергия",,1976, с. 49, рис. 2 — 10.

691849

Редактор Э. Губницкая

Заказ 6217/39

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4

Составитель Н, Шелобанова

Техред Л.Алферова КорректорН. Задерновская

Тираж 780 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открьггий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5