Накапливающий сумматор

Иллюстрации

Показать всеРеферат

О Il И С А Н И Е п, я.с11щр

ИЗОБРЕТЕНИЯ К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советски к

Социалистических

Рес ублик (61) Дополнительное к авт. сеид-ву (51)M. Кл.

G 06 F 7/50 (22) Заявлено 21.0ь,76 (21) 2374864/18 — 24 с присоединением заявки ¹

Гаеударствениьй квветвт

СССР в делам извбрвтвний и вткрытей (23) Приоритет

Опубликовано 15 10.79. Бтоллетень № 38 (53) УДК681325 5 (088.8) .Дата опубликования описания 15.10.79 (72) Авторы изобретения

В, И. Черницкий и В. A. Золо (71) Заявитель (54) НАКАЛДИВАН)ЩИЙ СУММАТОР!

Изобретение относится к области цифровой вычислительной техники и может быть использовано при проектировании электронных цифровых вычислительных машин.

Известен накапливающий сумматор параллельного действия для суммирования двоичных чисел, состоящий иэ i групп н содержащий в каждой i-ой группе счетные триггеры, логический преобразователь и элементы задержки fl), Наиболее близким техническим решением к данному является накапливающий сумматор, содержащий в каждом разряде счетные триггеры и элементы ИЛИ (21. В таком сумматоре процесс суммирования складывается иэ нескольких последовательных операций: 1) сум-, мирования по модулю два, при котором происходит изменение состояний триггеров, на счетные входы которых поступили единичные, сигналы; 2) задержки единиц переноса с помощью элементов задержки для того,, чтобы закончились переходные процессы в трйггерах при изменении их состояний; 3) переноса единиц в старшие разряды; 4) изменения состояний трттггеров, на счетный вход которых поступили единичные сигналы переноса. Время суммирования лри этом определяется длительностью фронта переброса триггера, временем задержки единицы переноса элементом задержки и временем задержки единицы переноса логическими элементами при сквозном переносе ее в

) старшие разряды.

Существенным недостатком такого сумматора является его низкое быстродействие иэ-за невозможности совмещения операции суммирования и переноса едтптицы в старшие разряды, Целью изобретения является увеличение быстродействия сумматора.

Это достигается тем, что в накапливающий сумматор, содержащий и счетных триггеров (n — число разрядов сумматора) и элементов ИЛИ, выходы которых подключены к входам соответствующих триггеров, дополнительно введены дешифратор и (2" — 1) узлов группового переноса, причем входные шины сумматора подключены ко входам дешифратора, выходы которого подключены к разрядным входам узлов группового переноса, другие входы

Qi1=xi соответствующий выход х; дешифратора 1, подключается непосредственно ко входу элемента

ИЛИ 3 j-ro разряда. Выполнение различных функций Q;j одного и того же j-го разряда

5 может быть, вообще говоря, упрощено, что и сделано при реализации трехразрядного накапливающего сумматора (фиг. 2), функциональная схема которого построена в полном

1 ,соответствии с приведенными функциями воз10 буждения. В процессе функционирования этого сумматора трехразрядное двоичное число поступает на входы а1, аг, аз дешифратора 1, при этом возбуждается один из его выходов х> — х2, а следовательно, к содержимому

t5 сумматора прибавляется соответствующее число.

Рассмотрим работу сумматора на конкретном примере. Пусть на обнуленный сумматор поступило число 2 (010), при этом с выхода дешифратора хг сигнал поступит только на

20 триггер 2 второго разряда через соответствующий элемент ИЛИ 3, На триггер 2 третьего разряда GHlHRJI поступить не может, так как элемент И 6, на который поступает сигнал с хг, не пропускает сигнала из-за того, что триггер 2 второго разряда находился в нулевом состоянии. В сумматор записывается число 010. Если же на вход снова поступит число, например, 3 (011), с выхода дешифратоЗо> ра сигнал х3 через элемент ИЛИ 7 поступит на счетный вход триггера 2 первого разряда.

Так как триггер 2 первого разряда находился в нулевом состоянии, сигнал хз через элементы ИЛИ 7 и И 6 поступит на счетный вход триггера 2 второго разряда. Так как триггер 2 второго разряда первоначально на. ходился в единичноь состоянии, на логическом элементе И 6 произойдет совпадение сигналов с единичного выхода триггера 2 второго разряда и сигнала хз, поступившего через элемент ИЛИ 7, и на счетный вход триггера 2 третьего разряда также поступит сигнал. Таким образом, все триггеры изменят свое состояние, и в сумматоре запишется число 5 (101), 45 что соответствует сумме 2 + 3. Аналогично сумматор работает при подаче на вход дешифратора 1 следующего двоичного трехразрядного числа, Выходом сумматора являются клеммы А1 Аг Аз ° и =2" +2q, которых соединены с выходами счетных триггеров предыдущих разрядов, а выходы соединены со входами элементов ИЛИ соответствующих разрядов.

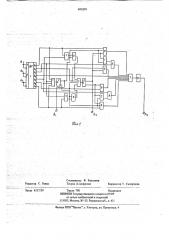

На фиг. 1 изображена функциональная схем накапливающего сумматора; на фиг. 2 показана функциональная схема трехразрядного на., капливающего сумматора (п=3) с реализацией узлов группового переноса на элементах И и ЙЛИ.

Накапливающий сумматор содержит дешифратор 1, счетные триггеры 2, элементы ИЛИ 3 а также (2" — 1) узлов группового переноса (на фиг. 1 показаны разрядные группы первого узла 4 группового переноса и (2"-1)-ro узла 5 группового переноса).

Принцип действия сумматора рассмотрим на примере трехразрядного накапливающего сумматора (фиг. 2), Выходные, шины сумматора а1, аг, аз подключены ко входам дешифратора 1, выходы которого подключены ко входам семи узлов группового переноса, реализованных на элемен тах И 6 и ИЛИ 7. Данные логические элементы соединены в соответствии с функциями возбуждения счетных триггеров 2 каждого разряда сумматора. В частности, при прибавлении единицы к содержимому сумматора функции возбуждения триггеров имеют вид

011 — х1 01г — х1 Т1 01з = х1Т1 Т2 где Т1 и Тг — выходные сигналы счетных триг геров 2 первого и второго разрядов сумматора, О» — функция возбуждения j-ro триггера 2 при прибавлении к содержимоьгу сумматора единицы, х1 — сигнал на первом выходе дешифратора 1.

При прибавлении к содержимому сумматора двух функции возбуждения триггеров 2 имеют вид

О

021 = 0 022 = X2 023 = X2T2

При прибавлении к содержимому сумматора трех, четырех, пяти, шести и семи функции возбуждения триггеров 2 имеют вид

Оз1 = хз Озг = хзТ1 О,з = хз(Т11Т2

0.1 1=0 0.2 2=0 01з = х1

Оз1 = хз Озг = хзТ1 Озз = хз (TtvT2) 50

Q 1 = 0 . С42 = хь Оьз = х6Т2

021 = x2 022 = хгТ1 02з = x2T1T2

Можно заметить, что выполнение разрядных групп узлов группового переноса в каждом конкретном случае может быть упрощено. На пример, при значении О» = О, соответствуюtuas J-ая разрядная группа i-ro узла группово"го переноса вообще отсутствует. При значении

В и-разрядном сумматоре соблюдается следующая закономерность соединения его элементов. Счетный вход каждого триггера 2 соединен с выходом элемента ИЛИ 3. Входы каждого элемента ИЛИ 3 соединены с выходными каналами дешифратора 1, номера которых определяются соотношением

691850 где k — номер разряда сумматора, к которому относится элемент ИЛИ 3; q О, 1, 2...

Так со входом элемента ИЛИ 3 первого разряда соединяются выходы дешифратора 1 с номерами 1, 1 + 2х1, 1 + 2х2,..., то есть 5 . ace нечетные выходы дешифратора, При k=2 и = 2, 6, 10, 14,..., Кроме того, входы каждого элемента ИЛИ 3 (исключая элемент ИЛИ 3 первого разряда) соединены с выхода 2 узяв rpyrmosoro переноса, где 1О

Р— номер разряда сумматора. Входы каждо-го узла группового переноса соединены с выходами триггеров 2 предыдущих разрядов и выходами дешифратора 1.

Учитывая, что в дешифраторе сигнал задерживается на одном логическом элементе (weменты включены параллельно), а узел группового переноса содержит не более двух последовательно включенных логических элементов, 20 общее время одного цикла суммирования складывается из времени задержки сигнала на четырех последовательно включенных логических элементах и времени переходы триггера в противоположное состояние.

Таким образом, быстродействие данного сумматора значительно выше быстродействия известных накапливающих сумматоров, и время суммирования Не зависит от числа разрядов сумматора, что дает возможность для примепения данного сумматора в современных вычислительных устройствах, Формула изобретения

Накапливающий сумматор, содержащий n . счетных триггеров (n — число разрядов сумматора), и элементов ИЛИ, выходы которых подключены к входам соответствующих триггеров, отличающийся тем,что, с целью увеличения быстродействия, сумматор дополнительно содержит дешифратор и (2" — 1) узлов группового переноса, причем входные шины сумматора подключены ко входам дешифратора, выходы которого подключены к разрядным входам узлов группового переноса, другие входы которых соединены с выходами счетных триггеров предыдущих разрядов, а выходы соединены со входами элементов ИЛИ соответствующих разрядов.

Источники информации, принятые во внимание при экспертизе

1, Авторское свидетельство СССР Р 482739, кл. G 06 F 7/385, 1973, 2. Анисимов Б. В. и др. Основы теории и проектирования ЭЦВМ. М., "Высшая школа", 1970, с. 291 — 292 (прототип).

691850

Фиг.8

Корректор Т. Скворцова

Редактор С. Равва

Заказ 6217/39

Составитель В. Березкин

Техред Л.Алферова

Тираж 780 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий.113035, Москва, Ж вЂ” 35, Раушская наб,, д. 4/5

Филиал ППП Патент", г, Ужгород, ул. Проектная, 4