Процессор

Иллюстрации

Показать всеРеферат

(72) Авторы изобретения

А. П. Кондратьев и М. А. Беляева (73) Заявитель! ф11

) (54) HPOUECCOV

Изобретение относится к области вычислительной техники и может быть ис пользовано в ЭВМ, в частности в том случае„когда время выработки основной памяти больше времени выборки запоми5 нающего устройства для хранения ключей защиты основной памяти, и эти памяти реализованы в виде нескольких блоков и конструктивно расположены отдельно от пентрального обрабатывающего устройства.

Известны ЭВМ, у которых осуществляется запита основной памяти по ключу

E >1C>1 . Процессоры содержат обычно . память ключей защиты, в которой хранится специальная информация - ключи блоков основной памяти, с помощью которых осуществляется защита основной памяти от несанкционированногодоступа и оши.бочного изменения ее содержимого.

Наиболее близким техническим решением к данному изобретению является пропессор,которыйсодержитцентральное обрабатывающее устройство, f3 блоков оперативной памяти с регистрами считы вания, и блоков памяти ключей защиты, блок сопряжения и управления памятью состоящий из регистра данных, выходы которого подключены в информационным входам центрального обрабатывающего устройства, увел управления оператив ной памятью, выходы которого подключены к управляющим входам блоков оперативной памяти и памяти ключей защиты, из схемы сравнения ключей, к одному из входов которого подключен регистр ключа защиты, а выход ее подключен к центральному обрабатывающе- . му устройству f 31;

Недостаток этого пропессора в том, что память ключей защиты имеет свои отдельные интерфейсы (шины считывания и записи) и регистр данных, а также

1 в сложной схеме приема в регистр данных основной памяти, так как необходимо обеспечить выбор информации из того блока оперативной памяти, к которому

3 691 было обращение. Кроме того прн организации многомашинной системы с общим полем памяти в каждом процессоре нужно предусматривать дополнительную аппаратуру для наращивания памяти ключей на величину, соответствующую увеличению объема общей памяти и дополнительную коммутацию или перемонтаж при изменении объема общей памяти. целью настоящего изобретения яв- 10 ляется сокращение оборудования., Указанная цель достцгается тем, что в процессор введены группы элементов

ИЛИ, причем первый и второй входы элементов ИЛИ первой группы подключены к первой группе инфбрмационных выходов регистров считывания, первые и вторые входы элементов ИЛИ второй и третьей групп подключены к второй группе информационных выходов регистров считывания и выходам памяти ключей зашиты соответственно, первые и вторые входы элементов ИЛИ четвертой группы подключены к выходам элем е нтов И ЛИ второй и третьей групп соответственно, 25 выходы элементов ИЛИ четвертой группы подключены к второй группе информационных разряд6в регистра данных и к первому входу схемы сравнения ключей

30 зашиты, выходы элементов ИЛИ первой группы подключены к первой группе информационных разрядов регистра данных, первый выход центрального обрабатывающего устройства (UOY) подключен к входу регистра данных, третий выход

= -==-.UOV подключен к адресным входам блоков опреативной памяти и блоков памяти ключей зашиты, второй выход ПОУ подключен к входу узла управления, ïåðвый выход которого подключен к управляющим входам блоков оперативной памяти и блоков памяти ключей защиты, а также к управляющим входам регистров считывания, второй выход узла управления подключен к управляющим входам блоков памяти ключей защиты и блоков оперативной памяти.

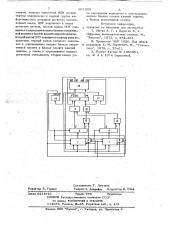

На чертеже изображена блок-схема процессора. 50

Выходы блоков 1 оперативной памяти подключены к входам регистров 2 считывания, а каждый из К выходов 3 регистра считывания каждого блока опера-. тивной памяти подключен через один из; элементов ИЛИ 4 первой группы к соответствующим входам регистра 5 данных.

К выходов 6 регистра данных подключены

ia информационным входам блоков 1. Каж859 4 дый из Е выходов 7 регистра считывания каждого блока 1 подключен к одному из входов L элементав ИЛИ 8 второй группы, к другому входу которых подключен один из информационных выходов блоков 9 памяти ключей защиты.

Выходы всех элементов ИЛИ 8 второй группы подключены через группу элементов ИЛИ 10 к соответствующим Р младшим разрядам регистра данных и к входам схемы 11 сравнения, к остальным входам которой подключены выходы центрального обрабатывающего устройства (ЦОУ) 13. Выход схемы 11 сравнения подключен к БОУ 13, Ч выходов

14 младших разрядов регистра данных подключены к информационным входам блоков 1 и 9. Выход 15 регистра данных подключен к UOY 13. Выход 16 подключен к узлу управления 17, выход 18 чтение. которого подключен к входам установки в ноль регистров считывания и также, как и выходы 19 (один запись, другой — "тип памяти ) подключены к соответствующим" управляющим входам всех блоков 1 и 9. Все выходы 20

ЦОУ 13 подключены к адресным входам всех блоков 1, а старшая часть выходов

20 ЦОУ 13 подключена к адресным входам блока 9. Информационные выходы 21

ЦОУ 13 подключены к входам регистра

5 данных.

В предлагаемом процессоре основная память может наращиваться блоками.

Каждый блок 1 оперативной памяти содер«, жит соогветствующий ему по объему блок 9 памяти ключей защиты, что исклю» чает проблемы, связанные с приведением в соответствие объема основной памяти и памяти ключей защиты при создании многомашинной системы с общим полем памяти. Так как быстродействие памяти ключей защиты выше,чем оперативной памяти, используется общий интерфейс (шины считывания, записи, адреса) для основной памяти и памяти ключей защиты (ПКЗ). При обращении к блоку 1

UOY 13 выдается адрес с выхода 20 и через узел 17 управления в блок 1 выдаются управляющие сигналы чтение и тип памяти . Сигнал чтение сбрасывает регистры 2 считывания всех блоков 1 и запускает один из блоков 1 и 9.

В нашем примере время цикла блока 9 принято в 4 раза меныие, чем время цикла основной памяти, поэтому информация

as ПКЗ появляется в первом такте с момента обращения к основной памяти, а

691859 6 данных, так как в противном случае вместо элементов ИЛИ 4, 10 и 8 нужны были бы более сложные схемы селекторов.

Все это ведет к сокращению оборудования процессора, Кроме того при органнаации многомашинной системы с обшим полем памяти не нужно в каждой ЭВМ предусматривать дополнительную аппаратуру для нарашивания памяти ключей зашиты на величину, соответствуюшую увеличению объема общей памяти, и дополнительную коммутацию или перемонтаж при изменении объема общей памяти.

Процессор, содержаший и блоков оперативной памяти, 12 блоков памяти ключей зашиты, 1 1 регистров считывания информации из оперативной памяти, регистр данных, схему сравнения ключей защиты, узел управления, централь25 ное обрабатываюшее устройство (UO5 ), первый вход которого соединен с первым выходом регистра данных, второй вход

БОУ подключен к выходу схемы сравне30 ния ключей защиты, информационные выходы блоков оперативной памяти подключены к входам соответствуюших регистров считывания, второй информационный выход регистра данных подключен к входам и блоков оперативной памяти, а

35 третий информационный выход подключен к входам блоков памяти ключей аашиты и входам блоков оперативной памяти, четвертый выход ЦОУ подключен

4О к второму входу схемы сравнения ключей зашиты, о т л и ч а ю ш и и с я тем, что, с целью сокращения оборудования, в него введены группы элементов ИЛИ, причем первый и второй вхо45 ды элементов ИЛИ первой группы подключены к первой группе информационных регистров считывания, первые и вторые входы элементов ИЛИ второй и третьей групп подключены к второй группе информационных выходов регистров считывания и выходам памяти ключей ,аашить соответственно, первый и вторые входы элементов ИЛИ четвертой группы подключены к выходам элементов ИЛИ второй и третьей, групп соответственно, выходы элементов ИЛИ четвертой группы подключены к второй группе информационных разрядов регистра данных и к первому входу схемы сравнейия ключей

ha блока оперативной памяти — в кбнце второго такта, Поэтому наложение информации из блока 9 и блока 1, посту паюшей по одним и тем же шинам ис1 ключено. Данные, представляюшие собой ключ памяти, иа блока 9 через группу элементов ИЛИ 8, 10 в регистр 5 дан ных не принимаются, а поступают на второй вход схемы 11 сравнения. И если этот ключ не равен ключу защиты программы, то с выхода схемы сравнения выдается сигнал, поступающий в НОУ 13 и вызывающий прерывание в процессоре.

Информация одного блока 1 памяти, запушенного при данном обращении череа группы элементов ИЛИ 4, 8 и 10 поступает на соответствуюшие входы регистра 5 данных и принимается в него в конце такта. В такте записи (регенерации) из UOT 13 через узел 17 управления выдается сигнал запись" и признак "память ОП", и производится запись информации из регистра 5 данных в блок

1, к которому было обращение при чтении.

Существуют также специальные команды, выполняющие запись и чтение данных из памяти ключей в ЦОУ 13. При чтении .ключа памяти ПОУ 13 череа уаел 17 управления выдается сигнал чтение по выходу 18 и признак память ключей по выходу 19. Сигнал чтение" на выходе 18 сбрасывает регистры 2 считывания, данные из соответствуюшего блока 9 через группы элементов ИЛИ 8 и

10 поступают в младших разрядов реI гистра 5 данных, а из регистра данных передаются в ЦОУ 13, При выполнении команды записи клю-. ° ча памяти из UOY 13 по выходам 19 выдается сигнал запись" и признак

"память ключей . Ключ памяти иа ЦОУ

13, переданный в предыдущем такте в младшие разряды геристра 5 данных,,в следующем такте из регистра данных записывается в блок 9.

При использовании предлагаемого изобретения отпадает необходимость в отдельном интерфейсе и регистре данных для памяти ключей зашиты, упрощается выполнение команд чтения и записи ключа памяти 1упрошаются микропрограммы этих команд). Наличие сбора регистров считывания при каждом обрашении к основной памяти исключает наложение информации от рааличных блоков памяти, так как запускается только выбранный блок памяти, что упрощает реализацию схемы приема информации в регистр

Формула иаобрете í ия

Составитель Т. Ламаина

Техред О. Андрейко Корректор Н. Стец

Редактор Б. Герцен

Заказ 6218/40 Тираж 780 Подписное

UHHHffH Государственного комитета СССР по делам иаобретений и открытий

113035, Москва, Ж-35, Рауаская наб., д. 4/5

Филиал ППП "Патент, r. Ужгород, ул. Проектная 4

7 691 нашиты, выходы элементов ИЛИ первой группы подключены к первой группе информацио :нь х разрядов регистра данных, первый выход ЦОУ подключен к входу регистра данных, третий выход ЦОУ подключен к адресным входам. блоков оперативной памяти и блоков памяти ключей зашиты, второй выход ПОУ подключен к входу узла управления, первый выход которого подключен к управляющим входам блоков опера- 10 тивной памяти и блоков памяти ключей нашиты, а также к управляющим входам регистров считывания, второй выход увла управления подключен к управляюшим входам блоков памяти ключей нашиты и блоков оперативной памяти.

Источники информации, принятые во внимание при экспертиае

1. Шигин A. Г. и Дерюгин A. A. цифровые вычислительные машины. М., "Энергия, 1 97 5, с. 4 82-484.

2. Процессор ЭВМ 1020. Под общей редакцией A. М. Ларионова, М, Статистика", 1975, с. 57-61.

3. Патент А нглии % 1 05695 1, кл. 4 4 А 1974 (прототип).