Цифровое интегрирующее устройство

Иллюстрации

Показать всеРеферат

(72) Авторы изобретения (71) Заявитель (54) ЦИФРОВОЕ ИНТЕГРИРУЮШЕЕ УСТРОЙСТВО

1...,; -,::;. --::-... ::;:, . -:-:::::;-:: -::; ;.:: ..-. 2

Изобретение относится к вычислитель-:,:- .-ggMg блока сравнения кодов, вторые вхоной технике и может быть использовано " ды бпокй сравнениМ кодов подключены к в цифровых сглаживающих и преобразую - " ..,шине кода Опорного уровйя, а выкод соеших системах. . динен "с йерййми Входами элементов И, Известны интегрирующие устройства . . выходы которых подключень1 ко входам.

f1), содержащие интегрирующие и сум- -:,накопитем, входь| цифрового интегратомируюшие усилители, ключи цифроана- : pa саединейы, с" входами элементов ИЛИ

) логовый преобразователь и двоичный счеФ- : гРУппй чик, в которых интегрирующие усилители, - "- He4ociamox о У р

6с4 атком этого чстоойства явля- работают поочередно, что позволяет по-:: -. ется невоййожность у р ся ево Можность и авления динамилучить достаточно широкий динамическйй ческим диайазОнрм р и, диапазон интегрирования. Недостаток .-:: . poeeH i чтФ ухуд ования что : дшабт точность интегритакого устройства состоит в том, что .. рования при зада но р р п и з анной аз ядности счетпри заданной разрядности цифроаналогов - чика или Интегратора. го преобразователя точность интегрирова» Целью .изобрет ни р р елью изо етения является оасшиовния и динамический диапазон опредеЛяют нне динамического диапазона и повышеся ценой младшего разряда и не могут ние точности работы устройства при заменяться в процессе интегрирования, что данной разрядности. . сужает область ego применения; Поставленная цель достигается за счет

Наиболее близким техническим реше- то1о, что в предлагаемое цифровое интегнием к данному изобретению является рирующее устройство введены вычитаюший устройство(21, содержащее датчик управ блок, две группы коммутаторов, допоаниляюшего кода, цифровой интегратор, вы- тельная группа элементов ИЛИ и инверходы которого соединены с первыми вхо- торы, причем первая группа вычитаю/

IS

® таторов 11 и наличием инв"ерторов 10.

: При приближении накопленного сигнала к заданной Йеличйне, определяемой датчиКоМ управляющего кода 6, разность на выходе вычитающего блока уменьшается, Это приводит к,такой настройке коммутаторов 8, что сдвиг уменьшается (в предельном случае до О), а сдвиг, выходных сигналов интегратора 1 за счет коммутаторов 12 увеличивается (в предельном случае до максимума, обесцечиЗ . вая направление старшего разряда интегратора 1 в младщий разряд накопителя

4). Таким обраэом, при приближении к заданной границе чувствительность интегратора 1 повышается, т. е. устройство работает о максимальной точностью, тогда как i начале работы за счет сдвига (масштабирования) входного сигнала устройство работает с невысокой точностью, но с более высоким быстродействием за счет редкого использования операций пересылки в накопитель. Такой ре55 з 69 щего блока соединена с датчиком управляющего кода, вторая группа вычитающего блока подключена к выходам накопителя, а выходы вычитающегo блока соединены с управляющими входами коммутаторов первой группы и через инверторы — с управляющими входами коммутаторов второй группы, информационные входы коммутаторов второй группы подключечены к информационным шинам устройст= ва, выходы соединены со входами элементов ИЛИ группы, информационные входы

"коммутаторов первой группы соединены с выходами интегратора, а выходы коммутаторов первой группы через элементы ИЛИ дополнительной группы подключены ко вторым входам элементов И.

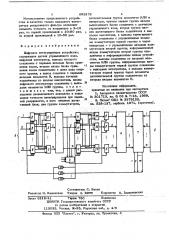

На чертеже показана схема предлагаемого устройства.

Устройство содержит цифровой интегратор 1, группу элементов ИЛИ 2, блок сравнения кодов 3, накопитель 4, элемен- ты И 8, датчик управляющего кода 6, вычитающий блок 7, первую группу коммутаторов 8, входную информационную шину 9, инверторы 10, вropyIO группу коммутаторов 11, дополнительную группу элементов ИЛИ 12.

Устройство работает следующим обра зом.

Входной сигнал поступает íà hxoii цифройого интегратора 1 через жоследовательно включенные группу коммутаторов

8 и группу элементов ИЛИ 2. При"этом, в зависимости от настройки коммутато-, 0 ров 8, каждый из rl входных разрядов информационной шины 9 может быть подключен к любому входу цифрового"ин гег"- ратора 1. Благодаря параллельному включению управляющих аходов всех коммутаторов 8, вс Р разряды информационной шины 8 смещаются одинаково при прохождении коммутаторов, что обеспечивает сдвиг разрядов при поступлении на входы цифрового интегратора 1. Такой сдвиг фактически означает управление масштабом интегрирования. Выходной сигнал с вькодов интегратора 1 также сдвигается аналогичной цепочкой коммутаторов

11 и элементов ИЛИ 12 и поступает на входы накопителя 4 через элементы И

8, которые открываются в случае сраба- тывания блока сравнения кодов 3. Этот блок настраивается кодом опорного уровня на сигнал интегратора 1, близкий к ,его верхней границе.

Каждый раз при достижении сигналом интегратора 1 опорного уровня в накопи1878 4 тель 4 засылается результат интегрирования, равный опорному уровню. Таким образом, при засылке результата интег« рирования в накопитель 4 целесообразно использовать только те выходные разряды интегратора 1, к которым в данном случае чувствителен блок сравнения кодов

3, т. е. разряды, определяющие опорный уровень. Сброс интегратора осуществляется при этом автоматически по разрядам опорного уровня. Перед засылкой в накопитель 4 производят целенаправленное смешение (масштабирование) результатов интегрирования. При этом смещейие разрядов происходит в направлении, обратйбм направлению смещения (сдвига) входных разрядов информационной шины 9, что обусловлено параллельным подключением управляющих входов коммуУцравленйе сдвигом разрядоц осуществляется вычитающим блоком 7, производящим анализ,накопленного результата. жим работы наиболее эффективен для боль. шинства случаев применения устройств такого типа. Сдвиг, выходных разрядов интегратора 1 необходим для выравнивания масштабов при засылке результата в накопитель 4.

Эффективность предложенного устройства проверена для случая его использования в цифровых рекурсивных фильтрах, состоящих иэ последовательно включенных цифровых чнтеграторов.

5 6918

Использование предложенного устройства в качестве только выходного интегратора рекурсивного фильтра позволяет повысить точность по координате в 3-10 раз, по первой производной в 10-80 раэ, по второй производной в 10-50 раз. с

Формула изобретения

1Î

Цифровое интегрирующее устройство, содержащее датчик управляющего кода, цифровой интегратор, выходы которого соединены с первыми входами блока сравнения кодов, вторые входы блока срэ нения кодов подключены к шине кода опорного уровня, а выход соединен с первыми . входами элементов И, выходы которьрс подключены ко аходам накопителя, входй цифрового интегратора соединены с выхо- >О дами элементов ИЛИ группы, о т л и -. ч а ю ш е е с я тем, что, с целью расширения динамического диапазона и повышения точности интегрирования при заданной разрядности, s него введены вычи-. таюший блок, две группы коммутаторов

78 6 дополнительная группа элементов ИЛИ и. инверторы, причем первая группа входов вычитающего блока соединена с датчиком управляющего кода, вторая группа входов вычитающего блока подключена к выходам накопителя, а выходы вычитаюшего блока соединены с управляющими входами коммутаторов первой группы и через инверторы - с управляющими входами коммутаторов второй группы, информационные входы коммутаторов второй группы подключены к информационным шинам устройства, выходы соединены.со входами элементов ИЛИ группы, информационные ахо-, ды коммутаторов первой группы соединены с выходами интегратора, а выходы коммутаторов первой"группы через элементы дополнительной группы подключены ко вторым входам элементов И, Источники информации, принятые во виийанйв при экспертизе

1. Авторское свидетельство СССР

Ь 301713, кл. 4 06 9 7/18, 1969е

2. Патент СЙА l4 3579128, кл. 328-12 7, опублик. 1971, (прототип).

Составитель С. Белан

Редактор, H. Каменская Тахред 3, Фанта Корректор Н, Задерновская

Заказ 8219/41 Тираж 780 Подписное

ЦНИИПИ Государственного комИтета СССР по делам изобретений и открытий, 113035, Москва, Ж-35> Раушская наб., д. 4/5

Филиал ППП "Патент, r. Ужгород, ул. Проектная, 4