Источник питания постоянного напряжения

Иллюстрации

Показать всеРеферат

(ill 692025

Союз Советских

Социалистических

Республик

-лам н и е

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свил-ву (22) Заявлено11.07.77 (21) 509106/о4 07 с присоединением заявки J% (23) Приоритет

Опубликовано 15.10,79. Бюллетень нв е

Дата опубликования описания 18,1р 79 (51) M. Кл.

Н 02 М 3/135

G 05 F 1/56

Гесударственний нем«тат

СССР на делам «забрвтвннй н еткрь тнй (53) УЛK 621.314..57(088.8) -{72) Авторы изобретения

В. А. Белов я А. И. Яцков (71) Заявитель (54) ИСТОЧНИК ПИТАНИЯ ПОСТОЯННОГО НАПРЯЖЕНИЯ

Изобретение относится к области прМ мышленной радиоэлектроники я может применяться в устройствах электропята:яяя постоянного напряжения.

Известны источники электропитания, содержащие основной стабилизатор поS стоянного напряжения я буферный блок, предназначенный для компенсации кратковременных провалов и выбросов выход-. ного напряжения, вызванных скачкообраз-.

10 ным изменением тока нагрузки jl).

В данных источниках питания буферный блок содержит транзисторы, с по-мощью которых осуществляется уетраненне провалов и выбросов выходного наt5 пряженяя.

Недостатком описываемого буферного блока является невозможность его использования в мощных ясточняках элект« ,ропитаняя, ввиду малойвелячяны предель».

Ъо-допустимых токов через транзисторы.

Известны источники питания постоянного напряжения, состоящие яз стабилизированного выпрямителя с 1 С -фильтром;

2 йодключенным через резистор к буферному блоку, содержащему тт параллельно соединенных ячеек яз койденсатора я зарядного тярястора, (l1 -1) логических схем И, каждая яэ которых первым входом соединена через диод с выходом формирователя импульсов, вторым жодом— с конденсатором предыдущей ячейки, а выходом — с управляющим электродом тярнстора последующей ячейки,,я блок управления, соединенный со входом формирователя импульсов, причем выходные выводы источника Питания подключены к выводам конденсатора ЬС -фильтра Г2).

В укаэанных источниках питания для обеспечения требуемой стабильности выходного напряжения необходимо большое количество ячеек в буферном блоке.

11елью изобретении является сняженяе числа ячеек до двух пря сохранения функциональных возможностей буферного блока

Указанная цель достигается тем, что в буферный блок источника питания по692026 ("ГОЯЕЕНОГ ) ЕЕЕ)ПЕ)ЯЖЕЕЕИЯ ВВОДЕНЫ TPH ЛОГИческих сх" мы И» лОГические схемы ИЛИНЕ, ИЛИ, две интегрирующих цепочки ц два разрядных тиристора» каждый из которых подклк)чен параллельно конденсатору своей ячейки, а еге управляющий электрод - к выходу вновь введенной схемы И, первым входом соединенной через диод с выходом формирователя импуль-, сов, а вторым — с выходом интегрирую- Ео щей цепочки, входом подключеннсй к конден ° сатору своей ячейки, причем вьеход первой интегрирующей цепочки соединен с одним входом схемы ИЛИ-НЕ, а второй интегрирующей цепочки -с другим входом схемы ИЛИНЕ и первым входом ИЛИ, второй вход которой подключен к выходу схемы ИЛИ-НЕ, а выход — к первому входу, третьей вновь введеннэй схемы И; вторым входом соединенной через диод с вы-Р0 ходом формирователя импульсов, а вы ходом — с управляющим электродом зарядного тиристора первой ячейки.

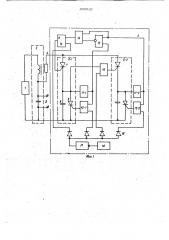

На фиг. 1 приведена иринципиальная

35 электрическая схема источника питания постоянногэ напряжения.

Источник, содержит стабилизированный выпрямитель 1 с L,C -фильтром 2, подключенным к выходным выводам 3 и через резистор 4 к буферному блоку 5Ä

30 состоящему из двух параллельйо включенных ячеек 6. Последние представляют собой последовательное соединение зарядного тиристора 7 и конденсатора 8; шун,35 тированного разрядным тиристором 9. Конденсатор первой ячейки черезсхему И 10 под ключен к управляющему электроду зарядного тиристора второй ячейки. Напряжение с конденсаторов через интегрирующие цепочки 1 1 ,40 и схемы И 12 подается на управляющие электроды своих разрядных тиристоров.

Сигналы с выходов ик егрирующих цепочек через схему ИЛИ-HE 13 подаются „на вход схемы ИЛИ 14, второй вход кото45 рой соединен с виходэм второй интегрирующей цепочки, а выход — со входом схемы И 15, прдключенной выходом к управляющему электроду зарядного тиристора первой ячейки. Сигнал с блока уп50 равления 16 подается через формирова»тель импульсов 17 и развязывающие диб- ды 18 иа вторые входы всех схем И.

Работает устройство следующим обраj5 зом.

При включении источника питания нулевой потенциал с конденсаторов ячеек прикладывается к схеме 13, вызывая по1 явление единичного сиг)еа)а на ее выходе, который через схему 14 поступаег на первый вход схемы И 15, обеспечивая открытое ее состояние по этому входу.

Данное состояние схемы сохраняется в статическом режиме нагрузки. При скачкообразном уменьшении тока через нее, изза наличия инерционного элемента - просселя, наблюдается выброс напряжения на выходных клеммах 3 и при превышении . напряжением допустимой величины блок управления 16 запускает формирователь импульсов 17. Импульс с его выхода через диод 18, схему И 15 поступает на управляющий электрод тиристора 7 ячейки 6-1, открывая последний. Конденсатор 8 ячейки 6-1 заряжается через резистор 4, тем самым аккумулируя энер-. гию сглаживающего дросселя и уменьшая величину выброса напряжения на выходных клеммах 3.

После заряда конденсатора 8 в ячейке 6-1 напряжение с него через интегрирующую цепь 11-1 поступает на вход схемы 13, поддерживая на ее выходе нулевой пэтенциал, который сохраняется все время вплоть дэ выключения источ ника, .поскольку в рабочем состоянии один

1 из конденсаторов ячеек обязательно заряжен. Нулевой потенциал прикладывается к одному из входов схемы ИЛИ 14, . вследствие чего сигнал на ее выходе пов« торяет сигнал на ее другом входе, подключенному к интегрирующей цепочке 112. На основании этого можно считать, что сигнал на входе схемы 15, соединенном с выходом схемы 14, .повторяет напряжение на интегрирующей цепочке ll2, т. е. схема И 14 будет функционировать аналогично схеме 10, замыкая кольцо между ячейками 6-2 и 6-1.

Рассмотрим функционирование ячеек буферного блока в следящем режиме в процессе отработки длительного выброса напряжения на нагрузке (выходные клеммй 3).Нафиг.2»йредставленывремен- I ные диаграммы, поясняющие работу бу,.ферного блока. На диаграмме А пока)зана форма напряжения на нагрузке. И момент т, о происходит скачкообразное

:уменьшение тока через нее и напряже . ние начинает увеличиваться.,:При. достижении им допустимого уровня на выхо,де формирователя в момент времени 11

Епоявляется импульс, приводящий к срабатыванию ячейки 6-1 и уменьшению на, пряжения на нагрузке. При дальнейшем увеличении последнего формирователь 16

5 69202 генерирует импульс в момент 1"..» и т.д.. до полной отработки выброса. Таким образом, с выхода формирователя 17 снимается последовательность коротких импульсов, подаваемых через диоды 18 на одни иэ входов логических схем И (диаграмма Б).

На диаграммах В и Д соответственно показана последовательность измене.ния напряжения, на конденсаторах ячеек»<

6-1 и 6-2, а на диаграммах Г и Е— напряжения на выходах интегрирующих цепочек 11-1 и 11-2. Первый импульс (момент времени t q ) открывает ти-. ристор 7 ячейки 6-1, конденсатор 8 ячейки заряжается и по одному из ахо-. дов открывает схемы И 10, Источник питания постоянного напряжения, состоящий иэ стабилизированного выпрямителя с С -фильтром, »тодключенным через резистор к буферному блоку, содержащему параллельно соединенные ячейки из конденсатора и зарядного тиристора, логическуюсхему И, которая первым входомсоединена через диод с выходом формирователя импульсов, вторымвходом-с конденсатором предь»дущей ячейки, а выходом — с управляющим электродом тиристора последующей ячейки, и блок управления, соединенный со входом формирователя импульсов, причем выходные выводы источника питания подключены к выводам конденсатора».С -фильтра, о т л ич вющийся тем, что, сцельюупрощения при сохранении функциональных возможностей буферного блока, в него дополнительно вверены три логические схемы И, логические схемы ИЛИ-HE и ИЛИ, две интегрирующих цепочки и два разрядных .тиристора, каждый иэ которых подключен параллельно конденсатору своей ячейки, а их управляющие электроды подключены соответственно к выходам двух вновь:введенных схем И, первым входом соединенных через диоды с выходом формйровате- . ля импульсов, а вторым — с выходами интегрирующих цепочек, входы которых подключены к конденсатору своей ячейки, причем выход первой интегрирующей цепочки соединен с одним входом схемы

ИЛИ НЕ, а второй интегрирующей цепочки - сдругимвходомсхемы ИЛИ HE ипервым входом схемы ИЛИ, второй вход которой подвиочен к выходу схемы

ИЛИ-НЕ, а выход - к первому входу третьей внбвь введенной схемы И, вторым входом соединенной через диод с выходом формирователя импульсов, а выходом — с управляющим электродом зарядного тиристора первой ячейки.

1. Устройства вторичных источ»»иков электропитания РЭА. Материалы семинара МДНТП им. Ф. Э. Дзержинского—

М., 1976, стр. 177-179.

2. Авторское свидетельство СССР

J4 598059> кл. G 05 Р 1/56, 1978

С окончанием заряда конденсатора .(, тиристор закрывается. С некоторой задержкой появляется сигнал на выходе интегрирующей цепочки 11-1 (диаграмма Г) и по одному из входов открывается схема И 12-1. Второй импульс в момент времени 1 через схему И 10 откры- 2. веет тиристор 7 ячейки 6-2 и через схему И 12-1 — тиристор 9 ячейки 6-1.

При этом конденсатор 8 ячейки 6-2 заряжается, конденсатор 8 ячейки 6-1 разряжается. зс

Логическая схема 10 запирается по одному из входов, С некоторой задержкой появляется нулевой. сигнал на выходе интегрйрующей цепочки l l-l, запирая схему 12-1, и единичный сигнал на вы- Ç5 ходе 11-2, отпирая по одному из входов схемы 12-2 и 15. Третий импульс в момент времени т через схему 15 открывает тиристор 7 ячейки 6-1 и через схему 12-2 — тиристор 9 .ячейки 6-2. 4о

Происходит заряд конденсатора 8 ячейки 6-1 и разряд конденсатора 8 ячейки

6-2. Таким образом, происходит заряд и разряд конденсаторов по кольцу до полной отработки выброса напряжения на нагрузке.

Сигналы, показанные на диаграммах

Г и Е, во время переходных процессов (например, в момент 64.) могут одновременно иметь низкий уровень, что может привести к появлению паразитного ! отпирающего сигнала на входе логической схемы 15.

Но поскольку данный момент времени задержан относительно момента времени

55 генерирования импульса формирователем

17, то это не оказывает влияния íà pa» v устройства.

Формула изобретения

Источники информации, принятые во внимание при экспертизе

692026

Подписное

Заказ 6237/49 Тираж 857

ЯНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул, Проектная, 4

Составитель Ю. Андреев

Редактор Д, Яепуришвили Техред С. Мигай I Корректор Н. Горват