Логический элемент или-нена мдптранзисторах

Иллюстрации

Показать всеРеферат

бунич„.„„ е9 ютена j, ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к ввт. сеид-ву (22) Заявлено 030877(21) 2513761/18-21 с присоединением заявки Но (23) Приоритет

Союз Советских

Социалистических

Республик

<н692О89

Н 03 К 19/08

Государственный комитет

СССР но делам изобретений и открытий (Д) УДК b21. 374 (088.8) Опубликоевно151079 Бюллетень Мо 38

Дата Опубликования описания 15.1079 (72) Авторы изо(сретения с .A . еРемин, А . И . каРмаэ инский и IG В . хоРошков

{71) Заявитель (54) ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ИЛИ-НЕ HA МДП-ТРАНЗИСТОРАХ

Изобретение относится к области электроники, импульсной и вычислительной техники и может быть использовано в цифровых интегральных схемах.

Известен логический элемент ИЛИ на МДП-транзисторах, содержащий вХодной.каскад и два инвертора . Входной каскад образован двумя транзисторами с.каналом р-типа, истоки которых соединены с соответствующими входами устройства. Стоки входных траМэисторов соединены с затворами транзисторов первого инвертора и через резистор — с истоками инвертирующих транзисторов первого и второго инвертора. Каждый из инверторов состоит из инвертирующего с каналом р-типа и нагруэочного с каналом р-типа транзисторов. Объединенные стоки инвертирующего и нагрузочного транзисторов первого инвертора соединены с объединенными затворами входных транзисторов и с объединенными затворами транзисторов второго инвертора, объе- 25 диненные стоки инвертирующего и нагруэочного транзисторов которого соединены с выходом элемента tl).

Описанный логический элемент обла дает рядом недостатков, затрудняющих

tro применение в интегральных микросхемах, а именно:

1) он включает линейный резистор большого номинала;

2) входные сигналы подаются на стоки транзисторов, сопротивление каналов которых модулируется напряжением с выхода первого инвертора, что ограничивает быстродействие устройства;

3) напряжение питания первого ин1вертора должно выбираться таким, чтобы под действием входных сигналов мог переключаться инвертирующий транзистор, на затвор которого подается напряжение с выхода первого инвертора.

Известен логический элемент на

МДП-транзисторах, содержащий входной каскад и инвертор, причем входной каскад состоит из нескольких входных транзисторов с каналом и-типа, включенных параллельно, и двух нагрузочных транзисторов, первый — с каналом п-типа, а второй — с каналом р-типа, сток первого и исток второго нагрузочных транзисторов подключены к шине питания, исток первого и сток второго нагрузочных транзисторов - к стокам входных транэис692089

10 торов, подложки и истоки, которых, а ." также "подложка первого нагруэочного транзистора подключены к общей шине, затворы нагрузочных транзистоРов входного каскада подключены к выходной шине элемента, а затворы входных транзисторов — к соответствующим входам элемента (21.

Недостаток данного устройства низкая помехоустойчивость.

Целью изобретения является повышение помехоустойчивости.

Для достижения поставленной цели в логический элемент ИЛИ.-НЕ на МДПтранзисторах, содержащий последова" тельно включенные первый и второй инверторы на транзисторах с дополняющим типом проводимости и входйой каскад, состбящий из двух входных транзисторов, затворы которых подключены к соответствующим входам элемента, истоки и подложки - к общей шине, а стоки — к стоку первого нагрузочного транзистора с каналом р-типа< истоку второго нагрузочного транзис- . тора с каналом и-типа и ко входу первого инвертораг исток и подложка первого нагрузочного транзистора и сток второго "нагрузочного транзистора подключены к щине питания, подложка второго нагрузочного:транзистора подключена к общей шине, а эатВоры первого и второго нагрузочных транзисторов к выходу второго инвертора, который является одновременно выходом элемента, в первый инвертор дополнительно введены инвертирующий с каналам итипа и нагрузочный c,êàíàëoì р-типа транзисторы, подложки которых подключены соответственно к общей шине и шине питания, а э.атворы - к затворам транзисторов первого инвертора, сток

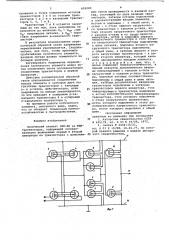

-. инвертирующего транзистора подключенк истоку дополнительного инвертирующего транзистора, сток которого подклю чен к стоку нЯтрузочного транзистора, исток которого псдключен к стоку дополнительного нагрузочного транзистора, исток которого подключен к общей шине..Устройство показано на фиг. 1.

Входной каскад состоит из первого 1. и второго 2 входных транзисторов с каналом и-типа и первого 3 с кана лом и-типа и второго 4 с каналом ртипа нагрузочных транзисторов.

" Первый инвертор включает первый

5 и дополнительный б с каналами и типа инвертирующие транзисторы, а также первый 7 и дополнительный 8 нагрузочные транзисторы с каналом р-типа.

Второй инвертор состоит иэ инвертирующего транзистора 9 с каналом и-типа и нагруэочного транзистора

10 с каналом р-типа.

Логический элемент включает также: шины питания 11, нулевого потенциала 12 и выходную 13.

Источки и подложки входных транзисторов 1 и 2, подложка нагрузочного транзистора 3, истоки инвертирующих транзисторов 5 и 6, а также исток и подложка инвертирующего транзистора 9 присоединены к шине нулевого потенциала 12. Затворы входных транзисторов 1 и 2 соединены с ооответс вующими входами элеt мента Вх. 1 и Вх,2. Стоки входных транзисторов 1 и 2 объединены с истоками нагрузочного транзистора 3 со стоком транзистора 4 и с затворами транзисторов первого инвер тора 5, 6, 7 и 8. Подложка транзистора 4, а также сток транзистора 3, исток транзистора 4, подложки траниэстора 7,:истоки и подложки нагрузочных транзисторов 8 и 10 соединены с шиной питания 11. Затворы транзисторов 3 и 4, а также стоки транзисторов второго инвертора 9 и 10 подключенй к выходной шине.13. Сток транзистора 5 объединен с истоком транзистора 6. Стоки транзисторов, 6 и 7 объединены. с затворами транзисторов 9 и 10. Исток транзистора

7 объединен со стоком транзистора 8.

Рассмотрим принцип работы предлагаемого логического элемента .

Отметим, что для повышения помехоустойчивости элемент должен обладать передаточной характеристикой, имеюЭ5 щей петлю гистерезиса, показанную на фиг. 2. Изменение ширины петли гистерезиса приводит к изменению помехоустойчивости как по отношению к положительной, так и отрицательной

40 помехам..

Петля гистерезиса может быть получена в схеме, обладающей положительной обратной связью. Изменение порогов срабатывания первой и второй ветви передаточной характеристики с петлей гистерезиса можно добиться, изменяя Пд„ и U„ Для этого и введег ны дополйительные транзисторы в первый инвертор.

Напряжение отпирания транзисторов

6 и 7 зависит от разности потенциалов между их подложками и истоками.

Для каждой пары транзисторов 5, 6 и

7, 8 один из них, в частности транзистор 8 для пары 7, 8 и транзистор

5 для пары 5, б, создает отрицательную обратную связь для другого транзистора, в результате чего изменяется напряжение отпирания транзисторов б и 7, Это приводит к изменению по60 ложения передаточной характеристики ветви 1 и 2 сдвигаются по направлению ветвей 1 и 2.

Увеличение входного напряжения на затворе одного иэ инвертирующих тран65 эисторов приводит к уменьшению на692089

Формула изобретения

5 пряжения, в точке соединения истоков транзисторов 3 и 4 со стоками транзисторов 1 и 2 и с затворами транзис торов 5, 6, 7 и 8.

Транзисторы 7 и 8. остаются закрытыми до тех пор, пока напряжение не изменится до величины En Uop,где

Е„- напряжение питания, à U — пороroaoe напряжение р-канально% тран.зистора.

В результате возникновения отрицательной обратной связи напряжение переключения увеличивается. Следова тельно, для того, чтобы произошло срабатывание логического элемента, входной сигнал должен измениться на большую величину.

Регулировать напряжение переключения.логического элемента можно путем увеличения числа последовательно соединенных транзисторов в первом инверторе.

Действие положительной обратной связи обеспечивается соединением выхода элемента и затворов двух йа-. грузочных транзисторов с каналами и- и р-типов. Действительно, если напряжение на выходе увеличивается, : то это приводит к запиранию р-канального транзистора 4 и отпиранию и-канального транзистора 3.

Из принципа работы логическогб элемента, описанного выше, видно,, что он обладает повышенной помехоустойчивостью и быстродействием..

Логический элемент ИЛИ-НЕ. на ИДПтранзисторах, содержащий последовательно включенные первый и второй инверторы на транзисторах с дополняющим типом проводимости и входной каскад, состоящий из двух входных транзисторов, затворы которых подключенй . к соответствующим входам элемента, истоки и подложки — к общей шине, а стоки — к стоку первого нагрузочного транзистора с каналом р-типа, истоку второго нагрузочного транзистора с каналом tl-òaïà и ко входу первогo. инвертора, исток и подложка первого нагрузочного транзистора и сток второго нагрузочного транзистора подключены к шине питания, подложка второго нагрузочного транзистора подключена, к общей шине, а затворы первого и второго нагрузбчных транзисторов — к выходу второго инвертора, который является одновременно выходом элемента, отличающийся тем, что, с целью повышения помехоустойчивости, в первый инвертор дополнительно введены инвертирующий с каналом и-типа и

70 нагрузочный с каналом р-типа транзисторы, подложки которых соответственно подключены к общей шине и шине питания, затворы дополнительно введенных тразисторов подключены к затворам

2д транзйсторов первого инвертора, сток инвертирующего транзистора подключен к истоку дополнительного инвертирующего транзистора, сток которого подключен к стоку нагрузочного транзистора, исток которого. подключен к стоку дополнительного нагрузочного транзистора, исток которого подключен к общей шине. Источники информации принятые во внимание при экспертизе

35 1. Авторское свидетельство СССР

Р 4051.78, кл, Н 03 К 19/08, 1972, 2. Заявка Ф 2454132/21, кл. H 03 К 19/08, 16.02.77, по кото рой принято решение о выдаче авторс40 кого свидетельства.

692089 и

Заказ 6240/52

Тираж 1060 П одпис ное

1IdHH11H Государственного комитетат СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д, 4/5

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4

Составитель И. Дубровский

Редактор Д. Мепуришвили Техред Л.йлберова КоРРектоР Ю, Макаренко