Устройство для обнаружения сигналов

Иллюстрации

Показать всеРеферат

О(ичасе

4ФМййв s евам дй1аД

0ПИС

ИЗОБРЕТЕНИЯ 1ц 692:0

6овз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву 604415 (22) Заявлено 17.05.77 (21) 2487332/18-09 с присоединением заявки №вЂ” (23) Приоритет

Опубликовано 23.07.82. Бюллетень № 27

Дата опубликования описания 23.07.82 (51) M. Кл.з

G О1 S 7/30

Государственный комитет (53) УДК 621,396.96 (088.8) по делам изобретений и открытий (72) Авторы изобретения

К. К. Васильев и Г. Ф. Комиссаров (71) Заявитель (54) УСт! 0йМВ0 ДЛЯ ОИНАРУЖКНИЯ СИГНАЛОВ

Изобретение относится к технике радиолокации, в частности к технике выделения некогерентных сигналов на фоне пестационарных помех, и может использоваться в устройствах цифровой обработки радиолокационной информации, работающих при воздействии коррелированных помех с изменяющимися параметрами.

По основному авт. св. 604415 известно устройство для обнаружения сигналов, содер кащее аналого-цифровой преобразователь, выход которого соединен с входом

Л последовательно включенных многоразрядных регистров сдвига, каждый из которых содержит 1(отводов, синхронизатор, первый и второй выходы которого соединены соответственно с входами управления аналого-цифрового преобразователя, и каждый из N многоразрядных регистров сдвига, и блок принятия решения, введен20 ные Л4-логических блоков и два сумматора, при этом одноименные отводы и выходы каждого из /V многоразрядных регистров сдвига соединены с соответствующими входами каждого из М логических блоков, 25 выходы одного из которых соединены с входами первого сумматора, а выходы всех остальных логических блоков, а так ке отводы первого многоразрядного регистра сдвига соединены с соответствующими входами второго сумматора, а выходы сумматоров соединены с входами олока принятия решения; причем каждый из логических олоков содержит (N — 1) логических элементов, прн этом первые входы каждого из (М вЂ” l) логических элементов и второй вход (N — 1)-го логического элемента являются соответствующими входами логи еского блока, выход каждого из (!U — I)-ых логических элементов является соответствующим выходом логического блока, а вторые н первые входы каждого из (N — 1)-ых логических элементов, кроме первого, соединены мехкду собой; при этом каждый из логических элементов логического блока выполнен в виде последовательно соединенных блока вычитания н ключа, второй вход которого соединен с вторым выходом блока вычитания, первый и второй входы которого являются соответственно первым и вторым входами логического элемента, а выход ключа является выходом логического элемента,(1).

Однако это устройство характеризуется недостаточной стабильностью уровня ложных тревог при изменении корреляционных свойств помехи.

Целью изобретения является увеличение стабильности уровня ложных тревог при изменении корреляционных свойств помех.

692375

Для этого в устройство для обнаружения сигналов, содержащее аналого-цифровой преобразователь, выход которого соединен с входом N последовательно включенных многоразрядных регистров сдвига, каждый пз которых содержит К отводов, сш|хронизатор, первый и второй входы которого соединены соотвстствснпо с вход<1mif ??||???????????????? ??????????????-????|1|???????????? ??????????????????????????||?? ?? ?????????????? 1i3 n ???????????????????????????? ?????????????????? ????????????, ???????? ???????????????? ??????????????, ?????????????????? ??-???????????????????? ???????????? ?????? ??????????????????, ?????? ???????? ?????????????????????? ???????????? ???????????? ???? ???????????? ?????????????????? ?? ?????????????????????????????? ?????????????? ?? ???????????????????? ????????????, ???????????? ?????????????? ?????????????? ???????? ?????????????????? ?? ?????????? ?????????????????????????????? ???????????????? ???????????????????????????????? ?????????????? ???????????????????? ?????????? ???????????????? ??????????????; ???????????? ???????????? ??????????>кит (N — 1) логических элементов, при этом первые входы ка>кдого из (N — 1) логических элементов и второй вход (N — 1)-ro логического элемента являются соответствующими входами логического блока, выход каждого из (N — 1)-ых логических элементов является соответствующим выходом логического блока, а вторые и первые входы каждого из (N — 1)-ых логических элементов, кроме первого, соединены ме>кдy собой; при этом каждый из логических элементов логического блока выполнен в виде последовательно соединенных блока вычитания и ключа, второй вход которого соединен с вторым входом блока вычитания, первый и второй входы которого являются соответственно первым и вторым входами логического элемента, а выход ключа является выходом логического элемента; введен блок умножения, (К+1) N входов которого соединены с выходами и с соответствующими из К отводов N многоразрядных регистров сдвига, а выход блока умножения соединен с дополнительным входом второго сумматора.

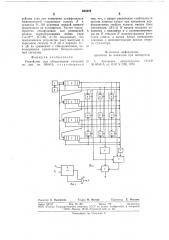

На фиг. 1 приведена структурная электрическая схема предложенного устройства; на фиг. 2 — схема, поясняющая работу логических элементов.

Устройство для обнаружения сигналов содержит аналого-цифровой преооразователь 1, N последовательно включенных многоразрядных регистров сдвига 2, синхронизатор 3, блок 4 принятия решения, М логических блоков 5, первый н второй сумматоры 6 и 7 соответственно, каждый нз логических блоков 5 содержит (Л вЂ” 1)

Ч вЂ” 1 логических элементов 8, а каждый нз логических элементов 8 — последовательно единенные блок вычитания 9 и ключ 10.

Устройство содержит блок умножения (1(+1) N входов которого соединены с hbiкодами и с соотвстствующнмп нз К отводов Л мпогоразряднык регистров сдвига 2, а выход блока умножения 11 соединен с дополнптельнь|м входом второго сумматора 7.

Устройство работает следующим образом.

В!|деос||г!!алы с выхода приемника РЛС поступают ца аналого-цифровой преобразователь 1, а далее — на многоразрядные регистры сдвига 2. Синхронизатор 3 обеспечивает синхронную работу аналого-цифрового преобразователя 1 и управляет движением сигнала в многоразрядных регистрах сдвига 2. Лнализ поступающих в многоразрядные регистры сдвига 2 сигналов осуществляется при помощи логических блоков 5, состоящих из логических элементов 8. Если на вход логического элемента

8 поступают сигналы Х! и Х> из двух соседних периодов повторения и Х!)Х, то на выходе ключа 10 образуется их разность У=Х! — Х„которая поступает затем

25 l3 сумматорь| 6 !. 7. Е.; Х|(Х2, То на выходе ключа 10 находится нуль. Таким образом, в сумматорах 6 и 7 суммируются только положительные приращения процесса в области предполагаемого сигнала в первом сумматоре 6 или в области помехи во втором сумматоре 7.

Кроме того, на вход второго сумматора 7 поступают дополнительные отсчеты в области помехи с выходов многоразрядных регистров сдвига 2, умноженные в блоке умножения 11 на весовой коэффициент а, зависящий от заданной величины ложной тревоги. Значение весового коэффициента а равно

4О и

1 /p — | — !

-|Л! где у — порог обнаружения блока приня45 тия решения 4;

à — заданная величина ложной тревоги; и — число отсчетов в области помехи по дальности; у N — число импульсов в пачке.

Для принятия решения о наличии цели в блоке 4 принятия решения используется сумма положительных приращений процесса в области предполагаемого сигнала, 55 нормирования к сумме положительных приращений в области помехи и сумме дополнительных отсчетов в области помехи, умноженной па весовой коэффициент сс.

|||! Использование информации, содержащейся в положительных приращениях помеховых отсчетов, а также во взвешенной сумме дополнительных отсчетов в области помехи позволяет ооеспечить хорошую ста||; онльность ложной тревоги па выходе устройства (так при изменении коэффициента межпериодиой корреляции помехи R в пределах 0... 0,9 величина ложной тревоги практически ие изменяется). Расчет характеристик обнаружения для релеевской модели коррелированных помех (при

Г=10 —, N=20, п=3) показывает, что предложенное устройство дает выигрыш в пороговом сигнале 5 — 6 дБ и порядка 3—

4 дБ по сравнению с обнаружителем, использующим накопление бинарио-квантовых сигналов.

Формула изобретения

Устройство для обнаружения сигналов по авт. св, 604415, отл ич а ющееся тем, что, с целью увеличения стабильности уровня ложных тревог при изменении корреляционных свойств помехи, введен блок умножения, (К+1) N входов которого со5 единены с выходами и с соответствующими из К отводов N многоразрядных регистров сдвига, а выход блока умножения соединен с дополнительным входом второго сумматора.

Источники информации, принятые во внимание при экспертизе

15 1. Лвторское свидетельство СССР № 604415 кл. G 01 S 7/30, 1976. редактор О. Филиппова Техред И. Пенчко Корректор Е. Михеева

Заказ 1021/9 Изд. № 184 Тираж 719 Подписное

НПО «Поиск» Государственного комитета СССР по делам изобретений и открытий

1!3035, Москва, К-35, Раушская паб., д. 4/5

Типография, пр, Сапунова, 2