Устройство для цифрового усреднения двоично-кодированных сигналов

Иллюстрации

Показать всеРеферат

(11 694867

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (бl) Допол1штельиое к авт. свид-ву (22) Заявлено 09.08.76 (21) 2394955, 18-24,,)i) Л!. Кл.-

6 06Г 15 36 с присоединением заявки . Й

Государственный комитет (23) Приоритет (43) Опубликовано 30.10.79 Ечоллетеиь ¹ 40 (45) Дата опубликования описания 30.10.79 (53) УДК 681.325 (088.8) ло делам изобретений и открь (72) Автор изобретения

Б. Я. Ваинштеин (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ЦИФРОВОГО

УСРЕДНЕНИЯ ДВОИЧНО-КОДИРОВАННЫХ

СИГНАЛОВ

Изобретение относится к специализированным средствам вычислительной техники и предназначено для обработки цифровых сигналов.

Известно устройство для усреднения двоично-кодированных сигналов 1), содержащее сумматор, реверсивный сче1чик, регистры памяти и цифровые иеремножители чисел. 11ри использовании этого фильтра для усреднения двоично-кодированных сигналов возникают ошиоки за счет Округления чисел при цифровом умножении, которые накапливаются из-за наличия оорагной связи. Кроме того, большое количссгво перемножителей усложняет схему.

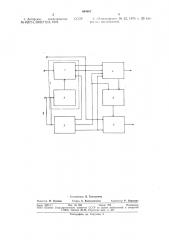

Наиболес близким техническим решением к изобретению является устройство, содержащее блок задержки, выход которого подключен к первому входу сумматора, второй вход которого соединен с первым выходом блока управления (2J

Недостаток устройства заключается в его сложности из-за наличия пер емиожителей и многовходового сумматора.

Цель изобретения — упрощение устройства.

С этой целью в устройство для цифрового усреднения двоично-кодированных сигналов введены реверсивный счетчик и элемент стробирования. При этом счетный вход реверсивногÎ счетчика подключен к выходу элемента стробирования, первый вход которого соединен с выходом переноса старшего разряда сумматора, третш1 вход которо — î объед1гнен с вторым входо» элемента строоирования и соединен

c IiTopbDi выходом Олока управления. 1ОТиертыи В .Од сумм а 1 Ора Ооъединен с lit рными входами олока задержки и реверсивного счетчика и является первым входом устроиства. Третий IIIixop блока управления иодк;почси к второму входу блока задсрж1 и, TpcTIIll вход IioTop010 c i A IIT H 10рым входом ус1ройства. 11ервый вход бло15 ка управления ооъсдинен с четвертым входом О:101 а задержки и является треl ыlм входом устроиства. 11ервый выход блока управления подключен к управляющему входу реверсивного счетчика, выход которого является первым выходом устройства, а выход сумматора — вторым выходом устройства.

Кроме того, блок задержки содержит элемент пам11ги и c÷cò÷èê, вы..од которого подключен к 1 срвому входу элемента памяти, второй, -lp«liiil и четвертый входы которого — э,î c001 встс1вснио первый, второй и трет и1. входы О;1 онa задержки, Вход счст30 чика;гвлястся чствсртым входом блока за694867

Составитель Л. Григорьянц

Редактор И. Грузова Техред А. Камышникова Корректор P. Беркович

Заказ 2521/11 Изд. № 623 Тираж 780 Подписное

НПО «Поиск» Государственного комитета СССР по делам изобретений и открытий

113035, Москва Ж-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2

1. Авторское свидетельство СССР № 465714, Н03Н 7/10, 1975.

2. «Зле1троника» ¹ 22, 1970, с. 20 (11ерев т. с английского).