Устройство синхронизации

Иллюстрации

Показать всеРеферат

7, кч, " ., )

ИЗОБРЕТЕНИЯ пщ 69498

Союз Советских

Социалистических

Республик (б1) Дополнительное к авт. свид-ву (22) Заявлено 28.09.77 (21) 2529474/18-09 с присоединением заявки № (23) Приоритет (43) Опубликовано 30.10.79. Бюллетень № 40 (45) Дата опубликования описания 30.10.79 (51) М. Кл.з

Н 04L 7/02

Гесудерствеииый квмитет (53) УДК 621.394.662 (088.8) по делам изобретеиий и открытий (72) Авторы изобретения

В. В. Кузнецов и В. Я. Болдырев (71) Заявитель (54) УСТРОЙСТВО СИНХРОНИЗАЦИИ

Изобретение относится к связи и может использоваться для синхронизации и фазирования местных генераторов приемников систем связи.

Известно устройство синхронизации, содержащее опорный генератор, формирователь импульсов, элементы И и И вЂ” HE u последовательно соединенные делитель частоты и дискриминатор знака рассогласования (1). 10

Однако известное устройство имеет недостаточную точность синхронизации.

Целью изобретения является повышение точности синхронизации.

Для этого в устройство синхронизации, 15 содержащее опорный генератор, формирователь импульсов, элементы И и И вЂ” НЕ и последовательно соединенные делитель частоты и дискриминатор знака рассогласования, введены блок управления и (n+1) 20 разрядный регистр сдвига, при этом выходы трех последних разрядов (и+1) разрядного регистра сдвига через блок управления подключены к первому входу первого разряда, к второму входу которого подключен выход второго разряда (п+1) разрядного регистра сдвига, а выходы первого разряда (и+1) разрядного регистра сдвига подключены соответственно к входу делителя частоты и к первому входу 30 формирователя импульсов, второй вход которого объединен с соответствующим входом дискриминатора знака рассогласования, выходы которого подключены соответственно к первым входам элементов И и

И вЂ” НЕ, два других входа которых объединены между собой попарно и подключены к соответствующим выходам формирователя импульсов, выход элемента И подключен к соответствующему входу блока управления и к соответствующему входу (п+1) разряда (и+1) разрядного регистра сдвига, а выход элемента И вЂ” НЕ подключен к соответствующим входам блока управления и «и» разряда (n+1) разрядного регистра сдвига, к тактовым входам (n+1) разрядов которого подключены выход опорного генератора.

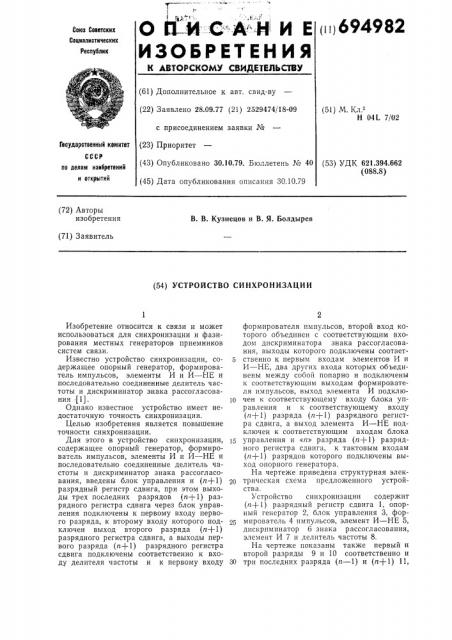

На чертеже приведена структурная электрическая схема предложенного устройства.

Устройство синхронизации содержит (п+1) разрядный регистр сдвига 1, опорный генератор 2, блок управления 3, формирователь 4 импульсов, элемент И вЂ” НЕ 5, дискриминатор б знака рассогласования, элемент И 7 и делитель частоты 8.

На чертеже показаны также первый и второй разряды 9 и 10 соответственно и три последних разряда (n — 1) и (п+ 1) 11, 3

l2 и 13 соответственно (п+1) разр ..диого регистра сдвига 1.

Устройство работает следующим обр =:зом. (и+1) разрядный регистр сдвига 1 образует управляемыи делитель частоты с обратными связями. Управление коэффициентом деления осуществляется с ьыхода дискриминатора 6. 1lри отсутствии входного сигнала, поступающего на вход дис- {О криминатора б, на обоих его выходах имеет место нулевой потенциал.

На выходах элементов И вЂ” Hi" 5 1.: И 7 уровни будут соответственно равны логической единице (лог. 1) и логическому пулю 15 (лог. 0).

Ы этом случае последний разряд 13 (и+1) разрядного регистра сдьига i выключен и коэффициент деления регистры равен (2+и). э{)

При поступлении входного сигнала на дискриминатор b, попадающего в зону исключения, дискриминатор б вырабатывает сигналы, уровни которых на и рзых входах элементов И вЂ” НЕ 5 и И 7 p2131IHI соответственно лог. 1 и лог. О, а на другис входы элементов И вЂ” НЕ 5 и И i с выхода формирователя 4 один раз за период передачи одного символа информации подается сигнал, имеющий уровень лог. 1 и длительность, равную периоду сигнала (n — i) разрядного регистра сдвига 1, так как на первый вход формирователя 4 подается сигнал с первого разряда 9 (и+1) разрядного регистра сдвига i, а на второи вход формирователя 4 подается периодическии сигнал с выхода делителя частоты а.

Таким образом, на выходе элементы И—

HE 5 однократно потенциал оудет иметь уровень лог. О, а на выходе элемента И 7 сохранится уровень лог. О. Ь этом случае разряд 13 (и+1) разрядного регистра сдвига 1 окажется отключенным, а разряд 12 отключенным однократно. Еоэффициент деления (n+1) разрядно о регистра сдвига 1 однократно будет равен (2-1-п — 1).

При поступлении входного сигнала, попадающего в зону добавления, дискри.1инатор б вырабатывает сигналы, уровни которых на первых входах элементов И вЂ” НЕ 5 и

И 7 равны соответственно лог. О и лог. 1.

Формирователь 4, как и в предыдушсм случае, однократно вырабатывает потенциал лог. 1.

На выходе элемента И вЂ” НЕ 5 будет постоянно потенциал лог, 1, а на выходе элемента И 7 будет однократно лог. 1. Разряд

12 (п+1) разрядного регистра сдвига 1 будет подключен постоянно, а разр..д 13 будет подключен однократно. Коэфф{1цпсит деления (п+1) разрядного регистра сдвига 1 однократно будет равен (2+и+1).

Таким образом, обеспечивается управление коэффициентом деления на +-1 двух последовательно включенных дели..елей 65 частоты (и- -1) разрядного pp: истра сдвиi а 1:- JOJIII Гел1 ч2стоты 8.

1 pii pc2ëèç2öèè чс 1 130 IcTB2 с{lнхi30HH311ции па J Ji триггерах и при использован{ни

l3 качсстl3с llеpi301 О 132313яда 9 (n7 — 1) ра рядно.о регистра сдвига i J ij 1риггера с

ТР ем я J ii Jl i C TP c.hi 31 J< ВХоды.,1 11 P o Jib 0JI Oкы управле IHH 3 мо{ут выполня-ь эти три входы первого разряда 9. Так кык вс тактовь{с входы (и-{-11 разрядов (и+1) раз13ИДНОГО 13 еГистр 2 сдь пl а 1 Ilодlс{1 10чсны н епосредственно к выходу опор IUiî I åíåð2TOра 2 и входы григгеров (разрядов) подключены к ьыходам предыдущих триггеров (разрядов) без промежуточных элементов, то быстродействие (n â€, i) разрядного регистра сдвига будет равно быстродействию одпночно1.о триггера. 11одключение тактовых входов триггеров (первые входы) формирователя 4 K 13ыходу IGpi3010 разряда 9 позволяет допускать задержку импульсов, IIOcT) па{ощих ны соо1ве ству{ощие входы разрядов 12 и 13, большую, чем два такта частоты опорного генератора 2, iipH рсылизации предложенногO устройства на

Д три{герах в качестве блока управления можно использовать один из логических элементов; трехвходовои элемент И, трехвходовой элемент И†HL., трехвходовой элемент И.{1И вЂ” -HL;, эле:1ент 2И вЂ” 3И,)1И—

11Е. и другие.

32 счет задержки ь блоке управления 3

I рыничная частота (точность синхронизации) устройсTI32, реализованного на ц триГГерах> по сравнению с устроllством н2 .{К триггерах меньше предельной на iQ—

11редложснное устройство i:oçâîëÿåT реализовать максимально 130зможную точность синхронизации и фазирования местных генераторов.

Формула изобретения

Устройство синхронизации, содержащее опорный генератор, формирователь импульсов, элементы И и И вЂ” НЕ и последовательно соединенные делитель частоты и дискриминатор знака рассогласования, отлич а 1о щ е с с я тем, что, с целью повышения точности синхронизации, введены блок управления и (и-{-1) разрядный регистр сдвига, при этом выходы трех последних разрядов (и+1) разрядного регистра сдвига через блок управления подключены к первому входу первого разряда, к второму входу которого подк{почен,выход второго разряда (n+1) разрядного регистра сдвига, а выходы первого разряда (п+1) разр:.;,Ио э рpãècòð2 сдвига подключены соотве-,ствс{;"о к входу делителя частоты и к первому зходу формирователя импульсов, второй вход которого объединен с соответствующим входом дискриминатора знака рассогласования, выходы которого подклю694982

Составитель Е. Петрова

Техред А. Камышникова

Редактор Н. Коляда

Корректор Е. Хмелева

Заказ 2513/12 Изд. Из 694 Тираж 780 Подписное

НПО «Поиск> Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2 чены соответственно к первым входам элементов И и И вЂ” НЕ, два других входа которых объединены между собой попарно и подключены к соответствующим выходам формирователя импульсов, выход элемента

И подключен к соответствующему входу блока управления и к соответствующему входу (и+1) разряда (и+1) разрядного регистра сдвига, а выход элемента И вЂ” HE подключен к соответствующим входам бл, . .а у; равлени, и и разряда (и+1) разрядного регистра сдвига, к тактовым входам (и+1) разрядов которого подключен

5 выход опорного генератора.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Кв 478451, кл. Н 041 /02, 1972 (прототип).