Устройство для сравнения двоичных чисел

Иллюстрации

Показать всеРеферат

!

„« нс

0 P(И "" «ет

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик

Ж

//

« (61) Дополнительное и авт. саид-ву (22) Заявлено 10.08.77(21) 2516198/18-24 (51) М. КЛ. с присоединением залами HP

G 06 F 7/04

Государствеииый комитет

СССР по делам изобретений и открытий (23) Приоритет

Опубликовано 053.179 Бюллетень HP 41 (53) УДК 681 .325 ° .5 (088.8) Дата опубликования описании 0511.79 (72) Автор изобретения

Л. H. Бутенко (71) Заявитель (54) УСТРОЙСТВО ДЛЯ СРАВНЕНИЯ ДВОИЧНЫХ ЧИСЕЛ

Изобретение относится к области автоматики и вычислительной техники и может быть применено в телеметрических устройствах контроля цифровых данных, получаемых с выходов преобразователей угол-код .

Известно устройство для сравнения двоичных чисел (1), представляющее собой схему сравнения чисел, представленных последовательным, двоичным кодом. Это--устройство сравйейия чисел состоит из триггера и элементов И.

Недостаток этого устройства — ограниченная область применения. С его помощью можно выявить толька факт равенства чисел по всем разрядам. В тех случаях, когда необходимо сравнивать между собой числа с заданной точностью, это устройство не может быть использовано.

Наиболее близким к предлагаемому техническим решением является устройство, содержащее триггеры, последовательный сумматор>элемент неравнознач-5 ности, элементы И (2).Устройство обесйечивает сравнение чисел с заданным допуском.

Недостаток этого устройства — невозможность сравнивать между собой числа, образующие замкнутое числовое кольцо, что имеет место, например, в преобразователях угол-код .

Цель предлагаемого изобретения расширение диапазона кодов сравниваемых чисел за счет обеспечения сравнения чисел, заданных циклическим кодом.

Для этого в устройстве информационные входы последовательного сумматора подключены к входным шинам сравниваемых чисел, прямой выход лоследовательного сумматора соединен с первым входом установки в единичное состояние первого триггера, второй вход установки в единичное состояние которого подключен к выходу первого элемента И, соединенному с первым входом установки в нулевое состояние второго триггера, второй вход установки в нулевое состояние которого Подключен к выходу второго элемента И, соединенному со входом установки В нулевое состояние первого триггера, инверсный выход последовательного сумматора подключен. ко входам установки в единичное состояние второго н третьего триггеров, инверсный и прямой выходы третьего триггера соединены соот696440 ветственно с первыми входами первого и второго элементов И, вторые входы которых подключены к шине управления, прямые выходы первого и второго триггеров соединены со входами элемента неравнозначности, а входы установки в нулевое состояние последовательного сумматора и третьего триггера подключе7 ны к шине начальной установки.

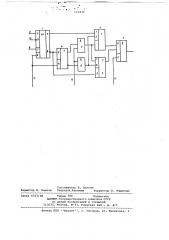

Схема предлагаемого устройства приведена на чертеже. 10

Предлагаемое устройство для сравнения двоичных чисел содержит последовательный сумматор 1, триггеры 2, 3 и 4, элементы И 5 и б, элемент 7 нерав" нозначности, шину 8 синхронизации, информационные шины 9 и 10 первого и второго сравниваемых чисел, шину 11 начальной установки, шину 12 управления для задания величины допуска сравнения и шину 13 управления опросом, При сравнении цифровых данных преобразователей угол-код преобразователи угол-код имеют замкнутую кодовую шкалу и кодированные сектора . наименьшего числа 0 и наибольшего числа 2 †((для и-разрядного двоич- 25 ного кода) на кодирующих элементах датчиков угла располагаются рядом.

Поэтому, сравнивая между собой коды чисел 0 и 2" -1, следует считать, что они отличаются одно от другого на 3Q единицу дискретности преобразователя угол-код, а не на 2 -1, числа 1 и и 2 .-2 — на три единицы дискретности, и а не на 2"-3 и т. д. При сравнении чисел, получаемых от преобразовате- 35 лей типа угол-код, следует учитывать наименьшую разность между числами в единицах дискретности по .,окружности кодирующего элемента преобразователя или,что одно и то же,на- 40 именьшее угловое расстояние в едини.цах дискретности между кодированными секторами чисел на кодирующих элементик преобразователей угол-код .

Предлагаемое устройство работает следующим образом.

Перед началом сравнения двух чисел

A и В, представленных двоичным последовательным кодом, по шине 11 начальной установки следует импульсный сигнал, который устанавливает триггер

4 в состояние 0, а последователь,ный сумматор — в начальное состояние.

Непосредственно после этого сигнала, синхронно с тактовыми импульсами, следующими по шине 8, на входные шины 9 55 и 10, поступают последовательно, разряд за разрядом, начиная с младшего, коды сравниваемых чисел A и В . Число

A поступает на неинвертированный, а число  — на инвертированный входы gp последовательного комбинационного сумматора 1. В результате сложения прямого кода числа А и обратного кода числа В на прямом выходе сумматора 1 формируется разность чисел A и В в об-65 ратном двоичном коде, а на инверсном выходе — инвертированное значение разности чисел.

Могут встретиться три типа комбинаций цифр в разностях чисел:

1) в младших разрядах, до К-1-го включительно, имеются любые комбинации нулей и единиц, кроме комбинаций,i состоящей из всех единиц (нулей), а в старших разрядах — только нули (единицы);, 2) в младших разрядах до К-1-го включительно имеются любые комбинации нулей и единицы, кроме комбинации, состоящей из всех единиц (нулей), а в старших разрядах — только единицы (нули) у

3) во всех разрядах разности чисел содержатся только единицы, .Если имеют место разности чисел первого и второго типов,то после прохождения первых К-1 разрядов разности чисел А и В триггер 4 под действием хотя бы одного сигнала 1,который появится на инверсном выходе последовательного сумматора 1, будет установлен в состояние 1, В момент времени между прохождениями К-1-ro, и К-го разрядов разности чи сел сл еду ет по ши н е 12 импуль с нйй сигнал, сбответствующей 1 . В этот момент времени на выходе элемента И

5 появится сигнал 1 (т к. на оба входа этого элемента поданы сигналы 1 ), который установит триггеры 2 и 3 в состояние 0 . Если, начиная с К-го разряда разности на прямом выходе последовательного сумматора 1 будут следовать сигналы 1, то триггер 2 установится в состояние 1, а триггер 3 останется в состоянии 0 . После появления последнего старшего. разряда разности чисел на выход последовательного сумматора;.

1 поступает опрашивающий стробирующий сигнал по шине 13. Так как на логические входы элемента 7 неравнозначности поданы разные сигналы — сигнал 1 с выхода триггера 2 и сигнал 0 с выхода триггера 3, то на выходе элемента 7 неравноэначности появится сигнал 1, свидетельствующий о равенстве сравниваемых чисел с точностью до 2 -1 единиц дисретности.

К

Если, начиная с К-ro разряда, на пряivIoM выходе последовательного сумматора 1 будут следовать нули, то триггер

2 останется в прежнем состоянии 0, а триггер 3 изменит состояние 0 на 1 . В этом случае триггеры 2 и 3 окажутся тоже в разных состояниях, следовательно, в момент прихода спрашивающего сигнала на выходе элемента 7 неравнозначности будет сигнал 1 . Если на выходах сумматора

1, начиная с К-го разряда, в разности чисел будут и нули и единицы, т.е. разность чисел не отвеЧает требованиям

696440 разностей первого и второго типов, то оба триггера 2 и 3 будут установ- лены в состояние 1 и,следовательно, при опросе элемента 7 неравнозначности на ее выходе будет сформирован сигнал 0, свидетельствующий о 5 неравенстве чисел.

При появлении на выходах сумматора разности чисел третьего типа, т.е. при появлении всех единиц как в младших К-1 разрядах, так и старших, начиная с К- ro в момент появления тактирующего сигнала триггер 4 окажется в состоянии О, так как после установки его в состояние ™ О

его вход установки в единичное состояние поступали только сигналы О с выхода сумматора 1 и сигнал 1 по.явится на выходе элемента И б. Этим .-игналом триггер 2 будет установлен в состояние 1, а триггер 3 — в состояние О . Следующие (начиная с

К-ro разряда) сигналы с прямого выхода последовательного сумматора равны 1 . Поэтому они будут как бы подтверждать состояния триггера 2, а на вход триггера 3 будут поступать 25 с выхода сумматора сигналы 0, не изменяющие состояния триггера 3. Он останется в состоянии 0 . Таким образом, к моменту прихода опрашивающего сигнала триггеры 2 и 3 будут 30 находиться в разных состояниях и на выходе элемента 7 неравнозначности появится сигнал 1 . В том случае, -если разность чисел в старших разрядах не удовлетворяет требованиям разности чисел третьего типа, т.е. в старших разрядах разности содер>хится хотя бы один ноль, то это приведет к появлению сигнала 1 на инверсном выходе сумматора 1,которым будет измене-щ но состояние тригерра 3 с нулевого на единичное. Поэтому к моменту опроса оба триггера 2 и 3 окажутся в состоянии 1 и на выходе элемента 7 неравнозначности в момент опроса будет сиг-45 нал 0, что свидетельствует о неравенстве чисел.

По сравнению с известными устройствами сравнения чисел предлагаемое устройство позволяет экономными средствами сравнивать с заданным допуском между собой числа, которые входят в множество чисел, имеющих замкнутую числовую ось, как например, кодированные числа в преобразователях уголкод .

Формула изобретения

Устройство для сравнения двоичных чисел, содержащее триггеры, последовательный сумматор, элемент неравнозначности, элементы И, о т л и ч а ющ е е с я тем, что, с целью расширения диапазона кодов сравниваемых чисел за счет обеспечения сравнения чисел, заданных циклическим кодом, в нем информационные входы последовательного сумматора подключены к входным шинам сравниваемых чисел, прямой ° выход последовательного сумматора соединен с первым входом установки в единичное состояние первого триг гера, второй вход установки в единичное состояние которого подключен к выходу первого элемента И, соединенному с первым входом установки в нулевое состояние второго триггера, вто. рой вход. установки в нулевое состояние которого подключен к выходу второго элемента И, соединенному со входом установки в нулевое состояние первого триггера. инверсный выход пос ледовательного сумматора подключен ко входам установки в единичное состояние второго и третьего триггеров, инверсный и прямой выходы третьего риггера соединены соответственно с ервыми входами первого и второго элеентов И, вторые входы которых подключены к шине управления; прямые выходы первого и второго триггеров соединены со входами элемента неравнозначности, а входы установки в Нулевое состояние последовательного суммато.ра и третьего триггера подключены к шине начальной установки.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 485445, кл, G Об F 7/04, 03.01.74.

2. Авторское свидетельство СССР

Р 4б8237, кл. G Об F 7/02, 02.01.74

Составитель В . Белкин

Редактор В. Павлов Техред М.Келемеш Корректор .Г. Решетник

Заказ 6767/48 Тираж 780 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д . 4/5

Филиал ППП Патент, г. Ужгород, ул . Проектная, 4