Параллельный комбинационный сумматор

Иллюстрации

Показать всеРеферат

«5,, !с, 1

ЕЛТЕЬ.„

О C И Е

ИЗОБРЕТЕНИЯ

Союз Советских

С щиалистических

Республик

Ж б

К АВтО СКОМУ СВИДЕтеЛЬСте (б1) Дополнительное к авт. свид-ву (22) Заявлено 240877(21) 2519171/18-24 (51) М. Кл. с присоединением заявки М (23) Приоритет

G 06 F 7/385

Государственный комитет

СССР но делам изобретений н открытий

Опубликовано 05,11.79. Бюллетень HB 41

Дата опубликования описания 051179 (53) УДК 681.325..5 (088.8) (72) Авторы

В. И. Корнейчук, В. П. Тарасенко и В. Х. Цонев

Киевский политехнический институт им, 50-летия Великой

Октябрьской социалистической революции (71) Заявитель (54) ПАРАЛЛЕЛЬНЫЙ КОМБИНАЦИОННЫЙ СУММАТОР

Изобретение относится к вычислительной технике и может приме-: няться в арифметических устройствах цифровых вычислительных машин .. 5

Известны параллельные комбинационные сумматоры (1), а также сумматоры с контролем и обнаружением ошибок (2), (3), (4), Недостаток таких схем — их плохая диагностицируемость, выражающаяся в большом числе входных наборов, необходимых для полной диагностики сумматора .

Наиболее близким по технической сущности является параллельный комбинационный сумматор, состоящий из и одноразрядных сумматоров, входы слагаемых.которых подключены попарно к входным шинам сумматора, а выходы суммы — к выходным шинам сумматора, вход переноса одноразрядного сумматора .младшего разряда сумматора подключен к входной шине переноса (5).25

Недостатком этого сумматора является то, что для полной диагностики необходимо подавать 2 " " входных наборов, а это связано с большими затратами машинного времени.

Цель предлагаемого изобретения улучшение диагностицируемости сумматора .

Для этого в сумматор введены элементы И, ИЛИ, НЕ и ИЛИ-НЕ, выходы переносов одноразрядных сумматоров подключены к первым входам элементов

И переноса, вторые входы которых подключены к дополнительной входной шине, а их выходы подключены к первым входам элементов ИЛИ переноса, выходы которых соединены со входами переносов одноразрядных сумматоров последующих разрядов, а вторые входы элементов ИЛИ переноса, за исключением элемента ИЛИ переноса старшего разряда, подключены к выходу первого элемента И, первый вход которого соединен с входом переноса младшего разряда сумматора, а второй — с выходом элемента НЕ, вход которого соединен с дополнительной входной шиной, ко второму входу элемента ИЛИ переноса старшего разряда сумматора, подключен выход второго элемента И, один вход которого подключен к выходу элемента НЕ, а другой - к выходу элемента ИЛИ, первый вход которого подклю- чен к выходу третьего элемента И, 696447 входы которого подключены к выходам переносов всех одноразрядных .сумматоров, второй вход элемента ИЛИ подключен к выходу элемента ИЛИ-HF., в>:оды которого также соединены с выходами переносов всех одноразрядных сумматоров.

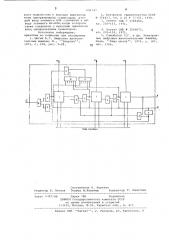

На чертеже приведена схема предлагаемого параллельного комбинационного сумматора.

Схема содержит и полных однораз— рядных сумматоров 1, выходы переносов которых подключены к первым входам элементов И 2 переноса, вторые входы которых соединены с дополнительной входной шиной 3. Выходы элемен- 1с тов И 2 подключены к первым входам элементов ИЛИ 4 переноса, вторые входы которых, за исключением элемента

ИЛИ 4 старшего разряда, соединены с выходом элемента И 5, первый вхоц которого соединен со входом переноса младшего разряда b, а второй с выходом элемента HE 7. Ко второму z>.оду элемента ИЛИ 4 старшего разряда, подключен выход элемента И 8. Выходы элементов ИЛИ 4 подключены ко входам переносов старших разрядов, Если для полной проверки и-разрядного сумматора необходимо подавать на входы 2 " наборов (2n входов :0

2>>+ 4 слагаемых.и один вход переноса младшего разряда), то для полной проверки одноразрядного полного суммато,а необходимо подавать 2 входных наборов (два информационных входа и один вход переиоса) . Поскольку связ-о между отдельными одноразрядными сумматорами прерывается при подаче на шину 3 логического 0, на них мо>кно подавать одни и те же входные 40 наборы. При этом элементы И 10 и НЕИЛИ 11 фиксируют равенство выходных сигналов переносов всех одноразрядных сумматоров. Если же переносы должны быть равны 0, то на выходе элемента И 10 имеется 0, а на выходе элемента ИЛИ-НЕ 11- 1 . >Эта единица через элементы ИЛИ 9, И 8 и

ИЛИ 4 появится на выходе сумматора

12. В случае, если на одном или нескольких входах переносов сигнал.не равняется 0, на выходе 12 появится 0 . Таким образом, будет установле,на ошибка при формировании переносов. Аналогично, если на всех выходаМ одноразрядных сумматоров долж- 55 на быть логическая 1, на выходе элемента НЕ-ИЛИ ll будет сигнал 0, а на выходе элемента И 10 — сигнал 1, который также появится на выходе 12. Если, имеет место ошибка в каких-то разрядах, то на выходе элемента И 10, а, следовательно, и на выходе 12 будет логический 0 .

Этим ошибха буцет обнаружена. Ошибки при формировании oóìì обнаруживают— ся на выходах 13 сумм одноразря,цных сумматоров .

Итак, н результате подачи 2 входных наборов обнаруживаются все ошибки при формировании переносов и сумм в одноразрядных сумматорах. При этом предполагается, что неисправностей в дополнительно введенных схемах не может быть, хотя некоторые из них могут быть обнаружены.Это ограничение не так существенно, потому что путем подачи нескольких дополнительных наборов все неисправности в этих схемах могут обнаруживаться (число их в любом случае не зависит от разрядности сумматора п) .

Таким образом, за счет введения в

«:остав сумматора дополнительного обо,:удо ания (около ЗС-o), количество вхоцчых наборов для полной проверки

2»-л сумматора уменьшается в 2 раз, а следовательно, во столько же раз, меньша.етс я и время, затрачиваемое па диагностику. Кроме тoro, значительIp упрощается диагностииирующее устpoAcòâo. Если схема сумматора выпол—

-.:åíHàÿ на БИС, то для этого необходим только один дополнительный внешний вывод.

Формула изобретения

Параллельный комбинационный сумм .то;-., состоящий из и одноразр.-.-дных с у:г..агоров, входы слагаемых которых подключены попа; но к входным шинам сумматора, а ьы>;оды суммы — к выход->ы: инам сумматора, вход пег еноса одноразрядного сумматора младшего o зряда сумматора подключен к входнои шине переноса о т л и ч а ю шийся тем, Что, с целью улучшения днагностицируемости сумматора, в него ввецены элементы И, ИЗ И, ИЛИНЕ, выходы переносов одноразрядных сумматоров подключены к первым входам элементов И переноса, вторые входы которых подключены к дополнительной входной шине, а их выходы

;оцключены к первым входам элементов ИЛИ переносы, выходы которых соединены с выходами переносов одноразрядных сумматоров последующих разрядов, вторые входы элементов ИЛИ переноса, за исключением элемента ИЛИ переноса старшего разряда, подключены к выходу первого элемента И, первый вход которого соединен со входом переноса младшегб разряда сумматора, а второй — с выходом элемента

HF,, вход которого соединен с дополнительной входной шиной, ко второму входу элемента ИЛИ переноса старшего разряда сумматора, подключен выход второго элемента И, один вход которого подключен к выходу элемента НЕ, а другой — к выходу элемента ИЛИ, первый вход которого подключен к выхоцу третьего элемента И, входы кото696 47

Составитель В. Березин

Редактор Б. Павлов Техред. М.Келемеш Корректор Г. Решетник

Заказ 6767/48 Тираж 780 Подписное

ЦНИИПИ .Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП. Патент, r. Ужгород, ул. Проектная, 4 рого подклю.ены к выходам переносов всех одноразрядных сумматоров, второй вход элемента ИЛИ подключен к выходу элемента НЕ-ИЛИ, входы которого также соединены с выходами переносов всех одноразрядных сумматоров.

Источники информации, принятые во внимание при экспертизе

1. Шигин А.Г. Цифровые вычисли— тельные машины. М., Энергия, 1971, с. 218, рис. 9-28.

2, Авторское свидетельство СССР

Р 354413, кл. G 06 F 7/385, 1970.

3. Патент США " 3588484, кл. 235 — 153,971

4. Патент США Р 3596072, кл, 235 †1, 1971, 5. Самофалов К.Г . и др. Электронные цифровые вычислительные машины, Киев, Вища школа, 1976, с. 167, О оис. 112а,