Устройство для определения среднего значения случайного процесса

Иллюстрации

Показать всеРеферат

r М )Д

« : ф,. ° 1 °". ««««

"-.-. « Рз:= Ов Фтских

Г, йР,иалистииескик

Р1мпъ Ол<81, 0IIlИСАНЙЕ

ИЗОБРЕТЕННАЯ (61) Дополнительное к авт, свид-sy ь,. С ( "ое1 11еретееяяый коиктет а f P яа делаю кзобретеккй я вткРытнй (5М)М. Кл. (22) Зайалвио 150877 (21)? 524797/18-24

606 г 15/36

Р,. :1 ПОиормтет (5Ç) 4Ê 681, 3 (088,8) Опубликовано 05,11.79. Бюллетень М 41

Дата опубликования списания 08.11.79 (72",мгтс .р

Я.з О, а т и:..; й

Б.A.. Прянишников (71) ЗдявытОль (54) .УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ СРЕДНЕГО ЗНАЧЕНИЯ

СЛУЧАЙНОГО ПРОЦЕССА

Изобретение относится к .специализированным средствам вычислительно-. техники и предназначено для определения среднего значения стационарных эргодических случайных процессов.

Известно устройство, в котором оценка средчего значения определяется в соответствии со следующим рекуррентным соотношением х. и„= =х 1+ (х „- x п Д д) Однако при использовании этого устройства необходимо наличие априорной информации о частотных свойствах исследуемого процесса.

Наиболее близким по технической сущности к предложенному является устройство для определения среднего значения случайного процесса, содержащее усреднитель, выход которого подключен к первому входу блока вычитания, второй вход которого объединен с первым входом усреднителя и яв- 25 ляется входом устройства, блок коррекции сигнала, выход которого соединен со вторым входом усреднителя (2)., Однако это устройство имеет большое время анализа случайного процес-а, связанное с необходюлостью получения информации о величине мошности входного сигнала.

Цель изобретения — повышение быстродействия устройства.

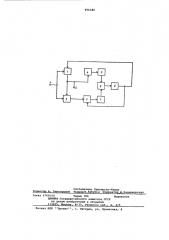

Для этого в устройство для определения среднего значения введены два формирователя модуля сигнала, дополнительный блок вычитания, блок формирования заданной погре чности и дополнительный усреднитель. Выход усреднителя через последовательно соединенные первый формирователь модуля сигнала и блок формирования заданной погрешности подключен к первому входу дополнительного блока вычитания, выход которого соединен со входом блока коррекции сигнала, выход которого подключен к первому входу дополнительного усреднителя, второй вход которого соединен с выходом блока вычитания. Выход дополнительного усреднителя через второй формирователь модуля сигнала подключен ко второму входу дополнительного блока вычитания, Структурная схема устройства представлена на чертеже.

Устройство содержит усреднитель 1, блок 2 вычитания, дополнительный ус-. реднитель 3, первый формирователь мо696480 дуля сигнала 4, блок 5 ФоРмиРованиЯ заданной погрешности, блок 6 коррекции сигнала, второй формирователь модуля сигнала 7, дополнительный блок вычитания 8. Первый вход усреднителя

1 объединен со вторым входом блока

2 вычитания и подключен ко входу устройства. Выход усреднителя 1 соединен со входами блока 2 вычитания и первого формирователя модуля сигнала 4, Первый вход дополнительного усреднителя 3 соединен с выходом блока 2, второй вход усреднителя 3 подключен к выходу блока 6 коррекции сигнала,а выход соединен со входом в" îðîãî dopмирователя модуля 7. Выход второго формирователя модуля 7 подключен ко д5 входу блока вычитания 8, другой вход последнего соединен с выходом блока формирования заданной погрешности 5, а выход подключен ко входу блока G коррекции сигнала, Выход блока 6 кop- . Рекции сигнала соединен со вторыми входами усреднителя 1 и дополнительного усреднителя 3, Выход первого формирователя модуля сигнала 4 подключен ко входу блока 5 Формирования заданной погрешности, Устройство работает сдТедующим Об-разом.

В начале работы устройства в усреднителях 1. и 3 устанавливается минимально возможная величина, сооТ.ветствующая наиболее высокочаcToTHo му диапазону работы устройства. Усреднители 1 и 3 могут быть выполне->r ны в виде RC-цепей или их цифровых аналогов. Входной сигнал усредняется на усреднителе 1 и полученной оценкой среднего значения грубо центрируется в блоке вычитания 2. Центрированный сигнал усредняется в допол- 4 д нительном усреднителе 3 и далее поступает на второй Формирователь модуля 7. Модуль оценки среднего значения, образованный в первом форми= рователе модуля 4, поступает на вход блока Формирования заданной погрешности 5, в котором по величине заданной Относительной погрешности dä формируется абсолютное значение допустимой погрешности Определения 50 среднего значения и в соответствии с выражением а= (х д, В блоке вычитания 8 формируется разность мдйкду модулем усредненного центрированного сигнала и абсолютным значением допустимой погрешности определения среднего значения. Блок 6 коррекции сигнала осуществляет формирование сигнала в соответствии с выражением ф д -д)qддpq=1 ы зи х! д и д "О Р д!

Сформированный сигнал осуществляет регулировку величины постоянных времени усреднения усреднителей 1 и 3. Усреднение центрированного сигнала на 65 дополнительном усреднителе 3 выявля-ет величину отклонения оценки среднего значения от его истинной величины, а последующее сравнение с величиной заданной погрешности определения среднего значения позволяет сфор-. мировать корректирующее воздействие для регулировки величины постоянных времени усреднения. После нескольких циклов корректировки устройство согласует свою постоянную времени усредн".Hèÿ с частотными свойствами исследуемого сигнала. Очевидно,. что априорной информации о частотных свойствах исследуемого процесса в дейком случае не требуется. Таким

Образом, изобретение позволяет повысить эффективность процесса получения среднего значения, заключающееся в уменьшении продолжительности процесса определения среднего значения, Обусловленном уменьшением необходимо. го Объема априорной информации о частотных свойствах исследуемого случайного процесса.

Формула изобретения

Устройство для определения среднего значения случайного процесса, содержащее усреднитель, выход которого подключен к первому входу блока вычитания, второй вход которого

Объединен с первым входом усреднителя и является входом устройства, блок коррекции сигнала, выход которого соединен со вторым входом усред" нителя, î -..л и ч а ю щ е е с я тем, что„ с целью повышения быстродействия, в него введены два формирователя модуля сигнала, дополнительный блок вычитания, блок формирования заданной погрешности и дополнительный усреднитель, при этом выход усреднителя через последовательно соединенные первый формирователь модуля сигнала и блок Формирования заданной погрешности подключен к первому входу дополн-. тельного блока вычитания, вьжод которого соединен со входом блока коррекции сигнала, выхсд которого подключен к первому входу дополнительного усреднителя, второй вход которого соединен с выходом блока вычитанияд выход дополнительного усреднителя через второй формирователь модуля сигнала подключен ко второму входу дополнительного блока вычитания.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 485455, ЙОб 7 15/Зб, 1974, 2. Патент США 9 3889108, кл. 806 У 15/Збр 1974.

69б 480

Составитель Григорьян-Чтани

Ре акт A. Виног ов Те К,Баб рка Корректо .Н.Задеряовская

Заказ б769/50 тираж 780 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035 Москва Ж-35 Ра ская наб 5

Филиал ППП Патент, г. ужгород, ул. Проектная, 4