Устройство для моделирования зоны нечувствительности

Иллюстрации

Показать всеРеферат

Союз Советскыи

Соцыалыстыческмк

Республык (61) Дополнительное н авт. свил-ву (22)Заявлено 16.05.78 (21) 2616334/18-24 (5е }М. К.п.

Q 06 g 7/26 с присоединением заявки И (23) Приоритет

Гваударстаенный иакитет

СССР

44 делам изобретений и Ртирктнй

Опубликовано 05.11.79. Бюллетень .1Й41

Дата опублнкованкя описания 08.11.79 (53) УЛ,К681.333 (088.8) (72) Авторы изобретения

В. И. Александрин, А. С. Алексеев и М. А. Чубаров

Научно-исследовательский институт прикладной математики и кибернетики при Горьковском государственном университете им. Лобачевского Н, И. (71) Заявитель (54) УСТРС::СТВО ДЛЯ МОДЕЛИРОВАНИЯ 3ОН61

НЕЧУВСТВИТЕЛЬНОСТИ

Изобретение относится к области аналоговой вычислительной техники и предназначено для специализированных вычислительных устройств на микроминиатюрных решающих усилителях постоянного тока (УПТ) .

Известно устройство (1 j для модели. рования звена с зоной нечувствительности при помощи решающих УПТ. Это устройство содержит типовые диодно-резисторные ячейки и УПТ с отрицательной обратной связью. Однако в таком устройстве при применении современных микроминиатюрных УПТ переход от зоны нечувствительности к зонам усиления недостаточно четкий.

Наиболее близким по технической сущности к изобретению является устройство, содержащее два УПТ, два делителя опорного напряжения идиоды (2). Точность работы такого устройства также недостаточна. 2О

Целью изобретения является повышение точности работы.

Эта цель достигается тем, что в устройство для моделирования зоны .нечувствительности, содержащее два делителя опорного напряжения, четыре диода, первый усилитель постоянного тока с резистором в цени обратной связи и двумя входными суммирующими резисторами, второй усилитель постоянного тока с входным резистором, один вывод которого соединен со входом устройства, а другой вывод — с инвертирующим входом усилителя, введен третий.-усилитель постоянного тока с входным резистором, один вывод которого соединен со входом устройства, а другой вывод — с инвертирующим входом третьего усилителя. Выход каждого делителя опорного напряжения подключен к неинвертирующему входу соответственно второгЬ и третьего усилителей постоянного тока. Неинвертирующий выход второго усилителя соединен с его инвертирующим входом через первый диод, включенный в прямом направлении, инвертирующий выход соединен с неинвертирующим входом через включенный в пря-. мом направлении второй диод. Неинвер696492 тирующий выход третьего усилителя соединен с его инвертируюшим входом через включенный в обратном направлении третий диод, инвертируюший выход - с неинвертирующим входом через четвертый диод, включенный в обратном направлении.

Входные суммирующие резисторы первого усилителя постоянного тока подкпюче4 напряжение более отрицательно, чем напряжение, поданное на "прямой" вход

УПТ 2, диод 6 закрыт, а диод 10 открыт. При этом в режиме с последовательной ООС находится усилитель 2, и входное напряжение устройства через резисторы 13, 12 поступает на второй вход УПТ 3. ны к инвертирующим входам соответствен. но второго и третьего усилителей.

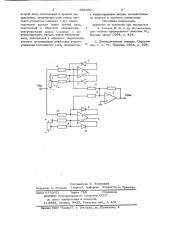

На чертеже показана принципиальная схема описываемого устройства.

Устройство состоит из двух балансных УПТ 1 и 2 с балансным входом и балансным выходом, являющихся ограни. чителями, и суммирующего УПТ 3. Между входом устройства и инвертирующим входом УПТ 1 включен резистор 4, между этим же входом УПТ и "прямым вы- gp ходом — диод 5 а между инвертирующим выходом и неинвертирующим входом диод 6.

Неинвертирующие входы УПТ 1 и 2 соединены соответственно с делителями 25 напряжений 7 и 8, задающими порог ограничения (ширину зоны нечувствительности). Соответствующие выходы УПТ 2 соединены; с его входами через диоды 9, 10. 30

Инверсные входы УПТ 1 и 2 соединены с входными суммирующими резисторами 11 и 12 УПТ 3. . Ограничтели имеют взаимно симметричные схемы и отличаются между собой 35 только полярностью напряжений ограничения и направлением включения диодов.

Устройство работает следующим образом.

Когда входное напряжение устройства 40 лежит внутри зоны нечувствительности, диоды 5 и 6 открыты, а диоды 9 и 10 закрыты. Усилители 1,2 находятся в режиме с параллельной отрицательной обратной связью (ООС), потейциалы их инверти:<> рующих входов остаются практически постоянными (потенциальный нуль ). Выходное напряжение устройства в этом случае не изменяется.

Если входное напряжение превышает

;напряжение, поданное на неинвертируюший вход УПТ 1„диод 5 закрыт, а диод 9 открыт УПТ 1 находится в режиме с последовательной обратной связью. В

55 этом случае его входное сопротивление весьма велико, и напряжение со входа устройства через резисторы 4 и 11 поступает на вход УПТ 3. Если входное. Благодаря большому внутреннему усилению усилителей 1 и 2 переход от режима параллельной OOC к режиму с последовательной ООС происходит при очень малом перепаде входного напряжения. В связи с этим переход от эоны нечувствительности к зонам усиления оказывается весьма резким и не зависит от формы вольт-амперной характеристики диода.

Кроме того, наличие нелинейной OOC позволяет избежать режима насыщения, и как следствие, получить достаточно высокое быстродействие устройства.

Экспериментальное исследование показало, что в предложенном устройстве переход от зоны нечувствительности к зоне усиления меньше нескольких милливопьт, а коммутационные помехи незначительны на частотах в несколько десятков килогерц.

Формула изобретения

Устройство дпя моделирования эоны нечувствительности, содержащее два делителя опорного напряжения, четыре диода, первый усилитель постоянного тока с резистором в цепи обратной связи и двумя входными суммирующими резисторами, второй усилитель постоянного тока с входным резистором, один вывод которого соединен со входом устройства, а другой вывод — с инвертируюшим входом усилителя, о т л и ч а ю щ е е с я тем, что, с целью повышения точности работы, в устройство введен третий усилитель постоянного тока с входным резистором, один вывод которого соединен со входом устройства, а другой вывод— с инвертирующим входом третьего усилителя, выход каждого иэ делителей опорного напряжения подключен к неинвертирующему входу соответственно второго и третьего усилителей постоянного тока, неинвертирующий выход второго усилителя соединен с его инвертирующим входом через первый диод, включенный в прямом направлении, инвертирующий выход соединен с неинвертирующим входом через

696492

Составитель В. Жовинский

Редактор Jl. Утехина Техред Л. Алферова Корректо » А. Гриценко

Заказ 6770/51 Тираж 780 Подписное

UHMNfIH Государственного комитета СССР по дела м и зобр ете ний и открытий

113035, Москва, Ж-35, Раушская наб„д. 4/5

Филиал ППП "Патент", г. Ужгород, ул, Проектная, 4 второй диод, включенный в прямом направлении, неинвертирующий выход третьего усилителя соединен с его инвертирующим входом через третий диод, включенный в обратном направлении, инвертируюший выход соединен с»еинвертирующим входом через четвертый диод, включенный в обратном направлении, входные суммирующие резисторы первого усилителя постоянного тока, подключены к инвертирующим входам соответственно втор oro и тр ет ь его усилит елей, Источники информации, принятые во внимание при экспертизе

1. Смолов В. B. и др. Вычислитель»ые машины непрерывного действия М., Высшая школа 1964, с. 434.

2. Вычислительная техника. Справочник, т, 1, М., Энергия, 1964, с, 204,