Устройство для моделирования нейрона

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

< и 696497 (61) Дополнительное к авт. саид-ву (22) Заявлено 140477(21) 2475658/18-24 (51)М. Кл.2

G G 7/60 с присоединением заявки М2

Государственный комитет

СССР но делам изобретений и открытий (23) Приоритет (53) УДК 681.333 (088. 8) Опубликовано 05.11.79. Бюллетень ) (о 41

Дата опубликования описания 05.11.79 (72) Авторы изобретения

К.Н.Дудкин и В.Е.Гаузельман (71) Заявитель

Ордена Трудового Красного Энамени институт физиологии им. И.П.Павлова AH СССР

{54) УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ НЕЙРОНА

Изобретение относится к области моделирования свойств биологических нейронов и может найти применение в радиотехнических системах, системах телеуправления, телеметрии и автоматики, а также в сенсорных системах роботов.

Известно устройство для моделирования нейрона, содержащее блок задания начальных условий, сумматор и блок памяти обучения (1).

Наиболее близким по технической сущности к предложенному изобретению 15 является устройство для моделирования нейрона, содержащее три канала, каждый иэ которых содержит интегратор, выход которого подключен к первому входу блока управляемой проводимости, выход блока управляемой проводимости третьего канала соединен со вторым входом блока управляемой проводимости второго канала, выход которого подключен ко второму входу блока управляемой проводимости первого канала, выход которого соединен со входом генератора потенциалов действия, выход которого является выходом устройства (2).

Недостатком известных устройств является низкая точность моделирования.

Цель .изобретения — повышение точности моделирования.

Укаэанная цель достигается тем, что в каждый канал устройства введены блок памяти обучения и блоки задания управляемых синаптичаских коэффициентов, первые входы которых являются входами устройства и подключены к входам блока памяти обучения своего канала, выходы которого соединены со вторыми входами бло-. ков задания управляемых синаптических коэффициентов своего канала, выходы которых подключены ко входам интегратора своего канала.

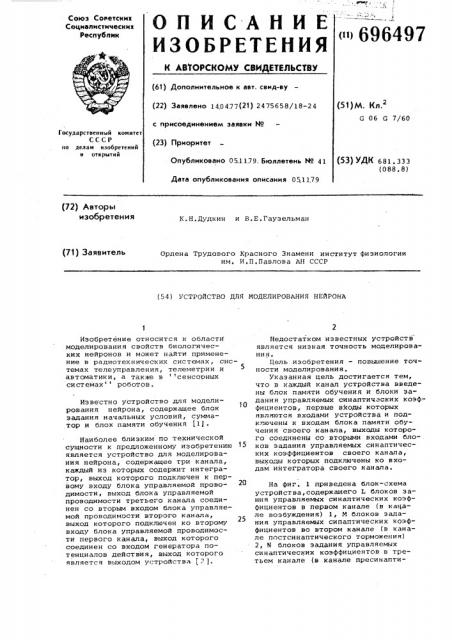

На фиг. 1 приведена блок-схеМа устройства, содержащего L блоков зания управляемых синаптических коэффициентов в первом канале (в кацале возбуждения) 1, М блоков задания управляемых сипаптических коэффициентов во втором канале (в канале постсинаптического торможения)

2, Н блоков задания управляемых синаптических коэффициентов в третьем канале (a канале пресинаптн696497 которой (R„C„) во много раз превышает постоянйые времени каналов возбуждения, торможения, растормаживания, (de синаптические коэффициенты блоков памяти обучения,8 16;>8> — пороги пороговых блоков 14 (фиг. 2) блоков памяти обучения, к.1(т) — ступенчатая функция, являющаяся выходным сигналом порогового блока 14 (фиг.2).

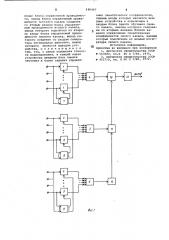

Поступающие по каждому входу импульсные последовательности интегрируются во времени на интеграторах в канале возбуждения, постсинап15 тического и пресинаптического торможения, и, кроме того, параллельно поступают на интеграторы 15 (фиг.2) блоков памяти обучения.

Здесь они интегрируются с большой постоянной времени (уравнения 4- .6) .

Выход интегратора 15 P(t) поступает на вход порогового блока 14 и параллельно на элемент ИЛИ 16, выходной сигнал которого служит для управления синаптическим коэффициен25 том 4J . При достижении сигналом

Р/ ) порогового значения 8 на выходе порогового блока 14 (фиг.2) появляется сигнал к ° 1(t), во много раз превышающий амплитуду сигнала

30 P (t), и на выходе элемента ИЛИ 16 устанавливается потенциал, равный по величине к 1(t). где L, М,К вЂ” число возбуждающих, 35 тормозных и растормаживающих входов нейрона соответственно ф(1),gP) („(<) весовые функции возбуждающих, тормозных и растормаживающих входов, И;(),и.(1), u„(<) — управляемые синаптические коэффициенты,Хф, х1,Х.„„- 40 сигналы, поступающие на -й возбуждающий, р -й тормозной, к-й растормаживающий входы.

Сигналами управления для коэффициентов и (t ) являются выходные сиг- 45 налы блоков памяти обучения 7, 8,9:

t р ()- g (t-A) p „(л)ал ч p (t) 8, р Р %1

50 т ри Р () 8

gpss P (t)(8 (М

p (t) >.e, ттри Р (t)CB> (g)

60 при Р (t))qg>, p (t) =x ) (t) ческого торможения) 3, интеграторы 4-6 в каналах возбуждения, постсинаптического и пресинаптического торможения соответственно, блоки

7-:9 памяти обучения в каналах возбуждения, постсинаптического и пресинаптического торможения соответс венно, блоки 10-;12 управляемой проводимости в каналах возбуждения, постсинаптического и пресинаптического торможения, генератор 13 потенциалов действия. На фиг. 2 представлена схема формирования кратковременной и долговременной памяти по одному из синаптических входов в одном из каналов устройства.

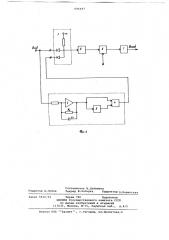

Работает устройство следующим образом. Поступающие по каждому входу импульсные последовательности интегрируются во времени на интеграторах 4-:6. Суммарный возбуждающий потенциал Е (t) подаваемый на вход генератора потенциалов действия 13, тормозной потенциал I(t.) и растормаживающий 9 (t) описываются уравнениями:

t g, К(Ц= f С @(а-), r(a)j;(e.-Л,Р,(Л))х,,й)Ы ()

-oo 7 f

t м

gt) = f . . (t, ДД(ЛЦ (t-ЛР-(ЯЦХ .gË)c(À,(2)

М

D(t) =f Е: f„(t A) „(t.-ЛДЙ))х Q)dA,(з)

ОО

Р,(t) =К. 1(t)

Е

Р, (t) j р (Ф. Л) 6) хz° . (A)(A

Р, (+) - К <(t) т р „(t)= $,(-л) ), В) (л где фР— весовая функция блока памяти обучения, постоянная времени

Блок задания управляемого синаптического коэффициента 1 работает следующим образом. При отсутствии входного сигнала х(1) или при одиночных импульсах синаптический коэффициент< ) блока 1 равен О, так как блок 1 представляет собой элемент И, на выходе которого сигнал будет тем больше, чем больше управляющий сигнал с выхода элемента ИЛИ 16. Коэффициент передачи имеет .наибольшее значение при наличии на выходе элемента ИЛИ 16 сигнала к .1 (t) .

Наличие сигнала к ° 1(t) имитирует долговременную память. Этот сигнал появляется в случае наличия на входе часто повторяющихся сигналов x (t) .

Кратковременную память определяет амплитуда сигнала Р (t) которая также формируется в блоке памяти обучения.

Введение новых структурных элементов обеспечивает моделирование кратковременной и долговременной. памяти, что повышает точность моделирования °

Формула изобретения устройство для моделирования нейрона, содержащее три канала, каждый иэ которых содержит интегратор, выход которого подключен к первому

6 96497 входу блока управляемой проводимости, выход блока управляемой проводимости третьего канала соединен со вторым входом блока управляемой проводимости второго канала, выход которого подключен ко второму входу блока управляемой проводимости первого канала, выход которого соединен со входом генератора потенциалов действия, выход которого является выходом устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения точности моделирования, в каждый канал устройства введены блок памяти обучения и блоки задания управляемых синаптических коэффициентов, первые входы которых являются входами устройства и подключены к входам блока памяти обучения своего канала, выходы которого соединены со вторыми входами блоков задания управляемых синаптических коэффициентов своего канала, выходы которых подключены ко входам интегратора своего канала.

Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР

9 563680, кл.G 06 G 7/60, 1975, 2 ° Авторское свидетельство СССР

М 453710, кл, G 06 G 7/60, 1972.

696497

Составитель Н. Дубинина

Техред Н. Бабчрка Корректор К

О.Ковинская

Редактор Д.Зубов

Заказ 6810,/61

Тираж 780 Подписное

ЦИНИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Филиал ППП Патент, г.Ужгород, ул.Проектная,4