Запоминающее устройство

Иллюстрации

Показать всеРеферат

Союз Советских

Социапистических

Республик в п -т ..

"" 4Л .)(щ „ (61) Дополнительное к авт. свид-ву— (22) Звявлено 01.0777(21) 2501832/18- 24 с присоединение. заявки №

G 11 С 11/00

Государственный комитет

СССР по делам изобретений и открытий (23) Приоритет— (S3) УДК 681. 327. 6 (088. 8) Опубликовано 05.1179. Бюллетень ¹ 41

Дата опубликования описания 08-11.79 (72) Авторы изобретения

Ю.Г. Бостанджян и Д.Е. Перельмутер (71) Заявитель (54 ) ЗАПОМИНАЮЦЕЕ УСТРОЙСТВО

Изобретение относится к области запоминающих устройств и может быть использовано в запоминающих устройствах (ЗУ) с разрядностью ячеек памяти лва и более байтов, каждый из которых 5 остоит из восьми информационных бит и одного контрольного бита, дополняющего количество единичных бит в байте до нечетного.

Одно из известных запоминающих 10 у тройств состоит из блока хранения информации в прямом или инверсном коде, триггера инвертирования, выход которого соединен с входными вентилями„ выход которых соединен с блоком хра- 15 кения информации, и выходных вентилей, вход которых соединен с выходом блока хранения информации (1).

Однако, в этом ЗУ для указания ница хранимого кода используется допол- 20 нительный разряд в каждой ячейке памяти, что увеличивает объем ЗУ.

Яаиболее близким по технической сущности к предложенному является запоминающее устройство, содержащее ре- 25 гистр числа, входы которого подключены к входным информационным шинам и к выходам накопителя, а единичные и

Нулевые выходы регистров числа во всех разрядах, кроме одного, соедине- 30

2 ны с соответствующими информационными входами входных и выходных элементов 2 И-ИЛИ, выходы которых подключены соотнетственно ко входам накопителя и выходным информационным шинам.

Управляющие входы входных элементов

2 И-ИЛИ соединены с соотнетстнующими выходами логического блока, входы которого подключены к входным информационным шинам и одной из управляющих шин (2), Однако, в этом ЗУ также необходи<о использовать дополнительный разряд в каждой ячейке памяти для указания нида хранимого кода, что уменьшает информационную емкость ЗУ.

Цель изобретения — увеличение информационной емкости устройства.

Это достигается тем, что устройство содержит дополнительный логический блок, входы которого соединены с выходами регистра числа и другой управляющей иной, выходы — с управляющими входами выходных элементов 2 И-ИЛИ.

Нулевой и единичный выходы регистра числа в одном из разрядов подключены ко входам соответствующих входного и выходного элементов 2 И-ИЛИ иннерсно по отношению к другим разрядам.

696541

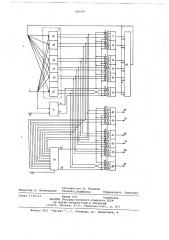

На чертеже представлена структурна я схема з а помина юще го устрой стн а.

Входные информационные шины 1 соединены с логическим блоком 2, служащим для анализа количества единичных бит в слове, и с входами регистра 3 числа. Выход 4 блока 2 соединен с. управляющими входами 5-10 входных элементов 2 И-ИЛИ ll 16, Выход 17 блока

2 соединен с управляющими входами 1823 этих же элементов, Единичные выходы триггеров 24-28 регистра 3 числа соединены с единичными информационными входами 29-33 входных элементов

2 И-ИЛИ 11-15, с единичными информационными входами 34-38 выходных элементов 2 И-ИЛИ 39-43 и с дополнительным логическим блоком 44, сл ужащим для анализа считанной информации. Нулевые выходы триггеров 24-28 регистра

3 числа соединены с нулевыми информа- 2О ционными входами 45-49 входных элементов 2 И-ИЛИ 11-15, с нулевыми информационными входами 50-54 выходных элементов 2 И-ИЛИ 39-43 и с входами блока 44.Единичный выход триггера 55 25 (контрольный разряд второго байта) .регистра 3 числа соединен с нулевым информационным входом 56 входного элемента 2 И-ИЛИ lб,с.нулевым информационным входом 57 выходного элемента 3()

2 И-ИЛИ 58 и с блоком 44. Нулевой выход триггера 55 регистра 3 числа соединен с информационным единичным вхо- . дом 59 входного элемента 2 И-ИЛИ 16, с единичным информационным входом 60 35 выходного элемента 2 И-ИЛИ 58 и с входом блока 44, т,е. инверсно по отношению к другим триггерам (разрядам)

Выходы входных элементов 2 И-ИЛИ 1116 соединены с накопителем 61 выход щ которого соединен с входами регистра

3 числа и с входом регенерации самого блока 61. Выход 62 блока 44 соединен с управляющими входами 6 3-6 8 выходных элементов 2 И-ИЛИ 39-43 и 58.

Выход 69 того же блока 44 соединен с управляющими входами 70-75 выходных элементов 2 И-ИЛИ 39-43 и 58, а выходы этих элементов соединены с выходными информационными шинами 76-81. Входы блоков 2 и 44 соединены с управ— ляющими шинами 82 и 83 соответственно. Анализируя работу устройства при записи и чтении информации, например, с меньшим количеством единичных бит, необходимо отметить следующее: 55

-так как любое нечетное число можно предстанить в виде сумьы двух чисел, из которых одно нечетное, à другое четное, то н любом девятиразрядном байте с нечетным количеством еди- 60 ничных бит всегда будет четное коли— честно нулевых бит;

«при инверсии вышеуказанного дев я тира зрядного байта получится четное количество единичных бит (инверсия 65 нулей) и нечетнОе количество нулевых бит (инверсия единиц); — если н девятиразрядном байте, представленном в прямом коде, инвертировать любой из битов, то количест-. во единичных бит станет четным, а ну левых — нечетным;

-если в денятиразрядном байте, представленном в обратном коде (инверсном), инвертировать любой из битов, то количество единичных бит станет нечетным, а количество нулевыхчетным.

Устройство работает следующим образом, Пусть на входные информационные шины 1 в режиме записи поступит информация 000000111 000000111 (два байта) . Эта информация занесется в регИстр 3 числа и одновременно поступит на вход блока 2. Так как количество единичных бит в этом слове меньше количества нулевых бит, то при поступлении команды Запи -b на шину 82 на выходе 4 блока 2 появится сигнал, который поступит на входы 5-10 входных элементон 2 И-ИЛИ

11 -16 и разрешит передачу информации с единичных выходов триггеров 24.-28 и с нулевого выхода триггера 55(контрольный разряд второго байта регистра 3 числа) в накопитель 61. Учитывая вышесказанное, в накопителе 61 первый байт будет состоять из нечетного количества единичных бит и четного .нулевых, а второй байт — из четного количества единичных бит и нечетного количества нулевых бит (000000111 000000110), Передача информации из регистра 3 числа на выходные информационные шины 76-81 блокируется отсутствием сигналов на выходах 62 и 69 блока 44. При подаче на шину 83 команды чтение считанная информация из накопителя 6» зане.сется в регистр 3 числа. Так как в хранящейся информации первый байт имеет нечетное количество единичных бит, а второй — четное, то на выходе

62 блока 44, при наличии команды чтение, появится сигнал, который поступит на входы 63-68 выходных эле» ментов 2 И-ИЛИ 39-43 и 58 и разрешит передачу информации на выходные информационные шины 76-81 с единичных выходов триггеров 24-28 и нулевого выхода триггера 55 (контрольный разряд. второго байта) регистра числа 3. Таким образом, при передаче информации на ныходные информационные шины 76-81 инвертирование контрольного разряда второго байта вызовет появление на этих шинах исходной информации, .поступившей в режиме записи на входные информационные шины 1. Передача информации из регистра 3 числа в накопитель

61 будет блокирована отсутствием сигналон на выходах 4 и 17 блока 2.

6965 41

Из рассмотрения работы устройств можно сделать следующие выводы

-если в считанной из накопителя информации первый байт имеет нечетное количество единичных бит, а второй байт — четное, то информация считана в прямом коде, за исключением контрольного разряда второго байта, для получения исходной информации необходимо инвертировать содержимое этого бита; 10 если в считанной из накопителя информации первый байт имеет четное количество единичных бит, а второй байт — нечетное, то информация считана в обратном коде, за исключением контрольного разряда второго байта, для получения исходной информации необходимо инвертировать содержимое всех битов, кроме контрольного разряда второго байта;

-одинаковая четность двух байтов свидетельствует об одиночном сбое устройства.

Изобретение может быть распространено на устройство с большим числом байтов, причем вместо контрольного разряда можно. использовать любой разряд любого байта.

Основным преимуществом изобретения является экономия оборудования за счет уменьшения разрядности ячеек па". Зц мяти (или увеличения эффективной емкости устройства). Это цозволяет использовать его в запоминающих устройствах с многобайтовой структурой ячеек памяти, в которых информация 35 хранится в прямом и обратном коде.

Формул а и зо брет ени я

За поми н ающее устройство, содержа— щее регистр числа, входы которого под ключ е ны к в х од ным и н фор маци он ным шинам и к выходам накопителя, а единичные и нулевые выходы регистров числа во в сех разрядах, кроме одного, соединены с соответствующкчи информационными входами входных и выходных элементов 2 И-ИЛИ, выходы которых подключены соответственно ко входам накопителя и выходным информационным шинам, а управляющие входы входных элементов 2 И-ИЛИ соединены с соответствующими выходами логического блока, входы которого подключены к входным информационным шинам и одной из управляющих шин, о т л и ч а ю щ в ес я тем, что, с целью увеличения информационной емкости устройства, оно содержит дополнительный логический блок, входы которого соединены с выходами регистра числа и другой управляющей шиной, выходы — с управляющими входами выходных элементов

2 И-ИЛИ, а нулевой и единичный выходы регистра числа в одном из разрядов подключены ко входам соответствующих входного и выходного элементов

2 И-ИЛИ инверсно по отношению к другим разрядам.

Источники информации, принятые во внжлание при экспертизе

1. Патент СНА 9 3579210, 340 †1, 1971.

2. Патент США Р 3681764, 340-172,5, 1972 (прототип) .

596541

Заказ 6 776/53

Тираж 681 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушсхая наб., д. 4/5

Филиал ППП Патент, г. ужгород, ул. Проектная, 4

Состав ит ель В, Рудаков

Редактор А. Виноградов Техред Л,Алферова Корректор A. Гриценко