Запоминающее устройство

Иллюстрации

Показать всеРеферат

ОП ИСА Й И E

ИЗОБРЕТЕНИЯ

Союз Советскнк

Социалистических

Республик

<1 696542

Х АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (б1) Дополнительное к авт. свид-ву (22) Заявлено 031077 (21) 2582061/18-24 (51) M. -Кл. с присоединением заявки ¹

G 11 С 11/00

Государственный комитет

СССР по делам изобретений и открытий (23) Приоритет— (53) УДК 681. 327. 6 (088.8) Опубликовано 0511.79 Бюллетень ¹ 41

Дата опубликования описания 08.11.79 (72) Авторы изобретения

A. Ï. Кумекин и Н.П. Попов (71) Заявитель (54 ) ЗАПОМИНАЮЩЕЕ УСТРОИСТВО

Изобретение относится к области вычислительной техникие в частности к запоминающим устройствам (ЗУ) с накопителями, выполненными на многоотверстных ферритовых пластин ах. 5

Известно запоминающее устройство (ЗУ), сЬдержащее накопители, адресный блок, блок синхронизации, блок выделени я информации блок э а пи си инфорI

1О мации, при этом накопители и усилители записи-считывания включены по мостовой схеме с целью компенсации помех от записи, запись 1 производится в разные накопители импульсами противоположной полярности (1).

Наиболее близким техническим решением к данному изобретению является запоминающее устройство, содержащее накопители, одни из входов-выходов которых подключены к одному из входов формирователя записи-считывания числа, другие вхоцы которого подключены к одному из выходов блока синхронизации и к выходу дешифратора адреса, первый и второй входы которого подключены соответственно к выходам элемента 11Е и элемента ИЛИ, входы которого соединены с выходами триггера и выходной шиной, и выходом элемента И, один из входов которого под- 30 ключен к соответствующей входной шине, другой — к шине записи и одному из входов блок а синхронизации, другие входы блока синхрони э ации Соединены с шинами обращения и считывания, соответствующие выходы блока синхронизации соединены с одним из входов адресного блока и со вторым входом триггера, первый вход которого соединен с выходом формирователя записисчитывания числа, входы-выходы которого соединены с coorsетствующими входами-выкадами накопителей, входы которых подключены к выходам адресного блока, входы которого подключены к управляющим шинам и входу элемента

НЕ (2) .

Недостатком известных устройств является то, что в них при считывании информации происходит регенерация той информации, которая считйвается. Иногда, например, при применении ЗУ в устройствах регистрации, необходимо после считывания информации производить обнуление Зу. В известных устройствах обнуление производится в цикле эа писи, что снижает быстродействие ЗУ.

Цель изобретения — повышение быст— ропействия Зу, 696542

Поставленная цель достигается тем, что запоминающее устройство содержит три элемента И, три элемента ffE u дополнительный элемент ИЛИ, ныход которого соединен с третьим входом дешифратор адреса, а входы — с выходами первого и второго элементов И, первые входы которых соединены соответственно с первым входом дешифратора ацреса и с соответствующим Вхо дом адресного блока, вторые входы первого и второго элементов И соединены соответственно с входом перного элемента НЕ, выходом третьего элемейта И, и выходом первого элемента НЕ, входы третьего элемента И соецинены с .выходами второго и третьего элементов

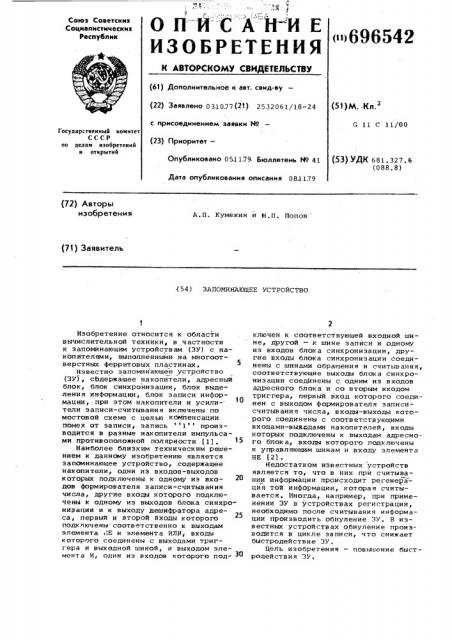

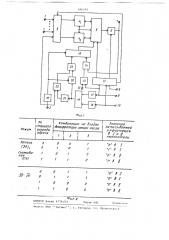

8E„ входы которых подключены к шинам записи и считывания, На фиг. 1 представлена блок-схема запоминающего устройстна для одного разряда числа," на фиг. 2 показано значение записываемой информации, получаемой на выходы дешифратора записи числа, в зависимости от кодовых комбинаций числа в различных режимах работы ЗУ.

Запоминающее устройство содержит управляющие шины 1,2, подключенные к адресному блоку 3, выходы которого соединены с входами накопителей 4, 4, формирователь 5 записи-считывания числа соединен по мостовой схеме с накопителями 4(, 4, выход формирователя записи-считывания 5 подключен к первому входу триггера 6 регистра числа, выход .которого соединен с выходной шиной 7 числа. Нина обращения

8, шина записи 9, шина считывания 10 подключены к блоку синхронизации 11, выходы которого соединены с входом блока выделения адреса 3, с управляющим выходом формирователя 5 записи-считывания числа и со вторым входом триггера б. ° Шина записи 9 и входная шина числа 12 через элемент И 13, а выходная шина 7 непосредственно подключены к входам элемента ИЛИ 14, Выход элемента ИЛИ 14 соединен с первым входом деиифратора адреса 15, первый вход которого соединен с выходом элемента НЕ 16 и через него— с управляющей шиной 2, Шина записи

9 подключена к входу элемента HE 17, шина считывания 10 — к входу элемента HE 18. Выходы элементов НЕ 17, 18 подключены к входам элемента И 19, выход которого соединен с входом элементов И 20 и входом элемента

НЕ 21, Один из входов элемента И 20 подключен к первому входу дешифратора записи числа 15 и выходу элемента НЕ 16. Выход элемента НЕ 21, вход элемента HE 16 и управляющая шина 2 подключены к входам элемента И ?2.

Выходы элементов И 20 и 22 соединены с входами дополнительного элемено та ИЛИ 23, -выход которого подключен к третьему входу дешифратора 15, В Режиме считывания информации по шинам 1 и 2 н блок 3 поступает адрес. При этом, если старший раз5 ряд адреса имеет значение . 0, то выбирается ячейка накопителя 4 (см.фиг.2), если значение 14 — то ячейка накопителя 4 . В режиме считывания на входы ЗУ кроме адреса поIO .ступает признак считывания по шине

10 и обращение по шине 8. По шине записи 9 элемент И 19 закрыт и сигналом с элемента НЕ 21 открыт элемент

И 22. Старший разряд адреса посту15 пает в виде прямого кода (ПК) через элемент И 22, далее через элемент

ИЛИ 23 на третий вход дешифратора

15 записи числа, на первый вход которого поступает обратный код (0K) старшего разряда адреса с выхода элемента НЕ 16 °

Блок синхронизации 11 вырабатывает строб для блока 3, импульсы сброса и приема в регистр числа, а так же строб записи для регенерации.

По переднему фронту строба ДШ про- . изводится считывание информации из

4 или 4 накопителя, формирование ее до необходимого уровня в формиро вателе 5 записи-считывания и прием в триггер б числа. Число с триггера б поступает на выход по шине 7. и через элемент ИЛИ 14 на дешифратор 15 записи числа, который в зависимости

З5 От значения информации старшего разряда адреса, формирует число в соответствии с таблицей (см. фиг.2).

- По стробу записи, поступающему на управляющий вход формирователя

5, формируется разрядный ток соот40 ветствующего накопителя, который либо складывается с током от ныборки адреса по заднему фронту страбон Д1Я и тогда записывается 1, либо вычитается из него и тогда записывает45 ся 0 . Это происходит с рабочим сердечником накопителя. В компенсационном сердечнике (на хранение одного бита информации используется

2 сердвч) происходит обратное:

5Q при сложении токов происходит запись 0 и при вычитании-запись 1 .

В режиме записи число в трйггер регистра б не принимается и.поступает на дешифратор 15. извне с эле55 мента И 13 по другому входу элемен-. та ИЛИ 14. Дешифратор 15 работает при этом как в режиме считывания (см, фиг. 2) .

В режиме считынания без рвгене60 Рации <Режим ЗП СЧ) в ЗУ поступает сигнал по шинам 1, 2 и 8, Блок синхронизации 11 вырабатывает сигналы, как и в режиме считывания, Тах жв по переднему Фронту строба д(л про65 исходит считывание информации, эя 9654? поминание ее в триггере 6 и выдача на выход 7. Запись числа по данному обращению происходит так же по стробу записи, однако дешифратор 1.5

Работает иначе, чем при считывании или записи. На первый и третий входы дешифратора 15 поступают не противоположные значения (на первый входОК старшего разряда, а на третий

ПК), как это было в режимах записи н считывания, а одинаковые сигналы сле- 10 дующим образом. При отсутствии сигналов записи и считывания на шинах 9 и

10 элемент И 19 вырабатывает сигнал разрешения на элемент И 20 и через элемент НЕ 21 сигнал запреra на элемент И 22 так, что OK старшего разряда адреса поступает с элемента НЕ 16 на первый вход дешифратора 15 непосредственно и на третий вход — через элементы И 20 и ИЛИ 23. По этим двум сигналам, независимо от того, что поступает на его числовой вход, дешифратор 15 вырабатывает 0 для записи в накопители 4 и 4 (см. фиг. 2).

Таким обРазом, введение в ЗУ незначительного .оборудования гозволяет

25 осуществить обнуление ЗУ в один такт с операцией считывания в режиме ЗП.СЧ, что равносильно увеличению быстродействия ЗУ.

Формула изобретения

Запоминающее устройство, содержащее накопители, одни из входов-выходов которых подключены к одному из входов формирователя записи-считыва; ния числа, другие входы которого подключены к одному из выходов блока синхронизации и к выходу дешифратора ад- 40 реса, первый и второй входы которого подключены соответственно к выходам элемента HE и элемента ИЛИ, входы которого соединены.с выходами триггера и выходной шиной, и выходом элемен- 45 та И; один из входов которого подключен к соответ< твующей входной шине, другой — к шине записи и одному из входов блока синхронизации, другие входы блока синхронизации соединены с шинами обращения и считывания, cooTBBTcTBующие выходы блока синхронизации соединены с одним из входов адресного блока и со вторым входом триггера, первый вход которого соединен с Bыходом формирователя 3апиcH — счиTbl вания числа, входы-выходы которого соединены с соответствующими входамивыходами накопителей, входы которых подключены к выходам адресного блока, входы которого подключены к управляющим шинам и входу элемента НЕ, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия устройства, оно содержит три элемента И, три элемента НЕ и дополнительный эле,мент ИЛИ, выход которого соединен с третьим входом дешифратора адреса, а .входы — с выходами первого и второго элементов И, первые входы которых соединены соответственно с первым входом дешифратора адреса и с соответствующим входом адресного блока, вторые входы первого и второго элементов И соединены соответственно с входом первогО элемента НЕ, выходом третьего элемента, И и выходом первого элемента НЕ, входы третьего элемента И соединены с выходами второго и третьего элементов НЕ, входы которых подключены к шинам записи и считывания.

Источнйки информации, принятые во внимание при экспертизе

1. Лашевский P.À. и др. Запоминающие устройства на многоотверсных ферритовых пластинах. M. Энергия, 1969, с. 7,73-76.

2. Авторское свидетельство СССР

9 498647, кл. 6 11 С 11/06 0674 (прототип).

696542

9 г.1 о

9 иг. 2

ЦИИИПИ Заказ 6 776 /5 3 Тираж бВ) Подии н <1е .Филиал ЛЛИ Патент, r. Ужгород, ул. Проек гиач, 4