Делитель частоты с автоматически изменяющимся коэффициентом деления

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

<" 696608 (61) Дополнительное к авт. саид-ву (22)Заявлено 14.07.77 (21) 2508515/18-21 с присоединением заявки Ж (23) Приоритет

Опубликовано 05.11.79 Бюллетень №41

Дата опубликования описания 08.11.79 (51 ) М. Кл.

Н 03 К 23/00

Гвсудврстввнный ивмвтвт

СССР вв делам извбрвтвиий и открытий (5Ç) УДК 621.374 (088.8) Р, А. Воробель, Т, Г. Галамай, В. Б. Дудыкевич и Б. A. Попов (72) Авторы изобретения

Физико-механический институт Академии наук Украинской ССР и Львовский ордена Ленина политехнический институт (71) Заявители (54) ДЕЛИТЕЛЬ ЧАСТОТЫ С АВТОМАТИЧЕСКИ

ИЗМЕ НЯЮШИМСЯ КОЭФФИБИЕ НТОМ

ДЕЛЕНИЯ

Настоящее изобретение относится к импульсной и вычислительной технике.

Известен делитель частоты, содержащий деи1ифратор, двоичный делитель частоты, реверсивный счетчик, блок записи параллельного кода, блок с ра вне ния, вычитающий счетчик, коммутатор и элементы И (1).

Недостатком его является низкое быстродействие и ограниченные функциональные возможности.

Наиболее близким по технической сущности является делитель частоты с автоматически изменяющимся коэффициентом деления, содержащий двоичный делитель частоты, схему записи параллельного кода, реверсивный двоичный счетчик, дешифратор и элементы И t2j.

Недостатком описанного устройства является большая длительность цикла его работы и ограниченные функциональные возможности.

Цель изобретения - сокращение длительности цикла работы делителя и расширение его функциональных возможностей.

С этой целью в делитель частоты с автоматически изменяющпмсч коэффициентом деления, содержащий двоичный делитель частоты, первый блок совпадения, управляющие входы которого соединены, непосредственно с разрядами реверсивного счетчика импульсов и через дешифратор — с первыми в<одами первого и второго элементов И, вторые входы которых соединены с выходом двоичного, делителя частоты, третьи - соответс1венно с шиной суммирование" и "вычитание", а выходы — со входами реверсивного счетчика импульсов, введены блок управления, второй блок совпадения, блок сложения-вычитания, первый вход которого подключен ко входу устройства, второй вход - к выходу первого блока совпадения, а выход — ко входу двоичного делителя частоты, выходы разрядов которого соединены с сигнальными входами первого и второго блоков совпадения, 696608 управляющие входы последнего из которых соединены с выходами блока управления, а выход является выходом устройства, при этом вход вычитание" реверсивного счетчика соединен с выходом 5 первого элемента И, а вход сложение"с выходом второго элемента И.

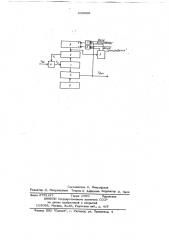

На чертеже представлена структурная электрическая схема делителя частоты с автоматически изменяющимся коэффи» циентом деления.

Делитель частоты с автоматически изменяющимся коэффициентом деления состоит из двоичнот"о целителя 1 частоты, блоков 2 и 3 совпадения, блока 4

15 сложения-вычитания, дешифратора 5, элементов 6 и 7 И, реверсивного счетчика

8 импульсов и блока 9 управления.

Разряды двоичного делителя 1 часто20 ты связаны с сигнальными входами блока 2 совпадения и блока 3 совпадения, управляющие входы которого соединены с выходами блока 9 управления, а выходс выходом устройства и вторыми входами элементов 6 и 7 И, третьи входы которых соединены с шинами "суммирование "и вычитание соответственно, а первые входы через дешифратор 5 с разрядами реверсивного сч@тчика 8 импульсов, соединенного входом "сложенная с выходом элемента 7 И, а, входом вычитание — с выходом элемента 6 И, и уп равляющими входами блока 2 совпадения, выходом соединенного co вторым входом блока 4 сложения - вычитания, первым входом связанного со входом устройства, а выходом - co входом двоичного делителя 1.

Делитель частоты с автоматически 40 изменяющимся коэффициентом деления работает следующим образом. (3) F2 Рвх«F, РФ

В исходном состоянии в реверсивном счетчике 8 находится код числа И=И, „-„, 45 соответствующий минимальному значению кода числа реверсивного счетчика, а на шику вычитание подан разрешающий потенциал, при котором элемент 7 И открыт. На первый вход блока 4. сложениявычитания поступает входной сигнал с частотой Fg, на второй вход - сигнал с частотой Г с выхода блока 2 совпадения. Поэтому, частота F сигнала на выходе блока 4 сложения — вычитания оп- 55 ределяется выражением

Так как двоичный делитель 1 с блоком 2 совпадения представляет собой двоичный умножитель частоты, управляемый кодом числа N реверсивного счетчика 8, то частота F<, на выходе блока

2 совпадения определяется выражением

F1 F — (4)

™ где N код числа реверсивного счетчичика 3;

М,«ря - коэффициент пересчета реверсивИ ного счетчика 3; тт количество двоичных разрядов реверсивного счетчика 3, Подставив (4) в. (3) получим

F =F +F -F.—

Х М (5) откуда . "м .F-ф (6)

Пусть, например, на выходы блока 3 совпадения поступает сигнал со входа двоичного делителя 1 частоты. Тогда;;тяпал с частотой F поступает через открытый потейциалом на шине "вычитание" элемент 7 И на вход сложения реверсивного счетчика 8, увеличивая при этом значение кода Й на единицу, что приводит к уменьшению выходной частоты F> в соответствии с (6). После того, как код реверсивного счетчика 8 примет значение соответствующее числу N =N тх, сигнал с дешифратора 5 запирает элемент

7 И и частота F не псступает на входы реверсивного счетчика 8.

При поступлении разрешающего потенциала на шину суммирование" открывается элемент 6 И и частота Fg с выхода блока 4 сложения вычитания через блок 3 совпадения и элемент 6 И поступает на вычитающий вход реверсивного счетчика 8, уменьшая его содержимое на единицу, что приводит к увеличению выходной частоты F . После того, как код реверсивного счетчика 8 примет значение И = М т„,..., сигнал с выхода дешифI ратора 5 запирает элемент 6 И и импульсы выходной частоты не изменяют содержимого реверсивного счетчика 8. Делитель придет в исходное состояние.

1Ь (6) следует, что длительность цикла работы Етт в описываемом делителе, когда на выход блока 3 проходит непосредственно сигнал с выхода блока

4, равна

696608 =а М +1 п 1И

u,". q м (7) где hN пах (wig

Сравнивая (2) и (7) видим, что в этом делителе частоты длительность цикла работы ц,,уменьшена в N paa.

Если на выход блока 3 проходит частота не с выхода блока 4 неуесредственно, а из выхода любого разряда двоичного делителя частоты, то длительность цикла работы 4, изменится.

Если, например, на выход второго блока 3 совпадения поступает частота с выхода блока 4 сложения - вычитания, то она равна в соответствии с (6)

В х " у, х„(8)

Vli а если на выход второго блока 3 совпадения поступает сигнал с выхода двоичного делителя 1, то с учетом (6)

Fр„

ВЬя N -ÿ (9) где и = 2 - коэффициент пересчета двоl1

М ичного делителя 1; и — количество двоичных разрядов двоичного делителя 1.

Следовательно, с учетом (8) и (9), с помощью блока управления можно изменять минимальную и максимальную частоты на выходе второго блока 3 совпадения, тем самым и на выходе делителя, в пределах

F ар р м

М

М вых — » (10) что существенно расширяет функциональные возможности делителя частоты с автоматически изменяющимся коэффициентом деления.

Таким образом, включение в состав устройства блока сложения — вычитания, блока совпадения, блока управления и изменение связей позволили существенно секратить длительность цикла работы 1, (+ц уменьшено в Nll„раз) и расширить функциональные возможности делителя (можно изменять минимальную и максимальную выходные частоты Вх l 3Ó Nnl пределах Вх с с Ьх Ф и Вью

+u. и, тем самым, изменять длительность цикла работы 1 .

Формула изобретения

Делитель частоты с автоматически изменяющимся коэффициентом деления, 10 содержащий двоичный делитель частоты, первый. блок совпадения, управляющие входы которого соединены непосредствен» f ( но с разрядами реверсивного счетчика импульсов и через дешифратор - с первыl5 ми входами первого и второго элемен» тов И, вторые входы которых соединены с выходом двоичного делителя частоты, третьи - соответственно с шиной суммирование и "вычитание", а выходы — со 0 входами реверсивного счетчика импульсов, о т л и ч а ю ш и и с я тем, что, с целью сокращения длительности цикла работы и расширения функциональных возможностей, в него введены блок управления, дополнительный блок совпадения и блок сложения - вычитания, первый вход которого подключен ко входу устройства, второй вход - к выходу первого блока совпадения, а выход - ко входу двоичного делителя частоты, выходы разрядов которого соединены с сигнальными входами первого и второго блоков совпадения, управляющие входы последнего из которых соединены с выходами блока упЗ5 равления, а выход является выходом устройства, при этом вход "вычитание" реверсивного счетчика соединен с выходом первого элемента И, а вход сложение с выходом второго элемента И.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

4 552704 24.02.76.

2. Авторское свидетельство СССР

% 451199> кл. Н 03 К 23/00, 19.01.72 (прототип) .

696608

v гагрЖиие

Составитель О. Митрофанов

Редактор Д, Мепуришвили ТехредЛ. Алферова корректор E Папп

Заказ 6791/57 Тираж 1060 Подписное

UHHHHH Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4