Запоминающее устройство

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ИТЕЛЬСТВУ

«ii 696871 (63) Дополнительное к авт, свид-ву(22) Заявлено 240178 (21} 2573115/18-24 с присоединением заявки Ио (23} ПриоритетОпубликовано 0709.81. сиоллетень Н9 ЭЗ

Дата опубликования описания 0709.81 (53)м. кл.з

С 11 С 17/00

Государственный комитет

СССР но делаю нзобретеннй н открытнй (S3) УДК 828. 327. .6(088.8) (72) Авторы изобретения

Г.B.Âèòàëèåâ, И.В.Евсеева и. A.Ï.×óãóíîý (73 } Заявитель (54) ЗАПОМИНИОЩЕЕ УСТРОЙСТВО

Изобретение относится к области вычислительной технике, а именно к сверхбыстродействующим запоминающим устройствам (ЗУ), которые используются как буферные ЗУ процессоров или Зу для хранении микропрограмм.

Известны ЗУ для хранения микропрограмм, в которых выходы дешифратора старших разрядов адреса соединяются с входами управления выборкой соответствующих запоминающих .модулей каждого рязряда (1).

Однако при этом быстродействие

Зу снижается как в режиме считывания, так и в режиме записи и за счет задержек в тракте управления выборкой. о

Наиболее близким к предлагаемому по технической сущности является ЗУ, в котором обеспечивается повышение быстродействия в режиме считывания, т.е. в режиме функционирования постоянного ЗУ, содержащее запоминающий блок для хранения микропрограмм, разделенный на четыре модуля, информационные выходы которых соединены с входами четырехканального переключа- теля, выполненного на элементах И-ИЛИ управляющие входы которого подключены к выходам дешифратора адреса, а ЗО выходы — к входам регистра считанной информации (21.

Недостатком ЗУ является снижение его быстродействия при записи новой информации, так как комбинированное управление по входу управления выбор. кой в режиме записи и при помощи выходного многоканального переключателя в режиме считывания не позволяет повысить быстродействие ЗУ в режиме записи. Это обусловлено тем, что сит налы на входе дешифратора старших разрядов кода адреса обычно вырабатываются с "существенной задержкой, что приводит к непроизводительным потерям времени при подаче этих сигналов на входы управления выборкой в режиме записи. Кроме того, наличие двойного управления увеличивает объем электронного оборудования ЗУ и усложняет его работу.

Целью изобретения является повышение быстродействия ЗУ.

Поставленная цель достигается тем, что в Зу, содержащее матричный накопитель на запоминающих модулях, адресные входы которых соединены с первыми адресными шийами, информационные входы — с информационным к шинами, а выходы запоминающих модулей каждой стро696871,ки накопителя подключены к одним из .входов соответствующих мультиплексоров, выходы которых соединены с входами регистра информации, и дешифратор, входы которого соединены с вторыми адресными шинами, а один из выходов — с другими входами мультиплексоров, введены элементы И, одни иэ входов которых соединены с другими выходами дешифратора, другие подключены к шине записи, а выходы элементов И соединены с управляющими входами соответствующих запоминающих модулей.

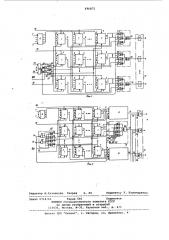

На фиг. 1-2 дана структурная схема устройства.

Устройство содержит матричный накопитель на запоминающих модулях 1, имеющих адресные входы 2, информационные входы 3, информационные выходы 4 и входы 5 управления записью. Модули

1 могут быть выполнены в виде интегральных микросхем. Устройство содержит регистр б адреса, входы которого соединены с первыми адресными шинами

7, а выходы — с входами 2 модулей 1, и мультиплексоры 8„ выполненные, например, в виде элементов И-ИЛИ (8A, 8Б), входы 9 которых подключены к выходам 4 модулей 1 соответствующей . строки матрицы, а выходы 10 — к входам триггеров 11 регистра 12 информации. Входы дешифратора 13 адреса подсоединены к вторым адресным шинам

14, а выходы — к управляющим входам

15 мультиплексоров 8. Информационные шины 16 присоединены к входам 3 модулей 1 соответствующей строки матрицы.

Устройство содержит также блок 17„ выполненный на элементах 18 И, первые входы 19 которых соединены с выходами дешифратора 13, вторые входы 20 - с шиной 21 записи, а выходы 22 — с управляющими входами 5 модулей 1 соответствующего столбца матрицы.

Дешифратор адреса (см. фиг. 2) может быть разделен на несколько дешифраторов 23, один из которых введен в блок 17, а другие — в состав мультиплексоров 8.Дешифраторы 23 выполнены

l.на входных элементах 23 и элементах

24 И, входы которых соединены с прямыми или обратными выходами соответ/ ствующих элементов 23 . При этом элементы 24 оследнего каскада дешифраторов 23 совмещаются с элементами И блока 17 и мультиплексоров 8.

Триггеры 11 регистра 12 могут иметь вторые входы 25 и входы 26 управления, причем .выходы триггеров

11 в этом случае соединяются с соответствующими шинами 16, что позволяет использовать регистр 12 в качестве регистра записываемой и считываемой информации.

Устройство работает следующим образом.

В режиме записи по шинам 16 на вход устройства поступает код записываемой информации, по шинам 7 — код основного адреса, а по шине 20 признак записи. Запись производится в тот столбец модулей 1, код номера которого поступает по шинам 14 на

5 Bx oц дешифратора 13. Увеличение быстродействия устройства достигается за счет уменьшения задержки в блоке

17 до величины задержки сигнала на одном элементе 18. В режиме считы.вания по коду адреса на шинах 7 производится выборка информации из всех модулей 1, а по коду адреса на шинах

14 при помощи мультиплексоров 8 на входы триггеров 11 регистра 12 производится передача информации выбранного столбца модулей 1.

Устройства, показанные на фиг, 2 и 1, работают аналогично, так как блок 17 и мультиплексоры 8 в обоих устройствах функционируют одинаково.

2О Различие между этими схемами обусловлено тем, что при большом числе входов 9 мультиплексоров 8 и входов

19 элементов 18 число управляющих входов можно уменьшить за счет введед ния дешифраторов в состав этих схем, причем,эти узлы реализуются на типовых логических модулях, например

500ИД61 и 500ИД64. Наличие вторых входов 25 и входов 26 триггеров 1" позволяет использовать регистр 12 как в режиме записи, так и в режиме считывания. При этом добавляется один вспомогательный режим — занесения информации на регистр. В остальном работа устройства не отличается от работы известных устройств.

Формула изобретения

Запоминающее устройство, содержащее матричный накопитель из запоми49 нающих модулях, адресные входы которых соединены с первыми адресными шинами, информационные в.оды — c ииформационными шинами, а выходы запоминающих модулей каждой строки накопителя подключены к одним из входов соответствующих мультиплексоров, выходы которых соединены с входами регистра информации, и дешифратор,входы которого соединены с вторыми адресными шинами, а одни из выходов — с другими входами мультиплексоров, отличающееся тем, что, с целью повышения быстродействия устройства, оно содержит элементы И, одни из входов которых соединены с другими выходами дешифратора, другие подключены к шине записи, а выходы элементов И соединены с управляющими входами соответствующих запоминающих модулей.

40 Источники информации, принятые во внимание при экспертизе

1. Патент США 9 3325787, кл. 340-172,6, 1969.

2. Патент США Р 3800293, д .кл 340-172,5 1974 (прототип).

696871

4 .1

Редактор М.Кузнецова Техред

Корректор у. Пономаренко

A. Ач

Заказ 6714/61 Тираж 645 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектнак, 4