Операционное устройство

Иллюстрации

Показать всеРеферат

Сс я оФ (Фг1 ф,, щ

4 е- нате.. (Ця

Союз Сааетсккк

Соцкалксткческкк

Республик п

ИЗОБРЕТЕН ИЯ! 697997 (6l ) Дополнительное к авт. свкд-ву (22) Заявлено 03.12.76 (21) 2425992/18-24 с присоединением заявки М (23) Приоритет (51)M. Кл.

С О6 15/Об

Гесударствеяивй каатет

СССР в двак кзабравк!и! я !!ткрктнй

Опубликовано 15.11.79. Бюллетень Уй 42

Дата опубликования опксания 15.11.79 (53) ЙК 681.325! 088.8) Б. П. Доброхотов, Б. М. Иванов, М. В. Котельников, В. Я. Холманских и Т. Ф. Шапетько (72) Авторы изобретения (71) Заявитель

ОКБ "Импульс" (54} ОПЕРАЦИОННОЕ УСТРОЙСТВО

Изобретение относится к области вычислительной техники, в частности к операционным устройствам, и может быть использовано в процессорах различного назначения.

Известно операционное устройство, содержа5 щее информационные регистры, единичные входы триггеров каждого разряда которых подключены к выходам элементои И, блок приема информации, блок управления, элементы

НЕ элементы И с открытым коллектором (1).

> !

Недостаток устройства состоит в том, что оно имеет ограниченные функциональные возможности.

Наиболее близким к изобретению по технической сущности и достигаемому результату !

5 является операционное устройство, содержащее блок дешифрации команд, первый выход которого соединен с первым вхопом блока управления, блок синхронизации, выход которого соединен со вторым входом блока управ20 ления, регистр результата, выход которого соединен с первым входгьм блока буферной памяти, первый коммутатор, первый и второй входы которого соелинсчв с выходами регист! ров соответственно первого н второго операндов, сумматор, выход которого соединен с первым входом второго коммутатора, и датчик параметров сдвига, выход которого соединен с управляющим входом регистра результата, причем выход блока буферной памяти соединен со входом регистра нервого операнда и с первым входом регистра второго операнда, второй вход которого является информационным входом устройства, первый и второй выходы первого коммутатора соединены соответственно с первым и вторь!м входами сумматора, третий вход которого, вторые входы блока буферной памяти и второго коммутатора, входы первого коммутатора н латника параметров сдвига соединены с первым выходом блока управления, выходы второго коммутатора и второй выход блока дешифрации команд соединены соответственно с разрялными входами регистра результата и сА вхо:1()M блока синхронизации, а вход блока пен нфраннн команд является командным вхолом ус!ройства (2).

Недостаток устройства с ",.< нг в том, что оно имеет незначигелын с .I,.0 ол .йсгвне.

697997 да, от которого начинается поиск единицы, задан и разрядах 27 — 31 регистра 4. Шифруемое число находится в регистре 5.

Из регистра 5 побайтно читается шифруемое число. Разряд от которого идет поиск, определяется следующим образом: результат дешифрации старших разрядов параметра (разряды 27, 28) в дешифраторе 13 определяет номер байта, с которого начинается поиск еди10 ницы, а на основании дешифрации младших разрядов (разрядов 29, 30; 31) регистра 4 дешифратором 14 для поиска единицы поступают только те разряды байта, которые находятся.по направлению поиска. Результатом !

5 работы является двоичный номер первого ненулевого (приоритетного) разряда от границы поиска, если он есть. Общая совокупность сигналов: номер байта из блока 3 управления и сигналов с дешифраторов 13, 14 организу20 ет поиск первой единицы в граничном байте.

В случае отсутствия первого ненулевого разряда в граничном байте происходит последовательный поиск единицы в последующих байтах. Эта последовательность сигналов поступает в формирователь 15, который формирует код границы в байте, от которого ведется поиск первого ненулевого разряда. В случае обнаружения единицы на регистре 17 формируется двоичный код первого единичного разря3О да в байте, в направлении поиска, Два старших разряда, определяющие номер байта, в котором обнаружена единица, формируются блоком 3 управления. Занесение в регистр 11 сформированного результата шифрации проис35 ходит через элементы И 18, 19. В случае от7 сутствия единицы в части слова от границы поиска, при последовательном переборе всех старших байтов, результат шифрации остается нулевым. Далее, результат через коммутатор 9 заносится по байтным информационным стробам записи в регистр 11 результата.

Цель изобретения — повышение быстродействия.

Поставленная цель достигается тем, что уст. ройство содержит первый и второй дешифраторы, преобразователь порядка расположения разрядов, регистр номера приоритетного раз-. ряда, формирователь кода границы поиска и три элемента И, причем третий выход первого коммутатора соединен с первым входом перво го элемекта И и через преобразователь порядка расположения разрядов — со входом второго коммутатора, четвертый выход первого коммутатора соединен со входами первого и второго дешифраторов, выходы которых соединены с первым входом формирователя кода границы поиска, выход которого соединен со вторым входом первого элемента И, вход и первый выход регистра номера приоритетного разряда соединены соответственно с выходом первого элемента И и с первым входом второго элемен та И второй вход которого и первый вход третьего элемента И соединены со вторым выходом регистра номера приоритетного разряда, выход первого дешифратора соединен с третьим входом био а управления,"второй выход которо го соединен со вторыми входами формирователя кода границы поиска и третьего элемента И, а выходы второго дешифратора, второго и третьего элементов И соединены со входом второго коммутатора.

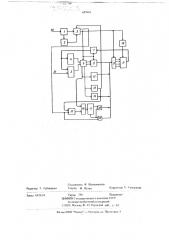

Структурная схема устройства представлена на чертеже.

Операционное устройство содержит блок 1 дешифратора команд, блок 2 синхронизации, блок 3 управления, регистр 4 первого операнда регистр 5 второго операнда, первый коммутатор 6, блок 7 буферной памяти, сумматор 8, второй коммутатор 9, датчик 10 параметров сдвита, регистр 11 результата, преобразователь

12 порядка расположения разрядов, первый

13 и второй !4 дешифраторы, формирователь

15 кода границы поиска, первый элемент

И 16, регистр 17 номера приоритегного разряда, второй 18 и третий 19 элементы И, командный 20 и информационный 21 входы.

Операционное устройство работает следующим образом.

Операция "Ш ифра ция"

Команда "Шифрация в сопровождении сиг.нала "Команда готова" принимается в блок 1, запускается блок 2 синхронизании, блок 3 управления вырабатывает сигналы обращения к блоку 7 (два последовательных запроса) и происходит чтение содержимого регистра 4, 55 затем содержимого регистра 5 с последующей записью в регистр 4 первого операнда и регистр 5 второго операнда. )la»ee производится побайтное выиолненис операции. Номер разряОперация Дешифрация.

При выполнении команды Дешифрация происходит считывание операнда из блока 7 по адресу, содержащемуся в регистре 5, и запись в регистр 5. Через коммутатор 6 иятиразрядный параметр поступает на вход дешифраторов !3, 14. Llaa старших разряда дешифруются дешифратором !3, выходы которого учас|вуют в формировании стробов записи в регистр результата и определяют номер байта, в который необходимо записать результат дешифрации трех млашиих разр»дов параметра, дешифрируемых лешифратором !4. Påçóèbтат дешифрации заиисываекя в блок 7 ц< апpeep, содержашемуся в рп исгр» 4.

Оиераиия Рефлексия

5 697997

Выполнение операции "Рефлексия реализуется преобразователем 12 представляющим собой линейку вентилей, запайка выходов которых проведена зеркально относительно сердины байта. Через первый коммутатор 6 рефлектируе- 5 мый операнд подается на преобразователь 12, начиная с младшего байта. Занесение результата рефлексии производится в регистр 11 результата страбированный управляющими сигналами из блока 3 управления. 0

Изобретение по сравнению с известным устройством имеет более высокое быстродействие. Действительно поиск единичного знатен m бита от заданного начала отсчета с помощью операций "сдвига", "перехода условного", "пе- 15 рехода по счетчику" требует в реднем 3 х 32:

2 - - 48 операций над 32-х разрядными слонами. В изобретении для решения тай же задачи требуется всего одна операция. Эта операция в 48 раз увеличивает быстродействие 20 ненулевого бита.

При отсутствии операции "дешифрация" запись числа ат 0 до 31 в таблицу битовых спецификацш с помощью операций "Вычитание 25 кодов, "переход условный, переход по счетчику" требует в среднем Зх32:2= 48 операщ4й над 32-х разрядными словами. Та есть эта операция в 48 раз увеличивает быстродействие записи числа в таблицу битовых спецификаций.

Таким образом при наличии всего 1% ат общего числа операций на шифрацию и дешифрацию тратится 50 o эффективного быстродействия при отсутствии этих операций в списке команд.

Формула изобретения

Операционное устройство, содержащее блок дешифрации команд, первый выход которого соединен с первым входом блока управления, блок синхронизации, выход которого саеди45 нен са вторым входом блока управления, регистр результата, выход которого соединен с первым входом блока буферной памяти, первый коммутатор, первый и второй входы каторага соединены с выходами регистров соат50 ветственна первого и второго операндов, сумматор, выход которого соединен с первым входом второго коммутатора, и датчик параметров сдвига, выход которого соединен с управляющим входам реьэ(стра результата, при. ем выход блока буферной памяти соединен со входом регистра первого операнда и с первым входом регистра второго операнда, второй вход которого является информационным входом устройства, первый и второй выходы первого коммутатора соединены соответственно с первым и вторым входами сумматора, третий вход которого, вторые входы блока буферной памяти и второго коммутатора, входы первого коммутатора и датчика параметров сдвига, соединены с первым выходом блока управления, выходы второго коммутатора и второй выход блока дешифрации камачд соединены соответственна с разрядными входами регистра результата и со входом блока синхронизации, а вход блока цсшифращш команд является командным входом устройства, о тл и ч г ю щ е е с я тем, что, с целью повышения быстродействия, ана содержит первый и второй дешифратары, преобразователь порядка расположения разрядов, регистр номера приоритетного разряда, формирователь када границы поиска и три элемента И, причем третий выход первого коммутатора соединен с первым входом первого элемента И и через преобразователь порядка расположения разрядов — са входом второго коммутатора, четвертый выход первого коммутатора соединен со входами первого и второго дешифраторов, выходы которых соединены с первым входом формирователя кода границы поиска, выход которого соединен со вторым входам первого элемента И, вход и первый выход регистра номера прнаритетнага разряда соединены соответственна с выходам первого элемента И и с первым входом второго элемента И, второй вход которого и первый вход третьего элемента И соединены са вторым выходом регистра номера приоритетного разряда, выход первого дешифратара соединен с третьим входом блока управления, второй выход которого соединен са вторым входами формирователя кода границы поиска и третьего элемента И. а выходы второго дешифратора, второго и третьего элементов И соединены са входом второго коммутатора.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельства С(СР N 481899, кл. 6 06 F 15/00(1975.

2. Абонентский пункт AH- 4, 1..С вЂ” 8504, ПТ1 320,114. TO с. 46, рпс. 5 (прототип). (б97997

Редактор 3. Рубнидкая

Тираж 7 0 Подписное

ИНИИПИ Государственного комитета С(.(P по делам изобретений и открытий

113035, Москва, Ж-35, Раугнская наб, ц. 4/5

Заказ 6929/34

Филиал Illlll "Патент . г. Ужгород, ул. Проектная, 4

Составитель Ф. Шагиахметов

Техред М. Петко Корректор Т. ("кворцова