Интегратор с запоминанием

Иллюстрации

Показать всеРеферат

Союз Советсиин

Социалистических

Республик

QllNCAHHE

ИЗОБРЕТЕНИЯ .

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

< 698009 (61) Дополнительное к авт. свид-ву (22) Заявлено 09.03.78 (21) 2588345/18-24 (5l)M. Кл.

G 06 G 7/18 с присоединением заявки М (23) Приоритет

Гесудерстеенньн1 ееиетет

СССР ее делам нзабретеннй е етнрьпнй

Опубликовано 15,11.79. Бюллетень М 42

Дата опубликования описания 15.11.79 (53) УЛК

681.335 (088.8) (72) Авторы изобретения

А, И. Гейфман, Ю. М. Месонжник и О. И. Хуторянский

Специальное конструкторское бюро диагностической аппаратуры (71) Заявитель (54) ИНТЕГРАТОР С ЗАПОМИНАНИЕМ

Изобретение относится к аналого-цисЬровой измерительной технике .и может найти применение в аналого-цифровых преобразователях, а также в аналоговых измерительных устройствах для обработки информации.

Известны интеграторы с запоминанием, выполненные на базе операционного усилителя с запоминающим конденсатором в цепи обратной связи (1) и (2)

Однако известные интеграторы обладают недостаточной точностью из-за влияния конечного сопротивления операционного усилителя.

Наиболее близким предлагаемому пс технической сущности является интегратор, содержащий операционный усилитель, выход которого через запоминающий конденсатор соединен с инвертирунпцим входом и через аналоговый ключ — с одной из обкладок накопительного конденсатора, другая обкладка которого связана с шиной нулевого потенциала, и согласующий блок, выход которого соединен с инвертирующим входом операционного усилителя. Аналоговый ключ интегратора замыкается на промежутке времени с периодом

Т (3).

Основная погрешность интегрирования . вход. ных сигналов вносится за счет перезаряда накопительного конденсатора, так как в на. чальный момент конденсатор разряжается через источник входных сигналов, а затем снова заряжается до напряжения. пропорционального амплитуде входного сигнала. На выход интегратора в каждом периоде будет подаваться сначала линейно-нарастающее напряжение в течение времени С-, равного длительности входного сигнала, а в оставшуюся часть периода— постоянное напряжение. 3а счет этого уменьшается средний уровень выходного напряжения. Величина этой погрешности зависит от скважности входных сигналов и от соотношения амплитуд напряжений предыдущего и последующего сигналов.

Цель изобретения, — повышение точности интегрирования входных сигналов.

Указанная цель достигается тем, что в интегратор с запоминанием введены дополнительный аналоговый ключ, дополнительный

698009

3О

U = Кт..

Емкость накопительного конденсатора 6

55 может быть на два-три порядка меньше емкости конденсатора 4, вследствие чего погрешность интегрирования, связанная с перераспределением заряда, будет минимальной, накопительный конденсатор и формирователь управляющих сигналов, вход которого соедиНсН со входом интегратора, à выход поцключен к управляющим входам основного и дополнительного аналоговых ключей, сигнальный вход дополнительного аналогового ключа соединен с выходом основного аналогового ключа, а выход дополнительного аналогового ключа подключен к входу согласующего блока и одной из обклацок дополнительного накопительного конденсатора, другая обкладка которого соединена с шиной нулевого потенциала.

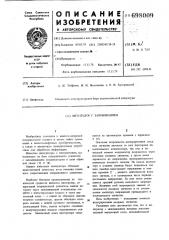

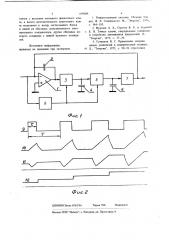

На фиг. 1 изображена структурная схема интегратора с запоминанием; на фиг. 2— эшоры напряжений;

Интегратор состоит из оператгионного усилителя 1 с запоминающим конценсатором " в цепи обратной связи, первого аналогового ключа 3, через который первый накопительный конденсатор 4 подключен к выходу усилителя 1, второго аналогового ключа 5 и второго накопительного конденсатора 6, включенных между первым накопительным конденсатором 4 и входом согласующего блока 7, 25 формирователя управляющих сигналов 8, вход которого связан со входом интегратора, а к выходу подключены управляющие входы аналоговых ключей 3 и 5, включенных в противофазе.

Входной сигнал 9 (фиг. 2), имеющий длительность Г, интегрируясь операционным усилителем 1 с запоминающим конденсатором

2 в цепи обратной связи, преобразуется в пилообразное напряжение 10, максималькая величина которого пропорциoHQJlbHB длительности входного сигнала, т.е.U = 1сТ, где — коэффициент пропорциональности.

Одновременно входной сигнал поступает о на вход формирователя входных сигналов 8, который из этих сигналов формирует импульсы, управляющие работой аналоговых ключей 3 и 5. Сигналами формирователя открывается аналоговый ключ 3 и закрывается ключ 5. Накопительный конденсатор 4. заряжается до максимального напряжения "пилы"

Рм. После окончания входного сигнала импульсами формирователя 8 ключ 3 закрывается, а ключ 5 открывается, и накопитель50 ный конденсатор 6 быстро перезаряжается от конденсатора 4 до величины поскольку величина ее определяется соотношением емкостей, Нри поступлении следующего входного сигнала накопительный конденсатор 4 разряжает. ся через запоминающий конценсатор 2 в цепи обратной связи операционного усилителя 1 до напряжения, близкого к начальному значению пилообразного напряжения 10, а затем линейно заряжается.

Накопительный конденсатор 6 не принимает участия в переходном процессе, связанном с нарастанием пилообразного напряжения, так как в интервале времени Г аналоговый ключ 5 закрыт импульсом формирователя управляющих сигналов 8.

Таким образом, в течение каждого периода следования входных сигналов на накопительном конденсаторе 4 будут иметь мест:.. перепады напряжения 11 (фиг. 2), а на накопительном конденсаторе 6 и, соответственно, на выходе согласующего блока 7 будет квазипостоянное напряжение 12, величина которого пропорциональна длительности входных сигналов 9, т.е. среднее значение напряжения на выходе интегратора определится

Ucp = 1м = "«.

Из этого равенства видно, что в данном случае имеется линейная зависимость между средним напряжением на выходе интегратора и длительностью входных сигналов.

Выполнение интегратора с запоминанием по указанной схеме позволяет практически исключить погрешкость, связанную с перезарядом запоминающего конденсатора. В результате повьппается точность обработки информации вычислительных устройств.

Формула изобретения

Интегратор с запоминанием, содержащий операционный усилитель, выход которого через запоминающий конденсатор соединен с инвертирующим входом и через аналоговый ключ — с одной из обкладок накопительного конденсатора, другая обкладка которого связана с шиной нулевого потенциала, и согласуюший блок, выход которого соединен с инвертирующим входом операционного усилителя, отличающийся тем, что, с целью повышения точности интегрирования, в него введены дополнительный аналоговый ключ, дополнительный какопительный конденсатор и формирователь унравляюших сигналов, вход которого соединен со входом интегратора, а выход подключен к управляющим входам основного и дополнительного

ы- алоговых ключей сигнальный вход дополнительного аналогового ключа со698009

ЦНИИПИ Заказ 6562/16 Тираж 780 Подписное

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 спилен с выходом основного аналогового ключа, а выход дополнительного аналогового ключа подключен к входу согласующего блока и одной из обкладок дополнительного накопительного конденсатора, другая обкладка которого соединена с шиной нулевого потенциала.

Источники информации, принятые во внимание при экспертизе

1. Развертывающие системы. Сборник поп ред, В. Л. Славинского. М., Энергия". 1976, с. 144-150.

2. Мурсаев А. Х., Смолов В. Б. и Угрюмов

E. П. Точные ключи, операциошгые усилители и устройства запоминания йапряжсний. Л..

"Энергия", 1972, с. 17 — 28.

3. Гутников В. С. Применение операционных усилителей в измерительной техншсе.

1О Л,, "Энергия", 1975, с, 90 — 93 (прототип)