Устройство для контроля памяти

Иллюстрации

Показать всеРеферат

(72) Авторы изобретения

Г. П. Крупников, И. А. Марков. и М. П. Сергеев

Институт электроники и вычислительной техники АН Латвийской ССР (71) Заявитель (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПАМЯТИ

Изобретение относится к запоминающим устройствам.

Известно устройство для контроля памяти, содержащее схему формирования растра, формирователи управляющих сигналов, схему сравнения, счетчик (11.

Однако зто устройство не обеспечивает автоматизированного выявления взаимного влияния ячеек блока памяти.

Наиболее близким к предлагаемому является устройство, содержащее генератор кодов адреса, первый выход которого подключен ко входу блока управления и первому выходу устройства, схему сравнения, первый вхоц которой подключен к одному из выходов блока управления, другой выход которого соединен со вторым выходом устройства„а второй вход схемы сравнения подключен к входу устройства (21.

К недостаткам известного устройства относится невысокая надежность и невозможность реали20 зации стандартных режимов проверки работоспособности блоков памяти, таких как бегущий ноль, единица, шахматное поле и т.л.

Цель изобретения — повышение надежности устройства,. а также расширение области применения устройства за счет возможности реализации в нем указанных выше режимов.

Укаэанная цель достигается тем, что устройство содержит формирователь сигналов координатной сетки, смеситель сигналов и телевизионный приемник, один вход которого подключен к выходу смесителя сигналов, а другой — ко второму выходу генератора кодов адреса, входы смесителя сигналов подключены соответственно к выходу схемы сравнения и выходу формирователя сигналов координатной сетки, вход которого соединен с первым выходом генератора кодов адреса.

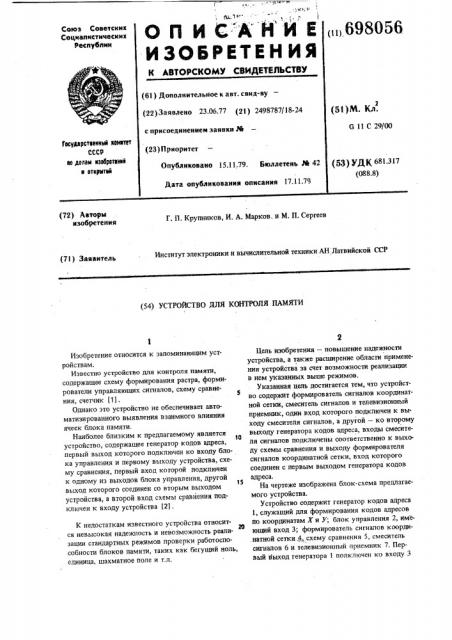

На чертеже изображена блок-схема предлагаемого устройства.

Устройство содержит генератор кодов адреса

1, служащий для формирования кодов адресов по координатам Х и У; блок управления 2, имеющий вход 3; формирователь сигналов коорди. натной сетки, схему сравнения 5, смеситель сигналов 6 и телевизионный приемник 7. Первый выход генератора 1 попключен ко входу 3

3 6 блока 2 и первому выходу устройства. Первый вход схемы сравнения 5 подключен к одному из выходов блока 2, другой выход которого соединен со вторым входом устройства, а второй вход схемы сравнения 5 подключен ко входу устройства. Од»н вход приемника 7 подключен к выходу смесителя 6, другой — ко второму выходу генератора 1. Входы смесителя 6 подключены соответственно к выходу схемы сравнения 5 и выходу формирователя 4, вход которого соедине1» с выходом генератора 1. Ко входу и выходам устройства подключается контролируемый блок памяти 8.

Работа устройства рассматривается на примере контроля блока памяти емкостью 256 битов, организованных в 64Я4 бита, т.е. 64 четырехразряднь»х слова. Генератор 1 последовательно формирует коды, соответствующие адресам, ячеек контролируемого блока памяти 8. При этом формирователь 4 вырабать»вает сигнал, который через смеситель 6 поступает на вход приемника

7, работающего в построчном режиме, и формирует на экране прямоугольную сетку.размером

16х16, каждый прямоугольник которой соответствует одной ячейке блока памяти 8 (или m-разрядному сло»»у). Размер ячейки может меняться по желанию оператора. На первь»х и строках (где

n — размер ячейки по вертикали) адрес У остается неизменным, а адрес Х циклически меняется от 1 до 16, причем после каждого цикла считывания адресов Х (т.е, перебора всех 16) генератор 1 вырабатывает строчный синхроимпульс, который подается на вход приемника 7. После сканирован»»я и строк адрес У увеличивается на единицу и т.д. После сканирования всех строк, соответствующих координатной сетке, генератор

1 вырабатывает кадровый синхроимпульс, который подается на вход приемника 7, и процесс повторяется. При этом в зависимости от выбранного режима может производиться не только последовательное считывание информации из блока памяти 8 и отображение ее на экране (при котором, например, логическому "0" соответствует минимальная яркость, а "1" — максимальная,) но и контроль блока памяти 8. В режиме контроля блок 2 при адресации к очередной ячейке

98056 4 производит запись необходимой информации.

Считанная из ячейки информация в схеме сравнения 5 сравнивается с информацией, поданной иэ блока 2. В случае несовпадения сигналов на обоих входах схемы 5 на ее выходе формируется сигнал, который через смеситель 6 подается на вход приемника 7, подсвечивает прямоугольник координатной сетки, соответствующий ячейке, в которой наблюдается сбой. Описанное уст10 ройство позволяет реализовать различные режимы контроля блока памяти,8 и обеспечивает индикацию результатов контроля.

При необходимости формирователь 4 может включать генератор символов, позволяющий

>5 в численном виде задать на экране телевизионного приемника 7 координаты ячеек блока памяти 8.

Формула изобретения

Устройство для контроля памяти, содер20 жащее генератор кодов адреса, первый выход которого подключен ко входу блока управления и первому выходу устройства, схему сравнения, первый вход которой подключен к одному из выходов блока управления, другой выход которого соединен со вторым выходом устройства, а второй вход схемы сравнения подключен ко входу устройства, отличающееся тем, что, с целью повышения надежности устройства, оно содержит формирователь сигналов координатной сетки, смеситель сигналов и телевизионный приемник, один вход которого подключен к выходу смесителя сигналов, а другой — ко второму выходу генератора кодов адреса, входы смесителя сигналов подключены соответственно к выходу

Ç5 схемы сравнения и выходу формирователя сигналов координатной сетки, вход которого соединен с первым выходом генератора кодов адреса.

Источники информации, принятые во внима4о ние при экспертизе

1. Китович В. В. Оперативные запоминающие устройства на ферритовых сердечниках и тонких магнитных пленках, М,-Л., "Энергия", 1965, с, 223-228.

4> 2. "Электроника", N 1, 1976, с. 70-73 (прототип).

ЦНИИПИ Заказ 6565/17

Тираж 681 Подписное

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4