Полосовой цифровой фильтр

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик (б1) Дополнительное к авт, сеид-ву— (22) Заявлено 1511,77(21) 2545644/18-09

{51)М. Кл.

Н 03 Н 7/28 с присоединением заявки»>Е

Государственный комитет

СССР но делам изобретений и открытий (23) Приоритет— (53) УДК 621.372. 54 (088. 8) Опубликовано 1511.79, Бюллетень М 42

Дата опубликования описания 1511.79 (72) Авторы изобретения

Ю. К. Свешников и И. И. Семенов (71) Заявитель (54) IIOJIOCOROA ЦИФРОВОЙ ФИЛЬТР

Изобретение относится к радиотехнике и может использоваться для обработки сигналов в системах связи.

Извест ен полосовой цифровой фильтр, содержащий аналого-цифровой преобразователь, выходом соединенный с первым входом коммутатора записи, выход которого через регистр сдвига подключен ко второму входу коммутатора записи, перемножитель, одним из входов соединенный с выходом блока памяти весовых коэффициентов, а выходом — co входом накапливающего сумматора, блок буферной памяти и блок синхронизации, соответствующие выходы >5 которого подключены к управляющим входам аналого-цифровorо. преобразователя, коммутатора записи, блока памяти весовых коэффициентов и регистра сдвига (1) . 20

Однако известный полосовой цифровой фильтр обладает большой длиной регис тра сдв ига .

Цель изобретения — обеспечение требуемой полосы пропуска ния при сниженном а ппа ра турн ом объеме памя ти. ,Цля этог о в полос овом цифров ом фильтре, содержащем аналого-цифровой преобразователь, выходом соединенный с первым входом коммутатора записи, выход которого через регистр сдвига подключен ко в-орому входу коммутатора записи, перемножитель, одним из входов соединенный с выходом блока памяти весовых коэффициентов, а выходом — co входом накапливающего сумматора, блок буферной памяти и блок синхронизации, соответствующие выходы которого подключены к управляющим входам аналого-цифрового преобра зов ателя, к оммута тора записй, блока памяти весовых коэффициентов и регистра сдвига, второй вход перемножителя соединен с выходом введенного коммутатора регистров, первый вход которого подключен к выходу регистра сдвига, а второй .вход — к выходу дополнительного регистра сдвига и первому входу доголнительного коммутатора записи, второй вход которого соединен с выходом накапливающего сумматора и входом блока буферной памяти, а выход — к входу дополнительного регистра сдвига., при этом управляющие входы коммутатора регистров,дополнительного регистра сдвига и дополнительного коммутато-. ра записи подключены к дополнительным выходам блока синхронизации.

698126

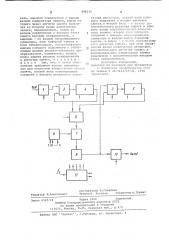

На чертеже приведена структурная электрическая схема предложенно- го полосового цифрового фильтра.

Полосовой цифровой фильтр содержит аналого-цифровой преобразователь

1, коммутатор 2 записи, дополнительный коммутатор 3 записи, регистр 4 сдвига, дополнительный регистр 5 сдвига коммутатор 6 регистров, перемножитель 7, блок 8 памяти весовых коэфФициентов, накапливающий сумматор 9, блок 10 буферной памяти и блок 11 синхронизации.

Полосовой цифровой фильтр работает следующим об ра з ом.

По команде блока 11 синхронизации запускается аналого-цифровой преоб;. разователь 1 и измеряет текущее значение совокупности суммы сигнала и помех на Входе. Одновременно с запуском аналого-цифрового преобразователя

1 поступает команда на коммутатор 2 записи, при этом регистр 4 сдвига переключается на один такт из кольцевого Режима в режим записи выборки сигнала „причем новая выборка записывается на место самой старой выборки. В регистре 4 сдвига хранится и постоянно обновляется массив из последних выборок входного сигнала. Количество ячеек регистра 4 сдвига рассчитывается для колокольной формы амплитудно-частотной характеристики по следующей приближенной формуле

2-<а

06

35 где N — количество ячеек (длина регистра); частота взятия выборок;

z f — полоса пропускания по уровню

0,5 от максимального коэффициента 4() передачи.

В интервале между моментами записи новых выборок сигнала регистр 4 сдвига работает в кольцевом режиме. Весь массив выборок с тактовой частотой, 45, поступающей от блока 11 синхронизации, перемещается вдоль регистра 4 сдвига °

Этим достигается поочередное прохождение всех выборок на вход коммутатора

6 регистров. Перемножитель 7 предназначен для умножения каждой выборки, поступающей через коммутатор 6 регистров, на весовой коэффициент, представляющий собой двоичное число, которое может иметь отрицательное или положительное значение в зависимости от значения закового разряда.

Абсолютная величина (мантисса) коэффициентов находится в пределах от 0 до 1 и может принимать ряд дискретных значений, количество которых 60 зависит от разрядности коэффициентов.

По окончании операции суммирования выборок на выходе накапливающего сумматора 9 будет присутствовать число, характеризующее помехи и по- 65 лезный сигнал, прошедшие через первый каскад полосового цифрового фильтра, ширина спектра суммы сигнала и помех, прошедших через первый каскад полосового цифрового фильтра, будет значительно уже исходного спектра, чем на входе аналого-цифрового преобразователя 1 и равна ширине полосы пропускания фильтра, опре. деляемой формулой (1) . В связи с этим появляется возможность записывать во второй каскад отсчеты отфильтрованных сигнала и помех реже, чем в первый каскад, что соответствует теореме отсчетов Котельникова. Именно в возможности прореживания выборок (отсчетов) и заключается положительный эффект предложенного изобретения. Если преобразовать формулу (1) в таком виде

2 в

06 )4

1 и при этом заменить 1 яа —, то получим

0B NT где T — интервал взятия выборок.

Но произведение (N Т ) есть не что иное, как время задержки фильтра

N. Ts= T3&.

Формулу (2) можно переписать

-T,àÚ

Таким образом, полоса пропускания зависит только от времени задержки и не зависит от частоты отсчетов. Если путем прореживания можно снизить частоту отсчетов, не меняя при этом времени задержки фильтра (и, следовательно, полосы пропускания), можно снизить аппаратурный объем памяти.

Прореженные отсчеты записываются в дополнительный регистр 5 сдвига второго каскада, принципы работы которого аналогичны работе первого каскада с тем отличием, что тактовая частота дополнительного регистра 5 сдвига меньше тактовой частоты регистра 4 сдвига в К раз, где К— коэффициент прореживания. В случае необходимости может быть введен третий каскад и т. д, Блок 10 буферной памяти по команде блока 11 синхронизации может запоминать результат суммирования первого, второго и т.д. каскадов, при этом полоса пропускания каждого последующего каскада сужается по отношению к предыдущему в К,, К,..., К; раз, где

К,, К,..., К; — коэффициенты прорежйванйя 1,2,...,... i-ого каскадов.

Формула изобретения

Полосовой цифровой фильтр, содержащий аналого-цифровой преобразова698126

Составитель А.Сагадиев

Техред И. Асталом Корректор Н.Горват

Редактор Л.Алексеенко

Тираж 1060 Подписное

ЦНИИПИ 1"осударственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Заказ 6567/18 ул. Проектная, 4

Филиал ППП Патент, r,Ужгород, тель, выходом соедкнепный с первым входом коммутатора записи, выход 1

ВыхОдОМ вЂ” co ВхОдом накапливаю!!1ег0 сумматора., блок буферной памяти и блок синхронизации, соответствую!!!!!=выходы которого подключены к управ— ляющим входам аналого-ц" фровог0 пр=-образователя, коммута.тора записи, блока памяти весовых коэффициентов и регистра сдвига, о т л и ч а. ю !!! и и с я тем, что, с целью Обеспечения требуемой полосы пропускания при сниженном аппаратурном Объ,=„e памяти, второй вход и"påMH0æèTåëê

СОЕДИНЕН С ВЫХОДОМ ВВЕДЕННОГО КОГ1, татора регкст!!ОВ, пер >ый Б

ВО." .у БхОду допол11кте 1ь11()ГО !<О"< утатора записи, Второ й:.;Од которого соединен с В ыходо!, Иа1< "-! . : iIH аю1:„ r0 сумматОра и БхОДОМ блокc3 (.".фернОй памя ТИ а. Б ых Од и Б ::".0,11у,.!IOJTO iIBI

ДОполнктельнОГО pei "". OT1=B. сдвиГа и цополнктельног0 коммутатора записи подклк)чень1 к ДОпОлнктель!<ым БыхОдам блока синхронкзацки.

Источники кнфор!Иа!!ии ;! приьIятI-. е Б о В H!Б IB пке прк экспертизе

АБ торское <. .в!1Детел ьстБ О CCCP по заявке " 241 "422/i 8 — 24 1976 (прототкп),