Устройство для подавления помех

Иллюстрации

Показать всеРеферат

ОЛИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРС!(ОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву Р 519857 (22) Заявлено 16.03.78 (2 ) 2590410/18-09 с присоединением заявки Н<2 (23) Г)риоритет

Опубликовано 15.1179 Б оллетень № 42

Дата опубликования описания 15,11.79

Союз Советских

Социалистических

Республик

3//

Государственный комите

СССР ио делам изобретений и открытий

3.531

) (72) Авторы изобретения

В.H,Óñà÷åâ и Л.И.Кулебин (71) Заявитель (54 ) УСТРОЙСТВО ДЛЯ ПОДАВЛЕНИЯ ПОМЕХ

Изобретение относится к импульсной технике, в частности к формирователям импульсов с подавлением кратковременных помех и может использоваться в вычислительной технике и автоматике.

По основному авт.св. вз519857 известно устройство для подавления помех, содержащее два триггера, каждый из которых имеет выходы нулевой, единичный, синхронизации и раздельной установки в 0 и выходы единичный и инверсный, причем входы раздельной установки в 0 обоих триггеров объединены, вход синхронизации первого триггера является входом устройства, единичный выход второго триггера является выходом устройства, а единичный выход первого триггера соединен с еднничйым входом второго триггера, единичный вход второго триггера объединен с его входом синхронизации, нулевой его вход з аз емлен, а инверсный выход соединен с единичным входом первого триггера, причем объединенные входы раздельной установки в 0 обоих триггеров являются управляющим входом устройства (1).

Однако известное устройство подавляет только кратковременные помехи положительной полярности, что снижает его помехоустойчивость.

Цель изобретения — повьпиение помехоустойчивости, Для этого в устройство для подавления помех, содержащее три триггера, каждый из которых имеет выходы нулевой, единичный, синхронизации и раздельной установки в 0 и выходы единичный и инверсный, причем входы раздельной установки в 0 обоих триггеров объединены, вход синхронизации первого триггера является входом устройства, единичный выход второго триггера является выходом устройства,а единичный выход . первого триггера соединен с единичным входом второго триггера, единичный вход второго триггера объединен с его входом синхронизации, нулевой его вход заземлен, а инверсный выход соединен с единичным входом первого триггера, причем объединенные входы раздельной установки в 0 обоих триггеров являются управляющим входом устройства, введены два дополнительных триггера, соединенные также, как и два основных триггера, и три

698128

50

Формула изобретения

65 элемента ИЛИ-НЕ| причем входы синхронизации первых основного и дополнительного триггеров объединены и являются входом синхронизации устройства, первый элемент ИЛИ-НЕ двумя входами подключен к входу раздельной установки в 0 первого основного триггера и является управляющим входом устройства, ныход первого элемента ИЛИ вЂ соединен с входом раздельной установки в 0 первого дополнительного триггера, второй элемент ИЛИ вЂ первым входом подключен к выходу второго основного триггера, вторым входом — к выходу третьего элемента ИЛИ-Не и является выходом устройства, выход второго элемента ИЛИ вЂ соединен с первым нходом третьего элемента ИЛИ-НЕ, второй вход которого соединен с выходом нторого,дополнительного триггера.

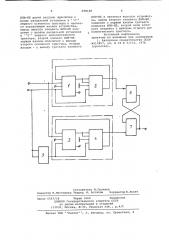

На чертеже изображена структурная электрическая схема предложенного устройства для подавления помех.

Устройство содержит два основных триггера 1 и 2, два дополнительных триггера 3 и 4, первый, второй и третий элементы ИЛИ-FIE 5, 6, 7.

Устройство работает следующим образом.

В исходном состоянии на входах раздельной установки в 0 основных триггерон 1 и 2 присутствует нулевой сигнал, которым они устанавливаются в нулевое состояние при включении напряжения питания устройства. Одновременно на входах раздельной установки в .0 дополнительных триггеров 3 и 4 присутствует в исходном состоянии единичный сигнал, поэтому при подаче напряжения питания дополнительные триггеры

4 и 3 могут устанавливаться в произвольное состояние. Но независимо от этого максимум через время равное двум периодам тактовых ймпульсов после включения напряжения питания, устройство приходит в исходное состояние. При этом на его выходе устанавлинается нулевой сигнал.4 При поступлении на управляющий вход устройства единичного сигнала разрешается работа оснонных триггеров

1 и 2, а дополнительные триггеры

3 и 4 перебрасываются в нулевое состояние. После этого спадом первого пришедшего тактового импульса, поступиншего на вход синхронизации основного триггера 1, на его единичном выходе устанавливается единичный сигнал, а на инверсном выходе нулевой сигнал. Затем спадом следующего тактового импульса на единичном выходе основного триггера 1 устанавливается нулевой сигнал, при этом основной триггер 2 перебрасынается

25 0

45 в единичное состояние, Единичный сигнал появляется на выходе устройстна. Нуленый сигнал с инверсного выхода оснонного триггера 2 поступает на единичный вход основного триггера 1 и устанавливает его в единичное состояние. Этот сигнал осуществляет блокировку основного триггера 1, т.е. поступающие на его вход синхронизации тактовые импульсы не могут принести основной триггер

1 в нулевое состояние и таким образом на единичном выходе основного триггера 1 сохраняется единичный сигнал до прихода на управляющий.вход устройства нулевого сигнала, Нулевый си гнал, поступающий на управляющий н ход устройств а, перебрасывает основные триггеры 1 и 2 в нулевое состояние H разрешает работу дополнительных триггерон

3 и 4„ которая происходит точно также, как и работа основных триггеров 1 и 2, но при этом на выходе устройства устанавливается нулевой сигнал до прихода на вход устройстна единичного сигнала. Если на устройство, находящееся в исходном состоянии, поступает. Управляющий сигнал недостаточной длительности, то спад первого пришедшето тактового импульса перебрасывает основной триггер 1 в единичное состояние, а переброс основного триггера 2 в единичное состояние может произойти по спаду следующего тактового импульса и если до его прихода на управляющем входе устройства поянляется нулевой сигнал, то основные триггеры 1 и 2 придут в исходное состояние. Одновременно дополнительные триггеры 3 и 4 перебрасываются в нулевое состояние ° Однако спадами днух последующих тактовых импульсов они возвращаются н единичные состояния. При этом на выходе устройства сохраняется нулевый сигнал, Экспериментальная проверка показала, что в предложенном устройстве для подавления помех количество исправляемых ошибок повышается в дна раза по сравнению с известным устройством.

Устройство для подавления помех по авт.св.Р519857,о т л и ч а ю щ е ес я тем, что, с целью повышения помехоустойчивости, в него введены два дополнительных триггера, соединенные также, как и два основных триггера, и три элемента ИЛИ-НЕ, причем входы синхронизации первых основного и дополнительного триггеров объединены и являются входом синхронизации устройства, первый элемент

698128

Составитель И. Грачева

Редактор И.Нестерова Техред И. Асталош Корректор Е.Лукач

Заказ 6567/18 Тираж 1060 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий.

113035, Москва, Ж-35, Рау аская наб., д.4/5

Филиал IIIIII Патент, r. Ужгород, ул. Проектная, 4

ИЛИ-НЕ двумя входами подключен к входу раздельной установки в 0 первого основного триггера и является унравляюцим входом устройства, выход первого элемента ИЛИ-НГ соединен с входом раздельной установки в 0 первого дополнительного

5 триггера, второй элемент ИЛИ-НЕ первым входом подключен к выходу второго основного триггера, вторым входом - к выходу третьего элемента

;ИЛИ-НЕ и является выходом устройства, выход второго элемента ИЛИ-НЕ; соединен с первым входом третьего элемента ИЛИ-НЕ, второй вход которого соединен с выходом второго дополнительного триггера.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

М519857, кл. Н 03 К 5/153, 1974 (прототип).