Устройство для преобразования двоичных чисел в двоично- десятичные

Иллюстрации

Показать всеРеферат

Союз Советскнк

Соцналнстнческнк

Республик (»)6995!9 (6!) Дополнительное к авт. свид-ву— (22) Заявлено 20.06.77 (2l ) 2497764/18-24 с присоединением заявки РЙ (23) Приоритет—

Опубликовано 25.11.79.Бюллетень ¹43

Дата опубликования описания 30,11,7 ) (5!)М. Кл.

G 06 Р 5/02

Гасударственный кюмктет

СССР ва делам кзобретвнкй в открыткй (53) УДК681,325 (088. 8) (72) Автор изобретения

В. И. Смельченко

Таганрогский радиотехнический институт им. В. Д. Калмыкова (7!) Заявитель (54) УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ДВОИЧНЫХ ЧИСЕЛ

В ДВОИЧНО-ДЕСЯТИЧНЫЕ

Изобретение относится к области автоматики и цифровой вычислительной техники и может быть использовано в преобразующих устройствах, специализированных вычислительных устройствах и вычислительных машинах.

Известно устройство для преобразования двоичных чисел в двоично-десятичные, содержащее запоминающий блок эквивалентов, переключатель эквивалентов, 10 формирователь эквивалентов, двоичный вычитатель с регистром сдвига fl).

Недостатком известного устройства является ere сложность.

Ближайшим к предлагаемому устройстlS ву по технической сущности является устройство для преобразования двоичных чисел в двоично-десятичные, содержащее блок управления, первый вход которого соединен с шиной управления, переключатель эквивалентов, вход которого соединен с первым выходом блока управления, запоминающий блок эквивалентов, вход которого соединен с выхоцом переключа2 теля эквивалентов, первый и второй формирователи эквивалентов, вход первого из которых соединен с выходом запоминающего блока эквивалентов, блок сравнения, первый вход которого соединен с выходом первого формирователя эквивалентов, а второй вход — со вторым выходом блока управления, группу триггеров, двоично-десятичный шифратор, двоичный вычитатель и регистр сдвига, вход которого соединен с выходом двоичного вычитателя, первый выход — c первым входом двоичного вычитателя, а второй выход— с третьим входом блока сравнения (2).

Недостатком данного устройства является относительно большой объем аппаратуры.

Цель изобретения - упрощение устройства.

Это достигается тем, что устройство содержит элемент ИЛИ, входы которого соединены с выходами блока триггеров и первыми входами второго формирователя эквивалентов, а выход соединен со вто699

15 г0

3О

45

50 рым входом блока управления, входы двоичцо-десятичного шифратора соединены с выходами блока сравйения, а выходы— со входами триггеров группы, вьгход второго формирователя двоичных эквивалентов соединен со вторым входом двоичного вычитателя, а второй вход — с выходом запоминающего блока двоичных эквивалентов.

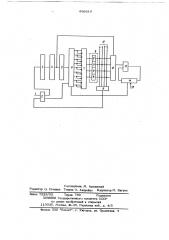

На чертеже представлена функциональная схема предлагаемого устройства.

Устройство содержит шину 1 управления, блок 2 управления, переключатель 3 эквивалентов, запоминаюший блок 4 эквивалентов, первый формирователь 5 эквивалентов, блок 6 сравнения, двоично-десятичный шифратор 7, группу 8 триггеров, состоящую из четырех триггеров 9, выходные шины 10, элемент ИЛИ 11, второй формирователь 12 эквивалентов, двоичный вычитатель 13, регистр 14 сдвига, входную шину 15.

Шина 1 управления предназначена для автономного пуска устройства. Блок 2 управления вырабатывает импульсы, необ- 5 ходимые для функционирования всего устроиства. Переключатель 3 эквивалентов предназначен для выборки необходимого эквивалента из запоминаюшего блока 4-.

Запоминающий бнок 4 хранит 1 двоичных эквивалентов вида (0,1....0,01....1,10....) по одному для каждого разряда, первый формирователь 5 двоичных эквивалентов формирует для каждого разряда двоичнодесятичного числа девять двоичных эквивалентов, блок 6 сравнения сравнивает содержимое регистра 14 сдвига с двоичным эквивалентом разрядов, двоично-десятичный шифратор 7 формирует код тетрады двоично-десятичного числа по признакам, поступающим из блока 6 сравнения группы 8 триггеров, хранит код тетрады двоично-десятичного числа. Выходные шины 10 предназначены для выдачи результата преобразования, элемент ИЛИ

11 формирует сигнал для повторного пуска блока 2 управления и считывания двоичного эквивалента j --го разряда на второй формирователь 12 двоичных эквивалентов. Регистр 14 сдвига сдвигает и хранит результаты вычислений. Входная шина 15 предназначена для записи двоичного числа, подлежащего преобразованию.

Преобразование осушествляется путем определения двоичных эквивалентов, для которых справедливо неравенство

ЪЭ. (Ч-1)519 4 с последующим определением разностей

5 (Н) 11) где А — содержимое регистра 14 сдвига;

Я„- двоичный эквивалент; номер десятичного разряда; — десятичная цифра.

Устройство работает следующим образом.

По шине 1 поступает сигнал, который запускает блок 2 управления, вырабатываюший сигналы„необходимые для автономного функционирования устройства.

Одновременно по входной шине 15 поступает преобразуемое двоичное число.

Регистр 14 сдвига обеспечивает хранение и выдачу на З-й вход блока 5 сравнения исходного двоичного числа, а далее частичных разностей А1 . На первый вход блока сравнения в каждом цикле подаются поочередно девять двоичных эквивалентов десятичных чисел вида з "= о цо-")

jj 1

Эти эквиваленты вырабатываются первым формирователям 5 эквивалентов. Выборку эквивалентов осуществляет блок 2 управления. В исходном положении блок

2 управления установлен на выборку максимального двоичного эквивалента. Затем возбуждаются шины меньших по величине эквивалентов. Последовательность выдачи эквивалентов определяется значением К: для правильных дробей (-1, 2 ... 1с ), для целых чисел — ()(—.1), (4 -2) -..О.

Первый и второй формирователи 5 и

12 позволяют хранить в запоминающем устройстве 4 по одному двоичному эквиваленту на один десятичный разряд.

Блок 6 сравнения возбуждает те выходы, для соответствующих двоичных эквивалентов которых справедливо неравенство А(,„„1 ) Э„.. При этом сигналы, вырабатываемые блоком 6 сравнения поступают на двоично-десятичный шифратор 7, который выбирает старший эквивалент и формирует тетраду преобразованного двоичного числа. Сформированная тетрада поступает с двоично-десятичного шифратора

7 на блок 8 триггеров.

В случае наличия единичного" состояния хотя бы одного из триггеров 9 элемент ИЛИ запускает бпок 2 управления, который вырабатывает сигналы для повторного считывания того же двоичного

Ю эквивалента из запоминаюшего устройства, поступающий на первый вход второго формирователя 12 эквивалентов. Тетрада

3 < )j9(3 преобразованного двоцчпо-десятичного числа поступает на входы второго ф.>рлитрователя 12 эквивалентов, вырабатывая двоичный эквивалент тетрады

Э,, =,. (о+к)

Код преобразованной тетарды снимается с шин 10, а ее двоичный эквивалент

Э „поступает с выхода второго формирователя 12 на второй вход двоичного 10 вычитателя 13. Так как блок сравнения 6 выработал сигнал, удовлетворяющий неравенству A s, > Э„.), то операция вычитания двоичного эквивалента Э „ из двоичного числа (далее из частичной раз- 15 ности А) возможна.

Описанный процесс преобразования повторяется в последующих (— 1) циклах.

При этом в каждом цикле выделяется очередная тетрада. Число циклов преобра- 20 зования определяется точностью преобразованного двоично-десятичного числа.

Таким образом, предлагаемое устройство позволяет сократить число триггеров блока 8 триггеров с девяти до четырех.

Так как второй формирователь двоичных эквивалентов сразу формирует эквивалент преобразованной тетрады, то нет необходимости в формировании всех девяти двоичных эквивалентов, как нет необходимости и в блоке элементов И. Повторное считывание двоичных эквивалентов вида

+К

l0 из запоминающего устройства позволяет при том же времени преобразования устранить линию задержки, с числом элементов, определяемых разрядностью двоичного эквивалента, считываемого из запоминающего устройства.

Формула изобретения

Устройство для преобразования двоичных чисел в двоично-десятичные, содер >3 "> 6 жми;о бл )K управления, лого и л.ш к.— торого соединен с шиной упр:я лс пля, цс.— реключатель эквнвалентов, вк p к, т,.рого соединен с первым выходом блока управления, запоминающий блок эквивалс птов, вход которого соединен с выходол переключателя эквивалентов, первый и второй формирователи эквивалентов, вход первого из которых соединен с выходом запоминаюшего блока эквивалентов, блок сравнения, первый вход которого соединен с выходом первого формирователя эквивалентов, а второй вход — co вторым выходол блока управления, группу триггерса, äâîè÷íî-.десятичный шифратор, двоичный вычитатель и регистр сдвига, вход которого соединен с выходом двоичного вычитателя, первый выход — с первым входом двоичного вычитателя, а второй выходс третьим входом блока сравнения, о тличающееся тем,что,сцелью упрощения устройства, она содержит элемент ИЛИ, входы которого соединены с выходами блока триггеров и первыми входами второго формирователя эквивалентов, а выход соединен со вторым входом блока управления, входы двоично-десятично-го шифратора соединены с выходами блока сравнения, а выходы — со входами триггеров группы, выход второго формирователя двоичных эквивалентов соединен со вторым входом двоичного вычитателя, а второй вход — с выходом запоминающего блока двоичных эквивалентов.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

% 395831, кл. G 06 F 5/02, 1971.

2. Авторское свидетельство СССР

No 523406, кл. G 06 Р 5/02, 1973.

699519

Составитель М. Аршавский

Редактор О. Стеннна Техред О. Андрейко Корректор М. Вигула

Заказ 7228/52 Тираж 780 Подписное

UHHHFIH Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4