Преобразователь двоичного кода в двоично-десятичный

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскик

Социалистических

Респубаик (iii699520 (61) Дополнительное к авт. свид-ву (51)M; Кл. (22) Заявлено 18.07.77(21) 2508753/18-24 с присоединением заявки М (23 ) Приоритет

G 06 F 5/02

Гваудврстаюнньй нвивтат

СССР ва делам нзабратаннй в аткритнй

Опубликовано 25.11,79. Бюллетень J% 43

Дата опубликования описания 30.11.79 (53) УДК 681.325 (088. 8) (72) Автор изобретения

В. И. Омельченко (71) Заявитель

Таганрогский радиотехнический институт им. В. Д. Калмыкова (54) ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА

В ДВОИЧНО-ДЕСЯТИЧНЫЙ

Изобретение касается автоматики и цифровой вычислительной техники и может быть использовано при построении устройств преобразования информации.

Известно устройство для преобразования двоичного кода в двоично-десятичный, содержащее одноразрядный двоичный сумматор, регистр сдвига, вход которого соединен с выходом сумматора, а выход— со входом сумматора, блок управления, 1О выход которого соединен со входом регистра сдвига, регистр двоично-десятичного числа, элемент И выделения тетрады, выход которого соединен со входом регистрра двоично-десятичного числа 11). ..Однако, в этом устройстве низко быстродействие, т.к. время преобразования прямо пропорционально числу разрядов двоично-десятичного числа и преобразование повторяется И циклов.

Наиболее близким по технической cymности к предложенному является преобразователь„содержащий регистр сдвига, первый одноразрядный блок умножения на десять, вход которого соединен с выходом регистра сдвига, блок управления, первый выход которого соединен со входом регистра сдвига, первый элемент И выделения остатка, первый вход которого соединен со вторым выходом блока управления. первый элемент И вьщеления тирады, первый вход которого соединен с выходом .первого одноразрядного блока умножения . на десять и вторым входом первого элемента И вьщеления остатка, а второй вход —.с третьим выходом блока управц ния, регистр двоично-десятичного числа, первый вход которого соединен с выходом первого элемента И вьщеления тетрады (2J.

Недостатком этого устройства является относительно невысокое быстродействие, связанное с необходимостью И пиклов преобразования для получения )т -разрядного результата.

Цель изобретения — увеличение быстродействия преобразователя. з 6995

Для этого on дополнительно содержит (И -1) одноразрядный блок умножения на десять (где и — число разрядов двоично-десятичного кода), (П -2) элемента

И выделения остатка, (г1-1) элемент

И выделения тетрады, первые входы которых соединены с выходами соответствующих одноразрядных блоков умножения на десять, вторые входы соединены с третьим выходом блока управления, а выходы - с соответствующими входами регистра двоично-десятичного числа, первый вход j -го (1 = 2- (п-1) элемента И вьщеления остатка соединен с (1 +2)-м выходом блока управления, второй вход соединен с выходом 1 -го одноразрядного блока умножения на десять, а выход соединен со входом (3 +1)-го одноразрядного блока умножения на десять.

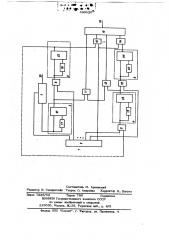

На чертеже изображена структурная схема преобразователя.

Устройство. содержит управляющую шину. 1, блок 2 управления, одноразрядные блоки умножения на десять 3-6, регистр

7 сдвига, элементы И 8-10 вьщеления остатка, элементы И 11-14 выделения тетрады, регистр 15 двоично-десятичного числа, выходные шины 16„элементы

17-20 задержки, одноразрядные сумма30 торы 21-24, входную шину 25.

Управляющая шина 1 предназначена для пуска преобразователя. Блок управления 2 вырабатывает ряд последовательностей импульсов, по 0; — 0 g< в каж35 дой, для вьщеления остатка 0 и одну IIo» следовательность импульсов Оп - 0 >,+,3 для, вьщеления тетрад двоично-десятичного числа, где a - число разрядов преобразованного числа, г1 — число раз40 рядов преобразуемого двоичного числа. Элементы задержки 17-20 на два такта смешают влево информацию, поступающую с предыдущего сумматора. Элементы И выделения остатка 8-10 предназ- 45 начены для вьщеления младших разрядов произведения. Одноразрядные сумматоры

21 — 24 суммируют информацию, поступающую на первые и вторые их,входы, регистр 7 сдвига хранит и сдвигает преобразуемое двоичное число. Элементы И

11-14 выделения тетрады предназначены для выделения тетрад двоично-десятичного числа одновременно, входная шина 25 предназначена для записи исход- 55 ного двоичного числа. Регистр 15 двоично-десятичного числа хранит преобразованное двоично-десятичное число. Выходные шины 16 предназначены для выдачи

20 4 преобразованной двоично-десятичной дроби. Для определения тетрад двоично-десятичной дроби в преобразователе используется метод последовательного умножения двоичной дроби на постоянную величину 10/16, т.е. 0,1010, вьщеления.иэ полученного произведения старших четырех разрядов, представляющих тетраду старшего разряда двоично-десятичной дроби, а младшие разряды произведения вновь умножаются на 0,1010.

Предлагаемый преобразователь работает следующим образом.

Двоичная дробь, подлежащая преобразованию, вводится в регистр 7 сдвига по входной шине 25 (последовательным или пареллельным кодом), старший разряд и -разрядной двоичной дроби находится во втором справа разряде сдвигающего регистра, младший разряд в крайнем левом разряде регистра, а первый разряд (справа) регистра, находится в нулевом состоянии. Сигнал, поступающий по управляющей шине 1, запускает устройство управления 2, которое вырабатывает 1 последовательностей сдвигаюших импульсов, поступающие на элемен« ты И 8-10 выделения остатка и одну последовательность выделения тетрады, поступающую на элементы И 11-14 выделения тетрады. При этом число импульсов в последовательности сдвигаюших импульсов на каждый последующий элемент И выделения остатка на один меньше и начинается эта последовательность на такт позже .последовательности импульсов, поступающих на каждый предыдущий элемент И вьщеления остатка. Таким образом, последовательность импульсов определяется для каждого элемента И выделения остатка соотношением

И-1

Последовательность импульсов, поступающая на управляющие входы элемента И вьщеления тетрадьг 11-14, одна и содержит четыре импульса

" + .ь

С выхода регистра 7 сдвига разряды, преобразуемой двоичной дроби поступают на вход первого одноразрядного блока 3 умножения на десять, состоящего из двоичного сумматора 21 н первого элемента задержки 17. С выхода элемента

17 задержки задержанный на два разряда код двоичной дроби поступает на второй вход того же сумматора 21. С выхода каждого предыдущего сумматора инфог ация поступает на первый вход не5 69 посредственно и задержанная на два такта — на второй вход последующего одноразрядного сумматора. Поступление информации на каждый последующий сумматор производится на один такт позже (что обусловлено задержкой предыдущего сумматора). С выхода каждого сумматора разряды полученные таким образом сумм соответствуют разрядам произведений преобразуемой двоичной дроби (в первом одноразрядном сумматоре 21) либо остатков О1 в последующих на 0,1010.

Через (1 -1) тактов сдвига происходит выделение последнего остатка произведения. Выделенные элементами И 11-14, начиная со старшей тетрады, записываются в регистр 15 двоично-десятичного числа по соответствующим импульсам из последовательности U > — U . На этом процесс преобразования заканчивается.

Выдача результата производится по выходным шинам 16. В с оответс вии с вьпцеизложенным слецует, что время преобразования двоичной дроби в двоично-десятичную дробь в предлагаемом устройстве ппределяется соотношением

Т= <.l1 где t — длительность тактирующего импульса.

Следовательно, оно в i раз меньше времени преобразования известного устройства (2).

9520 6

И выделения остатка, первый вход которого соединен со вторым выходом блока управления, первый элемент И вьщелення тетрады, первый вход которого соединен с выходом первого одноразрядного блока умножения на десять и вторым входом первого элемента И выделения остатка, а второй вход — с третьим выходом блока управления, регистр двоично-десятичного !

О числа, первый вход которого соединен с выходом первого элемента И выделения тетрады, о т л и ч а ю ш и йс я тем, что, с целью увеличения быстродействия преобразователя он дополнительно содержит (п-1) одноразрядный блок умножения на десять (где rl — число разрядов двоично-десятичного кода), (И-2) элемента И выделения остатка, (tl -1) элемент И выделения тетрады, первые входы которых соединены с выходами соответствующих одноразрядных блоков умножения на десять, вторые входы соеди.нены с третьим выходом блока управления, а выходы — с соответствующими входами регистра двоично-десятичного числа, первый вход j -го (1 = 2(h-1) элемента И выделения остатка соединен с (1+2)-м выходом блока управления, второй вход соединен с вы30 ходом i --го одноразрядного блока умножения на десять, а выход соединен со входом (1 + 1)-го одноразрядного блока умножения на десять. формула изобретения

Преобразователь двоичного кода в двоично-десятичный, содержащий регистр сдвига, первый одноразрядный блок умножения на десять, вход которого соединен с выходом регистра сдвига, блок управления, первый выход которого соединен со входом регистра сдвига, первый элемент

Источники информации, принятые во внимание при экспертизе

1. Сухомлинов М. Н., Выхованец В. И.

Перевод десятичных целых чисел в двоичные и двоичной дроби в десятичную. ао

Математическое моделирование и электрические цепи . Киев, 1967, вып. 1.

2. Авторское свидетельство СССР и 226258, кл. G 06 F 5/02, 1968.

Составитель М. Аршавский

Редактор Н. Сапирштейн Техред О. Андрейко Корректор М. Вигула

Заказ 7228/52 Тираж 780 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент", г. Ужгород, ул. Проектная,.4