Устройство для синтеза речи

Иллюстрации

Показать всеРеферат

о п и }()-,} }>(е<

ИЗОБРЕТЕНИЯ

Союз Советсмих

Соцмалнстим вских

Республнк

<>»699545

К АВТОРСКОМУ СВИДЕТИЗЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявле}}о 21.11.77 (21) 2545359/18-10 с присос(инением заявки ¹ (23) Приоритет —— (51) М. Кл .

< ) 10 L l!>10

Государственно}й комктет

СССР по делам кзооретенкй и открытий

Оп) б, }иконано 25>.11.7<). I;lo, Iri(I < }}ь llo 43 (53) УЛК 531.1(088.8) ((},;! >их б.}ик»i i}III}«>*,;и< a}III}I 05.12.79 (72) Автор изобретения

1. П. Токмаков (7 l ):С а я (} и тел ь (5-) } У(.1 РОЙС.ТВО, 1.}1Я (.111-1ТЕЗ.А РГ}-1И

Изобрете;}и(о; }}оситея к приборостроению и Moi} }!епо. } ьзо вано;(. Iя вывода информации I, ы:I!}or}è Tåëü}IO}I ма}пи}п !.

Извес}}ю )сгройетво для синтеза речи, в котором фонемный код преобразуется в акустические сиги;}лы (1(Однако В этом > < тройГ! Ве и(. x ÷HTûÂÿ(>T< я влияние с< едниx зыков, что ухудн}ает качество воспроизво.(имых слов.

Известно также устройство для синтеза речи, содержашее форматный цифровой синтезатор, запоминающее устройство, сдвиговые регистры и блок управления (21.

Одноуровневая организация управляющей информации в этом устройстве усложняет алгоритмы управления процессом синтеза речи, что сказывается на качестве синтезируемой речи.

Цель изобретения — повышение качества синтезируемой речи.

Это достигается тем, что в устройстве для синтеза речи запоминаюшее устройство выполнено в виде трехступенчатой иерархической системы, каждая ступень которой содержит входной сдвиговыи регистр, ассоциативный накопитель, блок посто»}!.>:.,:: памяти, к выходу которого подключ II }(,> ходной сдвиговый регистр, и схемы еo}III Iдения. первые входы которых соединены е

S выходом последней ячейки входного p(.II}<:rра, вторые входы — — с выходами ассоциативного накопителя. а выходы — с входамп блока постоянной памяти. Управляюпнl<

Входы регистров и ассоциативных накопи г(.лей подключены к блоку управления. Вхог(10 ной сдвиговый регистр второй ступени Выполнен из треx ячеек, причем параллельный

Вход третьей ячейки соединен с выходом первой ячейки выходного регистра третьей ступени.

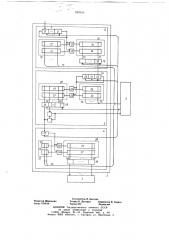

На чертеже изображена структурная

15 схема устройства для синтеза речи.

Устройство для синтеза речи содержит формантный цифровой синтезатор 1, sailoминающее устройство 2, выполненное в вид« трехступенчатой иерархической системы.

20 к которой подключен блок 3 управл Ill!}i.

Трехступенчатая иерарх«}еская ail< гсм.i памяти состоит из первой ступени 4, Втор и ст)пени 5 и третьей ступени 6. Третья т)699545

ЭЮ

И пень 6 содержит входной сдвиговый регистр 7, параллельный вход первой ячейки 8 которого является входом устройства, управляющий вход подключен к блоку 3 управления, а выход последней ячейки 9 соединен с последовательным входом первой ячейки 8, ассоциативный накопитель 10, шины 11 опроса числовых ячеек 12 которого подключены к блоку 3 управления. Входы схем 13 совпадения подключены к выходу последней ячейки 9 входного регистра 7 и к выходам ассоциативного накопителя, а их выходы— к входам разрешения считывания числовых ячеек 14 блока 15 постоянной памяти. Выходной сдвиговый регистр 16 соединен с шинами 17 считывания блока 15 постоянной памяти. Управляющий вход этого регистра подключен к блоку управления 3, а выход первой ячейки 18 является выходом третьей ступени. Вторая ступень 5 содержит входной сдвиговый регистр 19, состоящий из первой ячейки 20, второй ячейки 21 и третьей ячейки 22. Параллельный вход третьей ячейки 22 подключен к выходу третьей ступени 6, управляющий вход подключен к блоку 3 управления, а последовательный вход третьей ячейки 22 соединен с выходом первой ячейки 20.

Шины 23 опроса числовых ячеек 24 ассоциативного накопителя 25 подключены к блоку 3 управления. Входы схем совпадения 26 — к выходам ассоциативного накопителя 25 и к выходу первой ячейки 20 входного регистра 19. Входы разрешения считывания числовых ячеек 27 блока 28 постоянной памяти соединены с выходами соответствующих схем 26 совпадения. Выходной сдвиговый регистр 29 подключен к шинам 30 считывания блока 28 постоянной памяти, а управляющий вход этого регистра соединен с блоком управления. Выход первой ячейки регистра 31 является выходом второй ступени 5. Первая ступень 4 содержит входной сдвиговый регистр 32, параллельный вход которого соединен с выходом второй ступени, а управляющий вход — с блоком управления. Шины 33 опроса числовых ячеек 34 ассоциативного накопителя 35 также подключены к блоку управления. Входы схем

36 совпадения — к выходам соответствующих числовых ячеек 34 и к выходу входного регистра 32. Входы разрешения считывания числовых ячеек 37 блока 38 постоянной памяти соединены с выходами соответствующих схем 36 совпадения. Выходной сдвиговый регистр 39 соединен с шинами 40 считывания блока 38 постоянной памяти. Параллельный выход этого регистра, который является выходом трехступенчатой иерархической системы 2 памяти, подключен к цифровому синтезатору 1 речи.

Устройство работает следующим образом.

Управление процессом синтеза речи осуществляется по иерархическому принципу.

Первая ступень 4 трехступенчатой иерархической системы 2 памяти управляет цифровым синтезатором 1 речи. В числовых ячейках 37 блока 38 постоянной памяти записаны параметры квазистационарных участков речевого сигнала, которые являются управляющими параметрами для цифрового синтезатора 1 речи, а в соответствующих числовых ячейках 34 ассоциативного накопителя 35 записаны коды этих квазистационарных участков речевого сигнала.

Вторая ступень 5, которая управляет первой ступенью 4, выдает последовательность кодов квазистационарных участков речевого сигнала, соответствующих той или иной части фонем, которые записаны в числовых ячейках 27 блока 28 постоянной памяти, а в соответствующих числовых ячейках 24 ассоциативного накопителяД записаны коды тех или иных участков фонем. Последовательность кодов (записаны в числовых ячейках 14 блока 15 постоянной памяти) фонем синтезируемых слов поступает с выхода третьей ступени 6 трехступенчатой иерархической памяти, а в соответствующих числовых ячейках 12 ассоциативного накопителя 10 записана последовательность кодов букв синтезируемых слов. Последовательность байтов, составляющих синтезируемое слово, поступает на вход устройства.

После поступления каждого байта производится последовательный поразрядный опрос ассоциативного накопителя 10 с одновременныы M сдв и го м содержи мого входного сдвигового регистра 7, который работает при этом в кольцеьом режиме. Для этого с блока 3 управления на шины 11 опроса ассоциативного накопителя 0 поступают импульсы опроса, а на управляющий вход регистра 7 — тактовые импульсы сдвига.

Если содержимое входного сдвигового регистра 7 и некоторой числовой ячейки 12 ассоциативного накопителя 10 не совпадают, то производится сдвиг содержимого входного сдвигового регистра 7 на одну ячейку, при этом первая ячейка обнуляется. При поступлении очередных байтов цикл повторяется пока не происходит совпадение содержимых входного регистра 7 и некоторой числовой линейки 12 ассоциативного накопителя 10. При этом схема 13 совпадения этой числовой ячейки 12 возбуждает вход разрешения считывания соответствующей числовой ячейки 14 блока 15 постоянной памяти, и по шинам 17 считывания в выходной сдвиговый регистр 16 считывается содержимое этой числовой ячейки. Выходной сдвиговый регистр 16 третьей ступени 6, входной сдвиговый регистр 19 второй ступени 5 и блок 3 управления формируют из последовательности кодов фонем, поступившей из числовой ячейки 14 блока 15 постоянной

699545 памяти, либо коды начальных участков фонем в начале слова, либо коды собственно фонем, либо коды переходных участков между фонемами, либо коды конечных участков фонем в конце слова. При этом с блока 3 управления на первую ячейку 18 выходного сдвигового регистра 16 поступает разрешающий импульс и ее содержимое параллельным кодом считывается в третью ячейку 22 входного сдвигового регистра 19 второй ступени 5.

После этого производится сдвиг содержимого выходного сдвигового регистра 16 на одну ячейку. В результате во входном регистре 19 второй ступени 5 будет записай код начального участка первой фонемы синтезируемого слова. Затем производится последовательный поразрядный опрос ассоциативного накопителя 25 второй ступени с одновременным сдвигом содержимого входного сдвигового регистра 19, работающего в кольцевом режиме. С соответствующей числовой ячейки 27 блока 28 постоянной памяти в выходной регистр 29 считывается последовательность кодов квазистационарных участков речевого сигнала, из которых состоит начальный участок первой фонемы синтезируемого слова. После сдвига содержимого регистра 19 еще на одну ячейку в нем будет записан код участка собственно фонемы, пос,;с чего снова считывается содержимое первой ячейки 18 выходного регистра 16 в третью ячейку 22 регистра 19. Происходит формирование кода переходного участка между первой и второй фонемами синтезируемого слова. После считывания кода последней фонемы с первой ячейки 18 регистра 16 и сдвига его содержимого на одну ячейку во входном регистре 19 второй ступени будет записан код конечного участка последней фонемы. Далее, аналогичным образом, производятся все операции, связанные со считыванием последовательности кодов квазистационарных участков речевого сигнала, из которых состоит этот конечный участок последней фонемы синтезируемого слова. Коды квазистационарных участков речевого сигнала, составляющие те или иные части фонем синтезируемого слова, состоят

1О

1s

3О

3Е

3$

40 из двух частей. Первая часть кода является номером квазистационарного участка рече- и вого сигнала из всей совокупности квазистационарных. участков речевого сигнала учебной выборки, а вторая часть кода количеством необходимых воспроизведений этого участка при синтезе некоторого участка фонемы. Такая кодировка обусловлена соображениями сокращения необходимого количества ячеек блока 28 постоянной памяти второй ступени, так как нередко, особенно в случае стационарных фонем, встречается последовательность почти одинаковых- квазистационарных участков, для которых рациональнее использовать одну ячейку блока

28 постоянной памяти второй ступени, указав количество необходимых считываний в этой же ячейке. Информация, содержащая код номера квазистационарного участка речевого сигнала переписывается во входной регистр 32 первой ступени. Содержимое соответствующей ячейки 37 постоянной памяти

38 считывается в цифровой синтезатор речи. .Использование в качестве запоминающего устройства трехступенчатой иерархической системы памяти позволяет сократить объем необходимой управляющей информации и упростить алгоритм управления процессом синтеза речи. Применение в ступенях трехступенчатой иерархической системы памяти ассоциативных накопителей обеспечивает эффективный поиск необходимой информации для управления синтезом речи. Подключение входного сдвигового регистра на входе третьей ступени позволяет выделить слова из непрерывной последовательности кодов букв, поступающих из ЭВМ. Постоянная память в третьей ступени обеспечивает эффективный перевод буквенной записи синтезируемых слов в фонетическую. Выходной сдвиговый регистр третьей ступени и входной сдвиговый регистр второй ступени с помощью управляющих сигналов с блока управления обеспечивают анализ последовательности фонем, поступающих с числовых линеек и постоянной памяти третьей ступени, по весьма простому алгоритму.

Формула изобретения

1. Устройство для синтеза речи, содержащее форматный цифровой синтезатор, запоминающее устройство, сдвиговые регистры и блок управления, отличающееся тем, что, с целью повышения качества синтезируемой речи, запоминающее устройство выполнено в виде трехступенчатой иерархической системы, каждая ступень которой содержит входной сдвиговый регистр, ассоциативный накопитель, блок постоянной памяти, к выходу которого подключен выходной сдвиговый регистр, 4 схемы совпадения, первые входы которых соединены с выходом последней ячейки входного регистра, вторые входы — с выходами ассоциативного накопителя, а выходы — с входами блока постоянной памяти, причем управляющие входы регистров и ассоциативных накопителей подключены к блоку управления.

2. Устройство по и. 1, отличающееся тем, что входной сдвиговый регистр второй ступени выполнен из трех ячеек, причем параллельный вход третьей ячейки соединен с выходом первой ячейки выходного регистра третьей ступени.

Источники информации, принятые во внимание при экспертизе

1. Патент США № 3530248, кл. 179-1, 1970.

2. Авторское свидетельство СССР

¹ 485492, кл. G 10 1. 1/10, 1973 (прототип). г г

699545

Редактор Шмелькин

Заказ 7234/54

Составитель В. Киселев

Техред О. Луговая Корректор Н. Горват

Тираж 452 Подписное

ЦН И И П И Государственного комитета СССР по делам изобретений н открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП сПатент», г. Ужгород, ул. Проектная, 4