Адаптивный пороговый модуль

Иллюстрации

Показать всеРеферат

Союз Советскик

Социалистических

Респубпии (iil700862

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (5} ) Дополнительное к авт. саид-ну (5! )М. Кл . (22) Заявлено 03.01.78 (21) 2566766/18-24 с присоединением заявки РЙ

G 06 F 7/00

ГееударстееннМ кеинтет

СССР а6 данаи нзееретеннИ н открытнй (23) Приоритет

Опубликовано 30.11.79. Бюллетень М44

Дата опубликования описания 30.1 }.79 (53) УДК 681.327 (088.8) (72) Автор изобретения

А. Н. Антонов (7l ) Заявитель (54) АДАПТИВНЫЙ ПОРОГОВЫЙ МОДУЛЬ

Изобретение относится к области вычислительной техники и предназначено для использования в качестве центрального элемента в обучаемых классификаторах, в частности в классификаторах неисправностей различных техничес5 ких объектов.

Известен пороговый модуль, содержащий регистр, сумматор, схему настройки и генератор (1). Недостатком его является низкое быстродействие.

Наиболее близкое техническое решение к изобретению — адаптивньй пороговый модуль, содержащий схему сравнения, сумматор, регистр, счетчик, элемент запрета, информационные входы которого соединены с выходами счетчика, }5 а запрещающий вход через первый элемент задержки соединен с входом счетчика.

Каждый разряд модуля содержит первый элемент И, счетчик, элемент запрета, информационные входы которого соединены с выходом счетчика, настроечнь и вход которого соединен с соответствующим выходом регистра, а счетный вход через элемент задержки соединен с запрещающим входом элемента запрета и с выходом первого элемента И, первый вход которого является разрядным входом устройства.

Выходы всех элементов запрета устройства соедннены с входами сумматора, выход которого является выходом устройства и соединен с первым входом схемы сравнения, второй вход которой является входом устройства и соединен с входом регистра }2}. Устройство содержит кроме того, генератор. Недостатком его является низкое быстродействие.

Целью изобретения является повышение быстродействия. Цель достигается тем, что модуль содержит элемент И, элемент ИЛИ, второй элемент задержки и, кроме того, в каждом разряде второй элемент И, элемент ИЛИ, элемент НЕ, причем первый вход элемента ИЛИ каждого разряда соединен с выходом элемента задержки, второй вход — с выходом второго элемента И, первый вход которого через элемент НЕ соединен с разрядным входом модуля. Выход элемента ИЛИ каждого разряда, кроме последнего, соединен с вторыми входами элементов И следующего разряда. Выход элемента ИЛИ последнего разряда соединен с вто700862 рым входом первого элемента задержки, Выход которого через второй элемент задержки соединен с первым входом элемента И, Второй вход которого соединен с Выходом схемы сравнения, а выход подключен к первому входу элемента ИЛИ, нторой вход которого является вторым входом модуля. Выход элемента ИЛИ модуля соединен с вторыми Входами элементов И первого разряда.

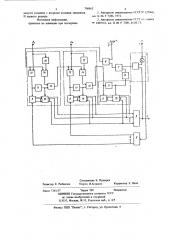

На чертеже показана схема предлагаемого модуля.

На схеме приняты следующие обозначения:

1 — первый вход модуля, 2 — второй вход мс дуля, 3 — сумматор, 4 — схема сравнения, 5— регистр, б — элемент ИЛИ, 7 — элемент И, 8— элемент задержки, 9 — счетчик, !О -- элемент запрета, 11 — элемент зздержки, 12 — элемент

ИЛИ, 13 и 14 — элементы И, »5 — элемент НЕ.

Адаптивный пороговый модуль работаст следующим образом.

При появлении иа разрядных входах Х», Х, ..., )(з комбинации ло» ичес!их единиц и нулей на вход 2 подается импульс, который через элемент 6 ИЛИ поступает на входы элементов N 13 и 14. Если на входе Х» присутствует логическая ециница, импульс проходит -срез элемс»гг Б 13, счетный вход счетчика 9 и через элемеп1 задержки 11 на вход элемента запрета 10 H один из входов элемента ИЛИ 12, При этом записанное в счетчике 9 несовсс значение в виде параллельного двоичного кода Ввод»ггся в сумматор 3.

Если на входе Х» присутствует логический нуль, пусковой импульс ".,pîõoäèò "срез элемент И 14 и без задержки поступает нз второй вход элемента ИЛИ 12, и значение веса в сумм матор не вводится, С выходя элемента ;". Л. импульс поступает на »зходы элементов . .:3 1

14 следующего разряда. Пут» прохсжде»»ия импульса по второму и последующим разр»7да.:7 аналогичпь» и зависят от значения переменной на входах этих разрядсв. C выхода 1»ос.:::,;;",»его

РаЗРЯДа ИМПУЛЬС,I»OCT)77!C» Иа СЯЕ7;-!ЫЙ В: О».. счетчика и через элеме117 зздер,;i::::, I:I ..-71-р:вая элемент запрета 10, вводит в сумм- :и 3 значени» порога, Иа этом цикл опра а разрядов ззкзг»гид-.е7сЯ. Если сигизл Z H 1 выходе .:ум»ма» с р а 3 0» . личается OT требуемо"o CH»нагла нз, «х;,де 1, схема сравнения 4 имеет на своем вь»ходе логическую единицу, и импульс с выхода элемента задержки 11 чепез элемент зацерж <11 8 1»е»»и обратной связи, элемент И 7, эл<...:;.е; ИЛИ 6 поступит вновь на вход первого разряда.

Цикл настройки повторяется, Процесс настройки заканчивается при совпздеиил HI»«л

7 на входе:умматора с требуемым аднзлом.

При этом схема сравнения 4 сигналом лог»»чес кого нуля запрещает прохождение импульса через элемент И 7. Элементы задержки в разрядах необходимы для того, чтобы перезапись в сумматор кодов из счетчиков происходила после окончания переходных процессов при счете и суммировании.

Техническая эффективнос»ь предлагаемого порогового модуля зависит от количества разрядов. С увеличением их числа экономия времени возрастает, по скажется на быстродействии устройствз, в состав которых центральным узлом входит предлагаемый пороговый модуль, 15

Формула изобретения

Ада»»тинный пороговый модуль, содержащий

26 сумматор, схему сравнения, регистр, счетчик, элемент запрета, информационные входы которого соединены с Выхьдами счетчика, а запрещающий вход через первый элемент задержки соединен с входом счетчика, каждый разряд модуля содержит первый элемент И, счетчик, элемент запрета„инфо.»мзц»ионпые входы которого соединены с Выходами счетчика, настроечный вход которого ссед»п»ен с соответству»ощим выходом регистра, счетный вход счетч»»кз через ьj элемент задержки соединен с эзпрещаюц»им входом элемента запрета и с выходом первого элемента И, первый зход которого янляетсн разрядчым Входом модуля, выходы Всех элементов запрета 1соторого соединены с входами сумматора, Выход KolopoI о является ВыхОдОм модуля и соеди-ICH с первым входом схемы сраВкили, второй вход:

gQ быстродействия, модуль содержит элемент И, элемент ИЛИ, второй элемент зздержки и, кротого в каждом разряд второй элемент И элемент ИЛИ, элемент НЕ, при-ем первый вход эасмептз ИЛИ каждого разряда соединен с вь1" " ii7of4 3iI .;меьга ззде13жк» В»срси Вход -- с ВыхОЦОм ГTOp010 элемента 11, первый вход к070рсго через элемент НЕ соединен с разрядным входом модуля, выход элемента 11ЛИ каждого разряда, .кроме последнего, ссед»п»ен с вторыми

В входами элементов И следующег .р:азряда,,выход элемента ИЛИ последнего разряда соединен вторым входом первого элемента задержки, выход которого через Второй элемент -адержки соединен с перин»м входом элемента И, второй

ВХОД КОТОРОГО СОЕДИНЕН С ВЫХОДОМ СХЕМЫ CPRBпения, а выход подключен к первому входу элемента ИЛИ, второй вход которого является вторь»м входом модуля, выход элемента ИЛИ

700862

Составитель Е. Пупырев

Ч ехред И.Асталош Корректор Е Папп

Редактор E. Рыбалова

Заказ 7381/37 Тираж 780 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д, 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 модуля соединен с вторыми входами элементов

И первого разряда.

Источники информации, принятые во внимание при экспертизе

1, Авторское свидетельство СССР N 327466, кл. G 06 F 7/00, 1972.

2. Авторское свидетельство СССР ло э явке

И 2485941, кл. 6 06 F 7/00, 16.05.71.