Устройство регистрации формы периодических коротких сигналов

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических. Республик

«»702307

3>" ) ) ,.г

75ЧМ," Кл .2" (61) Дополнительное к авт. свкд-ву (22) Замвлено 04.05.77(21) 2483655/18-21 с присоединением заявки ¹â€”

0 01 R 19/04

Государственный комитет

СССР но делам изобретений и открытий (23) Приоритет—

Опубликовано 0512.79. Бюллетень ¹ 45 (5З) УДК 621. З17. .791(088.8) Дата опубликования описания 0812.79 (72) АВТОРЫ изобретения

Н.Р. Карпов и В.К. Чепалов (71) Заявитель (54) УСТРОЙСТВО РЕГИСТРАЦИИ ФОРМЫ ПЕРИОДИЧЕСКИХ

КОРОТКИХ СИГНАЛОВ,.

Изобретение относится к области контрольно-измерительной техники и может быть использовано при анализе формы периодических коротких сигна5 лов.

Известно устройство регистрации однократных и редко повторяющихся сигналов наносекундной длительнос« ти (11 °

1О

Однако это устройство обладает малой точностью регистрации, которая определяется числом параллельных каналов преобразования временных интервалов. При попытке увеличения точности недопустимо возрастает объем обоI рудования.

Наиболее близхим по техническьй сущности к предлагаемому является устройство для регистрации формы по вторяющихся сигналов наносекундной длительности, содержащее блок синхронизации, линию задержки, блок управления, запоминающее устройство, блок вывода результатов измерения, порого- 5 вый элемент, счетчик тактов, цифроаналоговый преобразователь, причем вход линии задержки и блока синхронизации соединен с входом устройства, выход блока синхронизапии подключен к входу блока управления, выходы блока управления соединены с управляющими входами блока синхронизации, запоминающего устройства и блока вывода результатов измерений, вход которого подключен к выходу запоминающего уст» ройства, выход блока синхронизации подключен к входу счетчика тактов, выход линии задержки подключен к входу порогового элемента, выход счетчика тактов через цифроаналоговый пре-r образователь подключен к входу порогового элемента (21.

Недостатком этого устройства является большое время регистрации импульсов, ввиду того, что регистрация импульса сложной формы проходит в несколько циклов, причем каждый цикл состоит из нескольких тактов. Наличие нескольких циклов обусловлен:тем, что преобразователь временного интервала в цифровой код в каждом такте может измерять только один временной . интервал. целью предполагаемого изобретения является сокращение времени регистрации импульсов, Поставленная цель достигается тем, что в устройство регистрации формы периодических коротких сигналов, содержащее блок синхронизации, линию

702307 задержки, блок управления, запоминающее устройство,: блок вывода результатов измерения, пороговый элемент, счетчик тактов, цифроана>1оговый преобразователь, причем вход линии задержки и блока синхронизации соединен с входом устройства, выход блока синхронизации подключен к входу блока управления„ выходы блока управления соединены с управляющими входами блока синхронизации, запоминающего устройства и блока вывода результатов измерений, вход последнего подключен к выходу запоминающего устройства, выход блока синхронизации подключен K входу счетчика тактов, выход линии задержки. подключен к входу,лорогового элемента, выход счетчика тактов через цифроаналоговый преобразова-тель подключен к входу порогового элемента, введены элемент И-НЕ на два входа, два преобразователя длительности в число импульсов, каждый из которых позволяет прeoáðàçoâàòü в число импульсов длительность каждо-го из импульсов в пачке; поступанхцей на его вход, два коммутатора на и вы- 25 ходов и две группы счетчиков по и счетчиков в каждой, причем, выход порогового элемента соединен с входом первого преобразователя длительности в число импульсов и со входом элемен- 3() та И-НЕ, второй вход которого подклю- чен к выходу блока синхронизации, выход элемента И-НЕ подключен к входу второго преобразователя длительности в число импульсов, выход которого подключен к входу второго коммутатора, выход первого преобразователя длительности в число импульсов подключен к входу первого коммутатора, и выходов первого коммутатора подключены к вхо- 40 дам первой группы и счетчиков, и выходов второго коммутатора подключены к входам второй группы п счетчиков, выходы обеих групп, счетчиков подключены к входу запоминающего устройства.

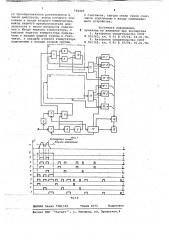

На фиг. 1 представлейа блок-cxeIta .Устройства; на фиг. 2 — эпюры напряжений, поясняющие его работу.

Устройство содержит: блок 1 син- 50 хронизации, линию 2 задержки, пороговый элемент 3, счетчик 4 тактов, цифроаналоговый1. преобразователь 5, пре- образователь .6 длительности в число импульсов, включающий в себя элемент

ИЛИ 7, линию задержки 8, линию 9 задержки, элемент И 10, элемент И-НЕ 11„ коммутатор 12, группу из и счетчиков

13-1, 13-2,...13-п, преобразователь

14 длительности в число импульсов, О коммутатор 15, группу из п счетчиков

1 6-1, 1 6-2,... 1 6-п, блок 17 управления, запоминающее устройство 18 и устройство вывода результатов измерения 19.

Исследуемый повторяющийся сигнал поступает одновременно на блок 1 синхронизации и через линию 2 задержки — на сигнальный вход порогового элемента 3. Блок 1 синхронизации вырабатывает синхроимпульс.(фиг. 2,6), Начало которого определяется передним фронтом исследуемого сигнала, а длительность синхроимпульса больше максимальной длительности исследуемого сигнала. Синхроимпульс (фиг. 2,6) поступает на вход счетчика,4 тактов, выходной код которого цифроаналоговым преобразователем 5 преобразуется в соответствующее номеру такта опорное напряжение, которое поступает на опорный вход порогового элемента 3, где сравнивается с исследуемым сигналом, поступающим с линии"

2 задержки (фиг. 2,а), изменение кода в счетчике 4 тактов происходит по заднему фронту синхроимпульса.

На выходе порогового элемента 3 образуется последовательность. импульсов нормированной амплитуды, число и расположение которых определяется формой исследуемого сигнала (фиг.2,в1

С выхода порогового элемента 3 сигнал поступает на вход первого преобразователя 6 длительности í п число импульсов, Преобразуемый. сигнал по" ступает на элемент ИЛИ 7, а с нее— на входы двух линий задержки 8 и 9.

Величина задержки линии 8 задержки

t. больше Длительности синхроимпульса с выхода блока l синхронизации, Величина задержки линии 9 задержки больше величины задержки линии 8 задержки на величину t, где д1 — величйна кванта преобразования временных интервалов, определяемая требуемой точностью регистрации.исследуемогО сигнала, Сигнал с выходов-ли» ний 8 и 9 задержки подаются на входы элемента И 10, а с выхода элемента

И 10 через элемент ИЛИ 7 — снова на входы линий 8 и" 9 задержки. Очевидно, что при подаче одного положительного импульса на вход элемента ИЛИ 7 (при условии, что его длительность не превышает величины t9) в замкнутом контуре, состоящем из элементов

7, 8, 9, 10 начинает. циркулировать положительный импульс, длительность которого с каждым циклом циркуляции уменьшается на величину ht. Циркуляция продолжается до тех пор, пока длительность импульса не станет менЬшей или равной величине nt, При этом на выходе элемента ИЛИ 7 образуется последовательность уменьшающихся по длительности импульсов, число котор-лх N равно

ы - — — у

t дС где — длительность импульса, поступающего на вход элемента ИЛЙ

702307

Формула изобретения

Устройство регистрации формы периодических коротких сигналов, содержащее блок синхронизации, линию задержки, блок управления, запоминающее устройство, блок вывода результатов измерения, пороговый элемент, счетчик тактов, цифроаналоговый преобразователь, причем вход линии задержки.,и блока синхронизации соединен с входом устройства, выход блока синхронизации подключен к входу блока управления, выходы блока управления соединены с управляющими входами блока синхронизации, запоминающего устройства и блока вывода результатов измерений, вход последнего подключен к выходу запоминающего устройства, выход блока синхронизации подключен к входу счетчика тактов, выход линии задержки.подключен к входу;.дорогового элемента, выход счетчика тактов через цифроаналоговый преобразователь подключен к входу порогового элемента, о т л и ч а ю щ е е с я тем, что, с целью сокращения времени регистрации, в него введены элемент И-HE на два входа, два преобразователя длительности в число импульсов, два коммутатора на п выходов и две группы счетчиков по и счетчиков в каждой, причем, выход порогового элемента соединен с входом первого преобразо- вателя длительности в число импульсов и с входом элемента И-НЕ, второй вход которого подключен к выходу блока синхронизации, выход элемента И-НЕ подключен к входу второТаким образом, число импульсов N пропорционально длительности преобразуемого импульса, В данном устройстве на вход преобразователя 6 длительности в число импульсов поступает несколько положительных импульсов 5 (фиг. 2,в). С выхода преобразователя

6 длительности в число импульсов при этом снимаются несколько последовательностей импульсов, следующих с периодом t> и сдвинутые друг относительно друга по времени (фиг, 2,г), С помощью коммутатора 12 эти после- довательности разделяются по разным каналам и поступают: первая последовательность (фиг. 2,д) †.на счетчик 13-1 вторая последовательность (фиг. 2,е) — на счетчик 13-2 и так далее. Таким образом, в счетчике.

13-1 окажется записанным код, пропорциональный длительности первого нм- 2() пульса, поступившего на вход преобразователя 6 длительности в число импульсов, в счетчике 13-2 — код, соответствующий длительности второго импульса, в счетчике 13-n — код, со- 25 ответствующий длительности n-ro импульса. Необходимое число счетчиков и определяется, исходя из степени сложности исследуемых сигйалов.

С помощью элемента И-НЕ 11 проис- 3() ходит подача сигнала с выхода порогового элемента 3 и его инвертирование, в результате чего формируется импульсный сигнал (фиг, 2,ж), где длительность положительных импульсов определяет длительность пауз сигнала, (фиг, 2,в). Сигнал с выхода элемента

И-HE 11 подается на вход преобразователя 14 длительности в число импульсов, устройство которого аналогично преобразователю 6. С выхода преобразЬвателя длительности в число импульсов 14 сигнал (фиг. 2,э) подается на коммутатор 15, С выхода коммутатора первая импульсная последовательность (фиг, 2,и) заполняет счетчик 16-1, вторая последовательность (фиг. 2,к) — счетчик 16-2, третья последовательность (фиг, 2,л)счетчик 16-3 и так далее, Таким образом, после окончания такта преобра=. 5О зованйя в двух группах счетчиков окажутся записанными коды, определяющие временное положение сигнала на уровне, определяемом опорным напряжением, подаваемым с цифроаналогового преобр- 59 разователя. После окончания такта .преобразования сигналами с блока 17 управления коды счетчиков 13-1, 13-2,. ° ..13-п! 16-1! 16-2! ° ° å 16"и переносятся в запоминающее устройст во 18, обе группы счетчиков устанавливаются в исходное состояние, на преобразователи 6 и 14 длительности в число импульсов подаются с блока

17 управления отрицательные импульсы, 65 устанавливающие их в исходное состояние, Поскольку отрицательным фронтом синхроимпульса код в счетчике 4 тактов увеличен на единицу, на опорном входе порогового элемента 3 уже при. сутствует опорное напряжение, соответствующее следующему такту, т.е. схема готова к следующему такту, По окончании регистрации импульса сигналом с блока 17 управления коды иэ запоминающего устройства 18 выводятся через устройство 19 вывода результатов измерения в приемлемой для анализа форме. По команде Пуск, поступающей на блок 17 управления, происходит общая начальная установка, всех устройств и начинается новый цикл преобразования.

Таким образом! весь процесс преобразования одного сигнала происходит ! за один цикл,. Длительность цикла определяется необходимым числом уровней квантования по амплитуде и периодом повторения исследуемого сигнала, 702307 е

ЦНИИПИ Заказ 7581/42 Гираж 1073 Подйи сное филиал ППП Патент, r. Ужгород, ул. Проектная,4 го преобразователя длительности в число импульсов, выход которого подключен к входу второго коммутатора, выход первого преобразователя длительности в число импульсов подключен к входу первого коммутатора, и выходов первого коммутатора подключены к входам первой группы п счетчиков, п выхоцов второго коммутатора подключены к входам второй группы и счетчиков, выходы, обеих групп счетчиков подключены к входу запоминаюЩего устройства.

Источники информаций, 5 принятые во в нимание при экспертизе

1. Авторское свидетельство СССР

Р 501363., кл. G 01 R 19/04, 30. 01. 76.

2. Авторское свидетельство СССР

Ф 501362, кл. G 01 R 19/04, 30,01.76.