Импульсный стабилизатор постоянного напряжения

Иллюстрации

Показать всеРеферат

лате нт Н0-7 e.;; н ". чес пан б, олноте.",g Ь1 БА (72) Авторы изобретений

Ю. Е Заблоцкий, В. Г. Лесной, В. С. Петренко и В Ф Ушанов (7I) Заявитель (54) ИМПУЛЬСНЫЙ СТАБИЛИЗАТОР ПОСТОЯННОГО НАПРЯЖЕНИЯ

Изобретение относится к электрораадиотехннке, а именно источникам питания и может быть использовано в систе .мах питания устройств автоматики и вычислительной техники.

Известны импульсные стабилизаторы, S содержащие регулирующий транзистор, интегрирующий фильтр, времязадаюшую цепь )1), Известен также импульсный стабилиза

10 тор постоянного напряжения, содервйший включенные последовательно в выходную> шину ограничиваюший резистор, составной регулирующий .транзистор, базой соеди« пенный с блоком управления, дроссель

;интегрйруюшего фильтра и блок зашиты с транзистором, эмиттер которого соединен с ограничивающим резистором со стороны входного вывода.

Недостатком известного стабилизато ра является то, что при ограничении пус» кового тока устройство зашиты вводят регулирующий элемент в линейный режим, что приводит к повышению рассеиваемой

2 мощности на регулирующем элементе и снижению надежности устройства, а в установившемся рФжйме весь" ток стабилизатора протекает через датчик тока что приводит к снижению KfIQ устрой» ства„ целью изобретения являются повыше ние надежности и увеличение КПД.

Для этого в импульсном стабилизато ре постоянного напряжения, содержащем вклкненные последовательно в выходную шину ограничивающий резистор, составной регулирующий транзистор, базой соединенный. с блоком управления, и дроссель интегрирующего фильтра, и блок зашиты с транзистором, эмиттер которого соединен с ограничивающим реэисторбм со стороны входного вывода;, Блок зашйты снабжен вторым транзистором и времязадаюшей цепью, причем коллектор первого транзистора соединен со вторым выводом ограничивающего резистора,"эмиттеры первого и вто рого транзисторов объединены, переход

02 367 4

15

3 7 амиттер-коллектор второго транзистора подсоединен параллельно цепи амиттербаза первого транзистора, точка соединения коллектора второго н базы первого транзистора через резистор подсоеди» непа к обшей шине, а база второго трап зистора через последовательно соединен ные резистор и конденсатор времязадающей пепи подключена к коллектору пер-, вого транзистора.

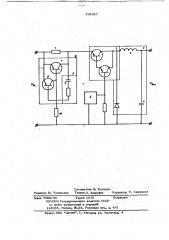

На чертеже представлен импульсный стабилизатор постоянного напряжения, алектрическая схема

Импульсный стабилизатор содержит ограничивающий резистор 1, регулирую щий составной транзистор 2, блок 3 уп равления, дроссель 4 интегрирующего фильтра 5, блок 6 защиты с транзисторами 7-8, времязадающую цепь 9, ре-. зистор 10.

Импульсный стабилизатор постоянного напряжения работает следующим образом.

При подаче1 питания ток заряда конденсатора интегрирующего, фильтра про текает через ограничивающий резистор

1 и последовательный регулирующий элемент 2. Величина этого тока ограничифается ограничивающим резистором 1.

Управляющий,,транзистор 8 открыт током заряда времязадаюшей цепочки 9, обусловленным падением напряжения на ограничивающем< резисторе 1, Транзистор 7 зашиты закрыт, так как его пере ход эмиттер-база зашунтирован открытым управляющим транзистором 8. По окончании переходного процесса ток заряда времяэадающей цепочки 9 уменьшается настолько, что Йачинает закрйжться управляющий транзистор 8. и, следователь но, открывается транзистор 7 защиты, током, ограниченным резистором 10 сме щения, Открывающийся транзистор зашиты частично щунтирует ограничиваю-, щий резистор 1, напряжение на котором становится меньше напряжения заряженного конденсатора времязадающей цепочки вследствие чего к переходу база-емиттер управляющего транзистора 8 оказывается приложенным запирающее напряжение, что приводит K опрокидыванию схемы, полному:: открытию транзистора 7 защиты и шунтированию ограничивающего резистора 1.

Таким образом, введение в схему уп-. равляющего транзистора, времязадающей цепочки, резистора смешения и их связей позволило: последовательный регулирующий элемент держать полностью открытым на момент заряда емкости интегрирующего фильтра, что приводит к повышению надежности работы регулирующего элемента, и отключать ограничива1ощий резистор в стационарном режиме, что приводит к увеличению КПД устройства на 15...2 0%.

Формула изобретения

Импульсный стабилизатор постоянного

20 напряжения, содержащий включенные последовательно в выходную шину ограничи веющий резистор, составной регулирующий транзистор, базой соединенный с блоком управления, и дроссель интегриi рующего фильтра, и блок защиты с тран-; зистором, змиттер. которого соединен с ограничивающим резистором со стороны входного вывода, о т л и ч а ю m и йс я тем, что, с целью повышения на50 дежности и увеличения КПД, блок заши- ты снабжен вторым транзистором и времяЗадаюшей цепью, причем коллектор первого транзистора соединен со вторым выводом ограничивающего резистора, З5 емиттеры-первого и второго транзисторов объединены, переход эмиттер-коллектор второго транзистора подсоединен параллельно пепи змиттер-база первого

",транзистора, точка соединения коллектоЮ ра второго и базы первого транзистора через резистор подсоединена к общей шине, а база второго транзистора через последовательно соединенные резистор и конденсатор времяэадаюшей пепи под-.

45 ключена к коллекгору первого транзистораф

Источники информации, принятые во внимание при акспертизе

1 Авторское свидетельство СССР

Ж 418842, кл. 0- 05 Р 1/56, 1971.

2. Авторское свидетельство СССР

М 536488, кл. G i05 Г 1/56, 1975.

702367

Составитель В. Косырев

Редактор Ю. Чолюканов Техред O ° Д,ндрейко ° Корректор Т. Скворнова

Закаа 7588/45 Тираж 1015 Подййсное

UHHHHH Государственного комитета СССР по делам изооретений и открытий

113035, Москва, ХМ5; Раушская наб., д. 4/5

Филиал ППП Патент, г, Ужгород, ул. Проектнан,. 4