Преобразователь прямого кода в дополнительный

Иллюстрации

Показать всеРеферат

Сею з Советских

Социалистических

Республик

i702376

l)M. Кл.

06 Г 5/02

Ваумрстввйай иацитвт

СССР аа делам изебретеиий и втирытий

З) УЙК 681 .325.53 (088.8) (72) Авторы изобретения

Ю. С,. Корнеев и Л. А, Погорелов (73) Заявитель (54) ПРЕОБРАЗОВАТЕЛЬ ПРЯМОГО КОДА В ДОПОЛНИТЕЛЪНЬЙ

Изобретение относится к области автоматики и пифровой вычислительной техники и может быть использовано при построении вычислительных устройств.

Известен преобразователь прямого кода в дополнительный, содержащий триг5 герный регистр, группы вентильных элементов для установки входного кода, группу вентильных элементов, входы которых соединены с выходами триггеров

pal HCTpB (1) .

Недостатком известного устройства является его сложность и относительно низкое быстродействие, связанное с необходимостью установки входного ко1 да, после которой следует собственно нреобраэование.

Наиболее близким техническим реше-нием к данному является преобразователь, содержащий разрядный триггерный регистр, первые установочные входы триггеров которого соединены с соответствукхцими шинами ввода прямого значения, (5-2) элементов ИЛИ, группу

2 элементов И, входы которых подключе ны к выходам триггеров регистра $2(,.

Недостатком известного преобразователя является относительно низкое быстродействие, связанное с необходимостью задержки преобразования на время первоначальной установки входного кода в регистр.

Белью предлагаемого изобретения является сокращение времени преобразования. Это достигается тем, что преобразователь содержит (И-2) элементов

И, выходы элементов ИЛИ соединены с первыми разрешающими входами триггеров с 3-го по И-ый разряд, BbIxogbl элементов И соединены с вторыми разрешающими входами триггеров 3-Fo по,g-ый разряд, шина ввода прямого значения 1-го разряда (2 -1(п) соединены со входами элементов ИЛИ во всех разрядах старше two, шина ввода инверсного значения 1-го разряда соединена со входами элементов И во всех разрядах старше т-го, первый и второй разрешао:

3 7023 Ф пие входы триггера второго разря да соединены с шинами ввода прямогс и инверсного эначейий младшего раз1 ряда соответственно, вторые установоч-ные входы триггеров со 2-го по -ый соединены с шинами ввода инверсного значения соответствующих разрядов, синхровходы всех триггеров регистра соединены- с управляющей шиной преобразователя. . 10

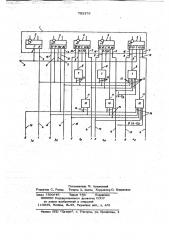

На чертеже представлена схема пре-. образователя прямого кода в дополнитель- . ный.

Преобразователь прямого кода в дополнительный содержит р -разрядный триггерный регистр 1, йервые установочные входы 2 (входы Э ) триггеров

3 которого подключены к соответствую щим шинам 4 ввода прямого значения а их синхровходы 5 (входы С) подклю- 20 чены z управляющему входу 6 преобразователя, h- 3 элементов ИЛИ 7, вы-. ,ходы 8 которых соответственно подклю чены к первым разрешающим входам .9 (входыЖ ); триггеров с 3-го по р-ый разряд, h- 2 элементов И 10, выходы 1 1 которых соответственно подключены ко вторым разрешающим входам 12 (входам\/2) триггеров 3 с 3-г по -й разряд, входы 13 элементов ИЛИ

7 и входы 14 элементов.И 10 йодк почены соответственно к шинам 4 вво. - да прямого значения и к шинам 15 ъвода инверсного значение предыдущйх разрядов, первый разрешающий вход 9 и второй. разрешающий вход 12 2-ro

Tparrepa 3 подключены соответственно. к шине 4 ввода пряма о значения и к шине 15 ввода инверсного зйачения младшего разряда; вторые установочные входы 16 (входы .Э1) со 2-гб по ф-й фиггеров 3 подключены" к сооьветствукяпим шинам 18 ввода йнверс-" "Roro значения.

Преобразователь работает следующим образом, Прямое и обратное значение пара- фазно представлейного исходного кода, который. должен быть преобразован, в виде соответствующих логических уров ней подается через ншны 4 ввода прямого значения и шины 18 ввода инверсного значения на первые установочные входы 2 и вторые установочные

:.входы 16 триггеров 3. В зависимости

SS от того, на какой иэ разрешающих входов триггеров 3 поступит Ьдищ чный, то есть раэрешакндий логиче<жий

76 уровень, будет подготовлена запись в соответствующий триггер 3 или, прямого или обратного значения соответствующего разряда исходного кода. Так, если уровень логической единицы посту-, цит на первый разрешающий вход 9, то будет подготовлена запись в триггер 3 обратного значения данного разряда ис-, ходного кода, так как вход 9 разрешает запись в триггер 3 состояния второго установочного входа 16, соединенного с шиной ввода инверсного значения 15. Если же логическая единица поступит на второй разрешаккднй вход

12, то этим будет подготовлена запись в триггер 3 прямого значения данного разряд исходного кода, так как вход

12 разрешает запись в триггер 3 со стояния первого установочного входа

2, соединенного с шиной 4 ввода прямого значения.. В зависимости от конкретного значения преобразуемого кода логическая единица поступит на вторые разрешающйе входы 12 тех, триггеров 3

3, по отношению z которым все предшествующие, более младшие разряды исходного кода содержат логические нули, В этом случае все входы 14 элемента И 10 в таком разряде преобразователя будут находиться под потенциалом логической единицы, чтО вызо -вет"появление единичного логического уровня на выходе 11 соответствующего элемента И 10 и поступление его на второй раэрашающий вход 12. При этом ни на"одном иэ входов 13 элементов ИДИ 7 в тех же разрядах не будет ни Одной единицы, следствием hiего явится появление нуля на выходе 8 элемента ИЛИ 7, поступление которого на первый разрешающий вход 9 блокируеФ возможность записи в триггер 3 состояния второго установочного вхо- да 2, соединенного с соответствующей шиной 18 ввода инверсного значения, 1

ВО всех остальных разрядах преобразователя, по отношению к которым хотя бы один из более младших разрядов ис ходного кода содержит единицу, аа выходе 8 элемента ИЛИ 7 будет иметь место логическая единица, поступление которой на первый разрешающий вход

9 подготавливает запись обратна-о зна чения данного разряда исходного. кода в соответствующий триггер 3. Запись прямых или обратных значений преобразуемого кода в соответствии с требо ваниями закона преобразования прямого

5 7023 (пополннтельного) кода в дополнительный (прямой) zon в; триттеры 3 трнггерного регистра 1 производится под воздействием импульса управляющей частоты, подаваемого через управляющий вход 6 преобразователя на счетные вхопы 5 всех триггеров 3. В самый младший разряп всегда бупет производиться запнсь прямого значения младшего разряда преобразуемого кода. 11

Таким образом, преобразование прямого кода в дополнительный и дополнительного кода в прямой осуществляется, в теченне одного чвкта управляющей частоты вместо двух тактов, необходн - 5 мых пля выполнения той же операции в известных устройствах.

25

Формула нзобре,тення

Преобразователь прямого .zona в пополннтельный, содержащий р-разрядный трпггерный регистр, первые установочные входы триггеров которого соепинены с соответствующими шинамн ввода прямого значения (И-2) элементов

ИЛИ, отличающийся тем, что, с целью сокрашения времени преоб= разовання, он сопержнт Yl.— 2 элементов

76: 6

И,выходы элементов ИЛИ соепинены с первыми разрешающими вхопамн триггеров с 3-ro по,ц-ый разряп, выхопы элементов И соединены со вторыми разрешающими вхопамн триггеров с 3-го по,h-ый разряд, шина ввопа прямого значения j -го разряпа (2+i И ) соединена со вхопамп элементов ИЛИ во всех разряпах старше j-го, шина ввода инверсного значения 1-го разряда соепннена со вхопамн элементов

И во всех разрядах старше 1-го, первый н второй разрешающие вхопы триггера второго разряпа соединены с шинами ввода прямого н инверсного значений млапшего разряпа соответственно, вторые установочные входы триггеров со 2-ro Do p-ый соепнпены с шинами ввода инверсного значеняя соответствующих разрядов, сннхровхопы всех триггеров регистра соединены с управляющей шиной преобразователя.

Источники информации, принятые во внимание прн акспертязе

1. Авторское свнпетельство СССР ¹ 185548, кл. 606 Г 5/02, 1966.

2. Авторское свидетельство СССР

l4 238225, кл, 006 Г И02, 1969 (прототип) .

702376

Составитедь М. Аршавский

Редактор С. Равва Техред 3. фанта Корректор О. Ковинская

Заказ 7590/46 Тира и 780 Подпйсное

ЦНИИПИ Государственного армитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Рауыккая наб., д. 4/5 филиал ПНП «Патент", г, Ужгород, ул, Проектная, 4