Дешифратор для запоминающего устройства

Иллюстрации

Показать всеРеферат

",. }:с« !«}!"}: } ° «,.:, 1

}}!/Ъ !" л „} !. !«1 «Дс!", х

1. -, 116 „,:,,-„,,-}} }.;„„

ОП ИСАНИЕ

ИЗОБРЕТЕН Ия

Союз Советских

Социалистических

Республик

<}}}702411

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22)Заявлено04.04.78 (21) 2600780/18-24 с присоединениеем заявки 1}в}— (23) Приоритет

Опубликовано 05.12.79, Бюллетень 11е} 45

Дата опубликования описания 08.12.79 (51)M. Кл.

Ci 11 С 17/00

Гасударственный комитет

СССР де делам кзебретевий

N еткрытнй (53) УДК 681.327. . 6(088. 8) Н. H. Журавский, А. М, Селигей и Д. С. Тростянецкий (72) Авторы изобретения

Киевский ордена Трудового Красного Знамени завод вычислительных и управляющих машин. (7I ) Заявитель (54) ДЕШИФРАТОР ДЛЯ ЗАПОМИНАЮЩЕГО

УСТ РОЙСТ BA Изобретение относится к области вычислительной техники и может быть использовано при построении устройств хранения дискретной информации.

Известны дешифраторы для ЗУ, со5 держащие координатные шины, в пересе-: чениях которых последовательно включены диоды и числовые шины 11).

Наиболее близким техническим решением к изобретению является дешифратор, содержащий координатные шины, в перекрестиях которых последовательно включены диоды и числовые шины. Дешифратор содержит также ключевые транзисторЬ1, подключенные к координатным

15 шинам, две дополнительные шины, подключенные к источнику питания и к дополнительным ключевым транзисторам, последовательно соединенным через резисторы и диоды с координатными шинами (2).

Недостатком та кого g ешифратора является необходимость перезаряда лара! зитных емкостей в промежутках между переключениями ключей. Во время перезаряда емкостей возникают помехи, снижающие надежность дешифратора и его быстродействие.

11ель изобретения — повышение надежности устройства.

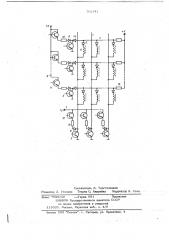

Поставленная цель достигается тем, что предложенный дешифратор содержит дополнительные диоды и резисторы, подключенные к источнику питания и через координатные шины — к- дополнительным диодам, соединенным с выходами ключевых транзисторов, На чертеже представлена принципиаль. ная электрическая схема дешифратора;

Дешифратор содержит координатные шины 1 и 2, в перекрестиях которых включены диоды 3 и числовые шины 4, и ключевые транзисторы 5 и 6.

Транзисторы 5 соединенв1 с шинами

1. Дополнительные шины 7 и 8 соедицены с диодами 9 и резисторами 10 через дополнительные ключевые транзисторы з .1 1 и 12 и непосредственно с исто шиком питания +Е. Шина 7 через транзисторы

1 2, резисторы 1 О и диоды 9 соединена с шинами 1. Шины 2 через резисторы

13 соединены с источником питания +Е и через диоды 1 4 с транзисч орами 6.

Шина 8 через транзисторы 11, реэисто— ры 10 и диоды 9 соединена с транзисторами 6.

Дешифратор работает следующим образом.

В соответствии с кодом адреса на ехоп одного из транзисторов 5 поступает йоложительный сигнал, а на вход соответствующего транзистора 12 — отрицательный сигнал. При этом данный транзистор 5 открывается, а транзистор 12 закрывается, остальные транзисторы 5 закрыты, а транзисторы 12 открыты.

Аналогично закрывается один из транзисторов 6 и открывается соответствуюший транзистор 11, остальные транзисторы 6 открыты, а транзисторы 11 закрыты. Закрытый транзистор 6 запирает соединенный с ним диод 14. На соединенной с диодом 14 шине 2 повышается напряжение, т. е. происходит возбуждение шины 2. Ток опроса возникает в одной шине 4, подключенной одним концом к возбужденной шине 2, а другим концом - к возбужденой шине 1, соединенной с открытым транзистором 5. В остальных шинах 4, подключенных к возбужденной шине 1, ток опроса не возникает, так как аноды диодов 14 имеют низкий уровень напряжения, равный падению напряжения на циодах 14 и открытых транзисторах 6. Резистор 1 3 является тбкозадающим. Диод 14, соединенный с закрытым транзистором 6, заперт и препятствует протеканию тока опроса через открытый транзистор 11, резистор l О и диод 9. Это позволяет использовать маломощные дсполнительные ключевые транзисторы 1 1, 1 2, диоды 9, резисторы 1 О.

После окончания опроса шины 4 все транзисторы 5, 11 закрыты, а все транзисторы 6, 12 открыты.

В дешифраторе обеспечивается постоянный заряд емкостей шин 4, так как шины 1 и 2 подключены через резисторы 10 и 13 к источнику питания +Е также на время переключения ключей (т. е, подключены постоянно). При этом

0211 1 уменьпгаются помехи, связапные c: перезарядом емкостей шин 4, и повышается быстродействие дешифратора, так как иэ цикла работы исключается время на успокоение помех при переключениях ключевых транзисторов.

В качестве ключевых транзисторов

5 и 12, 6 и 11 целесообразно использовать интегральные микросхемы, в ко10 торых соответствующие пары ключевых транзисторов, а также диоды 9 и резисторы 10 выполнены на одном кристалле (например, микросхемы K155ЛА6 или

К1 55ЛА1 2) . При этом значительно по-! 5 вышается степень интеграции цешифратора.

Предложенный дешифратор для ЗУ . имеет по сравнению с известными дешифраторами большие надежность, быстродействие и степень интеграции и меньшие габариты, вес и трудоемкость изготовления.

Формула изобретения

Дешифратор для запоминающего устройства, содержащий координатные шины, 30 в перекрестиях которых последовательно включены диоды и числовые шины, ключевые транзисторы, одни из которых подключены к оцним из координатных шин, две дополнительные шины, подклю- .

35 ченные к источнику питания и к дополнительным ключевым транзисторам, последовательно соединенным с резисторами и диодами, одни из которых подключены

40 к соответствующим координатным шинам, а другие - к другим Ключевым транзисторам, отличающийся тем, что, с целью повышения надежности, он содержит дополнительные диоды и резис45 торы, подключенные к источнику питания и через координатные шины к дополнительным диодам, соединенным с. выходами ключевых транзисторов.

Источники информации, принятые во внимание при экспертизе

1. Брик E. А. Техника ПЗУ. M., "Срветское радио", 1 973, с. 41 — 45, рис. З.l.е, 2. Авторское свидетельство СССР

966 кл. C 11 С 11 00, 18.03.68 (прототип).

702 !! ) Составитель Q. Тростянецкий

Редактор Л. Утехина Техред О. Андрейко . Корректор Н. Стен

Заказ 7599/48 ==:. Тираж 681 Подписное

1ШИИПИ Государственного комитета СССР по делам изобретений и открытий

1 1 3035, Москва, Раушская на 6., а. 4/5

Филиал ППГ! Патент", г. Ужгород, ул. Проектная, 4