Логический компаратор для контроля цифровых микросхем

Иллюстрации

Показать всеРеферат

ОПИСАНИ

ИЗОБРЕТЕНИ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВ

Союз Советских

- Социалистических

Республик

02 (61) Дополнительное к авт. саид-ву— (22) Заявлено 100577 (21) 2484010/18-2 с присоединением заявки Йо(23) Приоритет—

/20//

/28 Государственный комитет

СССР по делам изобретений и открытий

Опубликовано 05.1279, Бюллетень Йо

74,5 .8) 1

Дата опубликования описания 15127

IO. П. Белянин, В. A. Егоров, П, Ю. Макавеев, С. М, Портнов и Ю. Н. Сулицкий (72) Авторы изобретения (71) Заявитель (54 ) ЛОГИЧЕСКИИ КОМПАРАТОР ДЛЯ КОНТРОЛЯ

ЦИФРОВЫХ МИКРОСХЕМ

Изобретение относится к импульсной и измерительной технике, в частности, к области контроля и диагностики радиоэлектронных устройств, выполненных на цифровых микросхемах.

Известны логические компараторы для контроля цифровых микросхем (I), (2), Первый из известных компараторов, содержащий контактирующее устройство, и последовательно соединенную эталонную микросхему, элемент сравнения, элемент ИЛИ, индикатор, переключатель, триггер, не способен контролировать последовательные микросхемы, например триггеры, регистры, счетчики, а смена эталонной микросхемы производится вручную (Il .

Наиболее близким техническим решением к данному изобретению является логический компаратор для контроля цифровых микросхем, содержащий кбн..тактирующее устройство и блок регистрации t2) .

Однако этот компаратор имеет недостаточную достоверность контроля вследствие ручной смены эталонной микросхемы и связанной с ней ошибки контактнрова ния, целью изобрете ни я являетс я повышение достоверности контроля.

Для этого в логический компаратор для контроля цифровых микросхем, содержащий контактирующее устройство и блок регистрации, введены блок эталонных схем, блок выбора эталонных схем и блок развязывающих усилителей, причем выход контактирующего устройства через последовательно соединенные блок развязывающих усилителей, блок эталонных схем, блок выбора эталонных схем соединен с блоком регистрации, при этом блок эталонных схем содержит элементы сравнения, элементы ИЛИ и микросхемы комбинационного типа, входы которых подключены к соответствующим выходам блока развязывающих усилителей, а выходы — к первым входам элементов сравнения, вторые входы которых соединены с соответствующими выходами блока развязывающих усилителей, а выходы элементов" сравнения через элементы ИЛИ подключены к соответствующим входам блока выбора эталонных схем, а кроме того блок эталонных схем содержит элементы сравнения, элементы ИЛИ, двухвходовые элементы -HF. и микросхемы

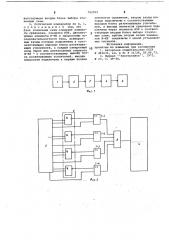

702502 устройство 1, блок 2 развязывающих усилителей, блок 3 эталонных схем, блок 4 выбора эталонных схем и блок

5 регистрации, причем блок 3 включает в себя микросхему б комбинационного типа, входы которой соединенй с выходами блока 2, в выходы — c первыми входами элементов 7=1 — 7=4

30 сравнения, вторые входы которых под35 ключены к соответствующим выходам блока 2, а выходы —: к входам элемента 8 ИЛИ, выход Которого соединен с входом блока 4, либо блок 3 включает в себя микросхему 9, асинхронные входы которой подключены к соответству 40 ющим выходам блока 2 непосредственно, а каждый синхронный вход через пары включенных последовательно двухвходовых элементов 10, 11 и 12, 13

И-HE — к соответствующим выходам блока 2, выходы микросхеьы 9 соединены 45 с первыми входами элементов 7=1

7=4 сравнения, вторые входы элементов 10-13 соединены с шинами 14 и 15 установочных сигналов.

Компаратор работает следующим образом.

Контактирующее устройство 1 надевается на проверяемую цифровую микросхему и обеспечивает съем с нее сигналов, которые поступают на вход бло- 55 ка 2, служащего для уменьшения нагрузки на проверяемую цифровую микросхему. Сигналы с выходов блока 2 ноступают в блок 3.

Входы эталонной микросхемою б или

9 присоединены к выходам блока 2 в соответствии с цоколевкой данной микросхемы, а выходы — к первым входам элементов 7=1 — 7=4. Вторые входы

Злементов 7=1 — 7=4 присоединены к и оследов атель ного типа, ас инхро нные входы которых подключены к соответствующим выходам блока развязывающих усилителей, а каждый синхронный вход через двЛ двухвходовых элемента И-НЕ к соответствующему выходу блока развязывающих усилителей, выходы микро5 схем подключены к первым входам элементов сравнения, вторые входы которых подключены к соответствующим выходам блока развязывающих усилителей, а выходы элементов сравнения подключены через элементы ИЛИ к соответствующим входам блока выбора эталонных схем, причем вторые входы элементов

И-НЕ соединены с шиной установочных сигналов.

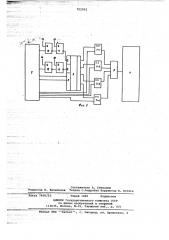

На фиг. 1 приведена схема компаратора, на фиг. 2 — схема одной из эталонных микросхем в блоке эталонных схем комбинационного типа, на фиг. 3 — схема одной из эталонных ми- 20 кросхем в блоке эталонных схем последовательностного типа.

Логический компаратор для контроля цифровых микросхем содержит включенные последовательно контактирующее 25 выходам блока 2 в соответствии с цоколевкой микросхемы б или 9. При любом несовпадении между выходными сигналами проверяемой микросхемы и эталонной микросхемы б или 9, на выходе элемента 8 появится сигнал, свидетельствующий о неисправности проверяемой микросхемы.

При контроле цифровых микросхем последовательностного типа, у которых последующее состояние зависит от предыдущего, перед проверкой необходимо установить эталонную микросхему 9 в соответствующее состояние.

Установка микросхемы 9 в исходное состояние происходит с помощью элементов 10-13 путем подачи на шину 14 уровня логического нуля, а на шину

15 — переключающих сигналов. Как только эталонная микросхема 9 будет иметь то же состояние, что и проверяемая, на шины 14 и 15 подаются- разрешающие сигналы — логические единицы н происходит сравнение проверяемой микросхемы с эталонной.

При любом несоответствии между выходными сигналами проверяемой микросхемы и эталонной микросхемы 9 на выходе элемента 8 появится сигнал, свидетельствующий о неисправности проверяемой микросхемы. С помощью блока по желанию оператора опрашивается только тот элемент 8, который отвечает за эталонную микросхему.

Сигнал с блока 4 поступает на вход блока 5, где регистрируется и индуцируется °

Формула изобретения

1. Логический компара .ор для контроля цифровых микросхем, содержащий контактирующее устройство и блок регистрации, отличающийся тем, что, с целью повышения достоверности контроля, введены блок эталонных схем, блок выбора эталонных схем и блок развязывающих усилителей, причем выход контактирующего устройства через последовательно соединенные блок развязывакщих усилителей, блок эталонных схем, блок выбора эталонных схем соединен с блоком регистрации.

2. Логический компаратор,по п ° 1, отличающийся, тем, что блок эталонных схем содержит элементы сравнения, элементы ИЛИ и микросхемы коМбинационного типа, входы которых подключены к соответствующим выходам блока развязывающих усилите- . лей, а выходы — к первым входам элементов сравнения, вторые входы кото- : рых соединены с соответствующими выходами блока развязывающих усилителей, а выходы элементов сравнения че- рез элементы ИЛИ подключены к соот702502 ветствующим входам блока выбора эталонных схем.

3. Логический компаратор по п. 1, отличающийся тем, что блок эталонных схем содержит элементы сравнения, элементы ИЛИ, двухвходовые элементы И-HE и микросхемы последовательностного типа, асинхронные входы которых подключены к соответствующим выходам блока развязывающих усилителей, а каждый синхронный вход через два двухвходовых элемента

И-НŠ— к соответствующему выходу блока развязывающих усилителей, выходы микросхем подключены к первым входам элементов сравнения, вторые входы которых подключены к соответствующим выходам блока развязывающих усилителей, а выходы элементов сравнения подключены через элементы ИЛИ к соответствующим входам блока выбора эталонных схем, причем вторые входы элементов И вЂ” НЕ соединечы с шиной установочных сигналов.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 483633, кл . G 01 R 31/28, 05.06.73.

2. Журнал . Электроника, 1973, Р 23, с. 29-36.

702502

Заказ 7608/53

Тираж 1060

Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, r. Ужгород, ул . Проектная, 4

Составитель A. Степанов

Редактор Н. Веселкина Техред O.Aíäðåéêî Корректор В. Бутяга