Устройство для дискретного экспоненциального сглаживания

Иллюстрации

Показать всеРеферат

ОП И

Союз Советских

Социалистических

Республик ()702509

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. сеид-ву— (22) Заявлено 0507.77 (21) 2503775/18-21 (51)М. Кл.2

Н 03.К 13/02 с присоединением заявки Нов

Государственный комитет

СССР по делам изобретений и открытий (23) Приоритет

Опубликовано 05.1279. Бюллетень М 45 {53) УДК 681. 325 (088.8) Дата опубликования описания 15.1279 (72) Авторы изобретения

В.. A. Соломка, Ф. И. Тищенко и Г. Л. Ноткин (71) Заявитель (54 ) УСТРОЙСТВО ДЛЯ ДИСКРЕТНОГО ЭКСПОНЕНЦИАЛЬНОГО

СГЛАЖИВАНИЯ

Изобретение относится к области измерительной техники, а именно к функциональным схемам устройств для дискретного экспоненциального сглаживания и может быть использовано в

5 различных схемах измерения текущего среднего значения параметров.

Известны устройства для преобразования измеряемого параметра .в усред-1 ненный выходной сигнал, содержащие преобразователь, элементы сравнения, счетчики fl).

Эти устройства не обеспечивают эффективного сглаживания при измерении среднего значения измеряемого параметра.

Известно устройство для дискретного экспоненциального сглаживания, содержащее линейный преобразователь аналог-код, соединенный-с коммутатором, и реверсивный счетчик, к инфор- мационнык выходам которого подключены

-входй блока фиксации кодов (2).

Недостаток этого устройства состо25 ит в неравномерной дискретности изменения параметра сглаживания.

Целью изобретения является повы юние точности усреднения измеряемых величин.

Поставленная цель достигается тем, что устройство для дискретного экспоненциального сглаживания, содержащее линейный преобразователь аналог-код, соединенный с коммутатором, и реверсивный счетчик, к информационным выходам которого подключены входы.блока фйксации кодов, дополнительно содержит делитель частоты, включенный между коммутатором и реверсивным счетчиком, и счетчик-регистр, управляющий вход которого соединен с управляющим входом реверсивного счетчика и выходом коммутатора, счетный вход — с импульсным входом коммутатора, информационные входы — c выходами реверсивного счетчика и входами блока фиксации кодов, а выход переполнения - co входом установки коммутатора, причем делитель частоты содержит два управляемых делителя, вы ход первого из которых соединен с единичным входом триггера, а выход второго — с нулевым входом триггера.

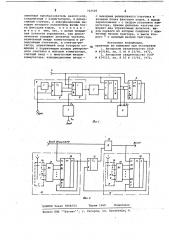

На фиг. 1 представлена функциональная электрическая схема устройства; на фиг. 2 — функциональная электрическая схема делителя частоты.

Устройство для дискретного экспоненциального сглаживания содержит ли702509 нейный преобразователь аналог-код 1 (найрнмер преобразователь аналог-частота), коммутатор 2, к выходу которого подключен делитель частоты 3, соединенный с реверсивным счетчиком 4, к информационным выходам которого подключены блок фиксации кода 5 н счетчик-регистр б. Коммутатор 2 включает последовательно включенные элемент задержки 7, триггер 8 и элемент

2И/ИЛИ 9 ° Один из импульсных входов элемента 2И/ИЛИ 9 соединен со счетным .входом счетчика-регистра б с шйной импульсов, другой — с преобразователем аналог-частота 1. Выход счетчнка- регистра б подключен к нулевому, а через элемент задержки 7 к единичному входу триггера 8, единичный выход которого соединен с управляющими входами счетчика 4, счетчика-регистра б и блока фиксации кодов 5.

Делитель частоты 3 (см. фиг. 2) вы- о полнен на двух управляемых делителях

10 и 11, элементе И 12 и триггере 13.

Каждый управляемый делитель 10 и 11 состоит из переключателя 14, дешифратора 15 и счетчика 16, информаци- 25 онные входы (Д1...ДИ) которого соединены с дешифратором, вход делителя 3 соединен со счетным входом счетчика

16 делителя -10 и через схему И 12 со счетным входом счетчика 16 делите- 30 ля 11. Выходы делителей 10 и 11 соединены соответственно с единичным и нулевым входами триггера 13 и со входами синхронизации счетчиков 16.

В исходном состоянии делитель частоты 3, реверсивный счетчик 4 и счетчик-регистр 6 установлены в нулевое состояние и на вход Сброс подают импульс, который устанавливает в нулевое состояйие триггер 8 и запускает 40 схему задержки 7.

При наличии на входе устройства йзмеряемой" вйй4чййы х„ -, ймйульсы с выхода преобразователя 1 через элемент 2И/ИЛИ 9 поступают на вход делителя частоты 3. Коэффициенты деле- 45 ния В и К управляемых делителей 10 и

11 устанавливают с помощью переключателей 14.

Дешифраторами 15 коэффициенты деления К и В преобразуются в двоичные коды, и в момент появления импульсов переполнения на выходах управляемых делителей коды переписываются в счетчики, определяя коэффициенты деления. 55

При поступлении на вход первого управляемого делителя 10 импульсов с выхода комчутатора 2 на выходе делителя получают импульс, который устанавливает триггер 13 в единичное co« «)gp стояние.

Потенциал с выхода триггера 13 от-, крывает схему И 12 и входные ймпульсы поступают на делитель 11, с выхода которого каждый К-й импульс поступает на триггер 13 и устанавливает его в нулевое состояние. Такое вцполнение делителя позволяет реализовать любой дробно-рациональный коэффициент деления делителя 3 равный при

К «а Я вЂ” 1.

К

Импульсы с выхода делителя 3 поступают в течение времени Т (Т вЂ” параметр схемы задержки 7) на счетчик 4, установленный первоначально потенциалом с выхода триггера 8 по управляющему входу на сложение. Счетчик просчитывает импульсы, соответствующие частоте —, где f средняя частота следования входных импульсов с преобразователя 1; P — коэффициент деления делителя 3.

Через время Т после подачи импульса на вход Сброс с выхода схемы задержки 7 на вход триггера 8 поступает первый тактовый импульс, который устанавливает триггер в состояние 1 переписывает накопленный к этому моменту в реверсивном счетчике 4 код у = — T в блок фиксации кода 5 и

F< счетчик-регистр б и включает реверсивный счетчик 4 по управляющему входу V на вычитание.

da вход делителя частоты 3 через; элемент 2И/ИЛИ 9 начинают поступать,: импульсы,с шины счетных импульсов и реверсивйый счетчик 4 просчитывает.

Е частоту .—, где F - частота счетных импуль с ов . р

Одновременно счетчик-регистр, работающий на вычитание, начинает просчитывать частоту F и через время — на выходе переполнения счетй

F чика-регистра 6 появляется импульс, который устанавливает триггер 8 в состояниеие 0, переключает реверс ивный счетчик 4 на сложение и запускает схему задержки 7.

За время t реверсивный счетчик 4 пуосчитывает число импульсов, равное и в момент установки трлггера 8 в состояние 0 в счетчике 4 будет записан код

1 р

К приходу п-го тактового импульса с выхода схемы задержки 7 в счетчике

4 будет записан код

Vn= (-А)Чи, + а Хи, где с(= р — любое дробно-рациональное число в диапазоне от 0 до 1.

Таким образсм в устройстве для дискретного экспоненциального сглаживания устраняется систематическая погрешность, а параметр сглаживания может изменяться от 0 до 1 и тем самйм" повышается точность усреднения измеряемых величин. формула изобретения

Устройство для дискретного экспоненциального сглаживания, содержащее

702509!

4Ри». 2

Тираж 1060 Подписное

ЦНИИПИ Заказ 7608/53

Филиал ППП Патент, r. Ужгород, ул. Проектная» 4 линейный преобразователь аналог-код, соединенный с коммутатором, и реверсивный счетчик, к информационным выходам которого подключены входы блока фиксации кодов, о т л и ч а ю1 щ е е с я тем, что, с целью повышения точности усреднения, оно дополнительно содержит делитель частоты, включенный между коьмутатором и реверсивным счетчиком, и счетчик-регистр, управляюший вход которого соединен с управляющим входом реверсивного счетчика и выходом коммутатора, счетный вход — с импульсным входом коммутатора, информационные входы— с выходами реиерсивного Счетчика и входами блока фиксации кодов, а выход переполнения — c входом установки коммутатора, причем делитель частоты со" держит два управляемых делителя, выход первого из которых соединен с еди- ничным входом триггера, а выход второго — с нулевым входом триггера.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 409146, кл. G 01 R 23/00, 1972.

2. Авторское свидетельство СССР

Р 424313, кл. И 03 К 13/02, 1972.