Устройство для сопряжения вычислительной машины с каналами связи

Иллюстрации

Показать всеРеферат

ОП ИС

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик

»ц»703799

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) ЗаЯвлено 01.03.77 (21) 2470713/18 24 (53)M. Кл. с присоединением заявки МО 06 Р 3/04

Веудерстееемй кемнтет

СССР ае лаием взееретенкйй и еткрытей (23 ) ПриоритетОпубликовано 1 .12.79. Бюллетень %46

Дата опубликования описания17.12.79 (53) УДК 681 328 (088,8) М. М. Осипенко, А. С. Колокольчиков н В. М, Бродский (72) Авторы изобретения (7! ) Заявитель (54) УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ

МАШИНЫ С КАНАЛАМИ СВЯЗИ

Изобретение относится к области вычислительной техники, в частности..к уст. ройствам для сопряжения UBM с абонентамн» и может быть использовано В c8 стемах дистанционной обработки, данных.

Известно устройство для сопряжения

UBM с каналами связи, содержащее ком мутатор, преобразователь кода, буфер, распределитель импульсов, блок управления, формирователь, узел поиска левой едннн10 пы, элемент И, два триггера, группы элементов И н регистры управления (1).

Недостатком устройства является малая надежность.

Известно также устройство для сопряжения I1BN с каналами связи,.содержащее блок согласования, генератор импульсов, блок кодопреобразования, блок формирования коррекционных посылок, блок анализа коррекцнонных посылок, при емно-передаю щий блок, блок связи с телеграфной линией связи, регистр режима, шифратор символов, схему анализа служебных комбинаций символов, схему возвратя к основно2 му циклу, схему обмена автоответамв и схему дешифрации символов (2)„

Недостаток устройства состоит в том, что оно требует значительных затрат оборудования.

Наиболее близким к, изобретению по технической сущности н достигаемому результату является устройство для сопряжения вычислительной машины с каналами связи, содержащее коммутатор, первый вход которого является первым входом устройства, блок управления, первый выход которого соединен со вторым входом коммутатора, преобразователь кода, регистр адреса, реестр конца обмена, счетчик, триггер н первый элемент ИЛИ (3).

Недостаток устройства состоит в том, чч:о оно имеет малую надежность, так как не позволяет проводить повторную передачу информации при неустойчивой илн неисправной работе оконечных устройся свя-: зи, а также не формирует запроса для по вторной передачи информации при обнаружении сбоя. Кроме того, устройство не

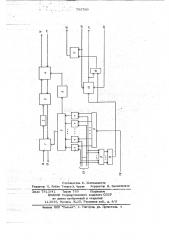

З - 703 7,3 3 позволяет вести передачу информации в ка- гистр 8 конца обмена, регистр 9 адрес„ налы связи и прием информации из 1IBM, счетчик 10, триггер 11, элементы ИЛИ что обуславливает его ограниченные функ- 12 и 13, первый вход 14, второй. выход циональные возможносги. 15, первый выход 16, второй вход 17, Целью изобретения является расшире- > четвертый выход 18, третий вход 19, чет ние функциональных возможностей за счет вертый вход 20, третий выход 21, пятый обеспечения повторного обмена выдачи ин- вход 22 и группу входов 23. формации в каналы связи и приема инфор Устройство работает следующим обрамации из вычислительной машины. зом.

Поставленная цель достигается тем, з B исходном состоянии н а выходе 18 что устройство содержит блок буферной наличие высокого потенциала соответству памяти; распределитель импульсов, блок ет сигналу «готовносгь устройства подство, контроля, второй элемент ИЛИ и группу ключенного ко входу ЦВМ. По этому сиг элементов И, причем первый выход ком- налу из ЦВМ на вход 20 и далее в ре мутатора через блок контроля соединен 15 гистр 9 поступает позиционный код номес первым входом преобразователя кода, ра канала связи, а.в блок 4 по входу 17 второй вход, первый и второй выходы кото- поступает информация, которую необходимо рого соединены соответственно с первым передать из UBM в канал связи. По сигвыходом блока буферной памяти, с пер- налу на входе 19 гасится триггер 11 и вым входом блока буферной памяти и с 20 запускается счетчик 10 для отсчета вре третьим входом коммутатора, вторые вход мени ожидания конца обмена. й" выход блока буферной памяти и второй

ppà те на входе соответствувыход коммутатора являются соответст- готовности к работе на вход оо = Ие%й вторым" входом устройства и йер- ющего элемента И 7 присутствует высовым, вторым выходами устройства, второй 2 кий потенциал. При совпадении этого повыход блока управления через распредели- тенциала с "1" в соответствующем раз тель-импульсов соедйнен с третьим вхо- ряде регистра 9 на один из входов блока дом блока буферной памяти, разрядные вы- 5 управления выдается сигнал, который ходы регйстра адреса соединены с первы- через коммутатор 1 подключает информами входами соответствующих элементов З ционные входы одного из абонентов. С по

И группы элементов И, вторые входы эле- мощью раслрэделителя 6 импульсов счиментов И соединены с соответствующими тывается информации из блока 4. входами группы входов устройства, груп- На время обмена в режиме передача па входов устройства через регистр кон- с соответствующего абонента снимается ца обмена соединена с первым элементом высокий потенциал, который восстанавлиИЛИ, выход которого соединен с первым вается только после конца обмена. Призуправляющим входом второго-элемента нак конца обмена, появившийся на входе

ИЛИ, третий вход устройства соедйнен с соОтветствующего разряда регистра 8 чеодним входом триггера и со вторым управ- .реэ элемент ИЛИ 12 сбрасывает счетчик ляющим входом счетчика„выход которого 10 и через элемент ИЛИ 13 устанавлисоединен с третьим выходом устройства вает" триггер 11 в состояние готовности, и со вторым входом второго элемента При котором, устройство. готово к очередИЛИ, выход которого соединен с другим ному циклу обмена.

- входом триггера, выходы элементов И гРУппы элементов И соединены со входа- . При неисправ

45 неисправности абонента на входе со ми блока управления, а вход регистра ад- ответствуц>щего И7 о ответствующего элементаИ7не будет высореса„ счетный вход счетчика и выход триг- кого потенциала или же на выходе соотгера являются соответственно четвертым„ветствующего разряда регистра 8 не понятым входами и пятым выходом устрой-",Йй тся признак конца обмена. Тогда счетства. чик 10 сформирует сигнал переполнения

Структурная схема устройства приведе (заполнение счетчика 10 происходит имна на чертеже. пульсами, поступающими на вход 22), ко

Устройство для "сопряженйй "вйчисли- торый через элемент ИЛИ 13 переклютельной машины с каналами связи содер- чит триггер 11 и поступит на выход 21. жит коммутатор 1, блок 2, контроля, пре- Появление сигналов на выходах 18 и 21 образователь 3 кода, блок 4 буферной па- информирует UBM об ошибочной передаче мяти, блок 5 управления, распределитель данных. По сигналам от ЦВМ организует6 импульсов, группу элементов И 7, ре- ся повторная передача информаций в этот

7037

5 же канал, связи (при сбое) или в дру1-ой канал (неисправен канал).

Ч ак К8К абоненты обычно имеют возможность определять наличие сбоев в принимаемой информации, для целей обнаружения ошибок в информации, поступающей от абонентов, в устройство введен блок

2 контроля, который при наличии сбоя сообшает об этом ЦВМ через преобразователь 3 кода и блок 4. о

При наличии сбоя UBM через тракт передачи посылает запрос абоненту на повторную передачу той информации, в кото рой был обнаружен сбой блоком 2.

Таким образом, за счет введения в со- 5 став устройства новых узлов и связей удалось достигнуть расширения его функциональных возможностей.

Формула изобретения

Устройство для сопряжения вычислительной машины с каналами связи, содер25 жащее коммутатор, первый вход которого является первым входом устройства, блок управления, первый выход которого соединен со вторым входом коммутатора, преобразователь кода, регистр адреса, регистр .зо конца обмена, счетчик, триггер, первый элемент ИЛИ, о т л и ч а ю щ е е с я

1 тем, что, с целью расширения функциональных возможностей за счет обеспечения повторного обмена выдачи информации

35 в каналы связи и приема информации из вычислительной машины, оно содержит блок буферной памяти, распределитель импульсов, блок контроля, второй элемент

ИЛИ и группу элементов И, причем первый выход коммутатора через блок контроля соедйнен с первым входом преобразователя кода, второй вход, первый и вто рой выходы которого соединены соответст9с)

6 венно с первым выходом блока буферной памяти, с первым входом блока буферной памяти и с третьим входом коммутатора, вторые вход и выход блока буферной памяти и второй выход коммутатора являются соответственно вторым входом устройства и первым, вторым выходами устройства, второй выход блока управления через распределитель импульсов соединен с третьим входом блока буферной памяти, разрядные выходы регистра адреса соединены с первыми входами соответствующих элементов И группы элементов И, вторые входы элементов И соединены с соответствующими входами группы входов устройства, группа входов устройства через регистр конца обмена соединена с первым элементом ИЛИ, выход которого соединен с первым управляющим входом второго элемента ИЛИ, третий вход устройства соединен с одним входом триггера и со вторым управляющим входом счетчика, выход которого соедийен с третьим выходом устройства и со вторым входом второго элемента ИЛИ, выход которого соединен с другим входом триггера выходы элементов И группы элементов И соединены со входами блока управления, а вход регистра адреса, счетный вход счетчика и выход триггера являются соответственно четвертым, пятым входами и пятым выходом устройства.

И сточники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

М 516031, кл. 5 06 F 3/00, 1976.

2. Авторское свидетельство СССР

М 433480, кл. 6- 06 Р 9/00, 3/04, 1974, 3. Авторское свидетельство СССР

М 433482, кл. (3 06 F 9/18, 3/04, 1974 (прототип).

703790

Составитель Ф, Шагиахметов

Редактор H. Лобач Техредэ. уазик Корректор,й. Веселовскан

Заказ 7813/41 Тираж 780 . Подписное

ИНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушскаа наб., д. 4/5 филиал ППП «Патент, r. Ужгород, ул. Проектнан, 4