Накапливающий сумматор

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

038! 0

4r

J (6I) Дополнительное к авт. ! (22)Заявлено 11 04.77 (2, Кл.

06 Р 7/50 с присоединейием заявки

Гооудерстееииый комитет

СССР ио делам изобретений и открытий

{23) Приоритет

Опубликовано 15.12.

ДK 681.325. (088. 8) Дата опубликования (72) Авторы изобретения

Г. Д. Дорощенков, В. Е. Качуровский и А. В. Чередниченко (7I) Заявитель (54) НАКАПЛИВАЮЩИЙ СУММАТОР

Изобретение относится к области дифровой вычислительной техники.

Известны накапливающие сумматоры, содержащие в каждом разряде счетный триггер, элемент задержки, элементы И и ИЛИ (1) (21.

Наиболее близким к данному изобре- тению является накапливающий сумматор содержащий в каждом разряде счетный триггер, счетный вход которого соединен

10 с выходом первого элемента ИЛИ, а выход подключен к выходу переноса в последующий разряд (31 .

Слагаемые числа должны подаваться на параллельные входы разрядов сумма 15 тора последовательно во времени, обеспечивая временной интервал между поступлением двух чисел, достаточный для формирования сигнала переноса в разрядах сумматора, и его передачу через линии задержки включенные между каждыми двумя соседними разрядами по направ.лению от младших разрядов к старшйм, что существенно снижает быстродействие

2 сумматора. Кроме того, в таком сумматоре отсутствует возможность сложения чисел, представленных в последователт ном коде, а также в случае, когда одно из слагаемых представлено в последовательном, а другое.в параллельном коде.

Целью изобретения является расширение класса решаемых задач и увеличение быстродействия сумматора.

Это достигается тем, что предлагаемый сумматор содержит в каждом раз-. ряде элемент И, элемент И-НЕ, второй и третий элементы ИЛИ, и, кроме того, в сумматор введен распределитель импульсов, вход которого подключен к управляющему входу сумматора, а выходы ооединены с первыми входами элементов И-НЕ и И в каткдом раэтяде, вторые входы которых соединены с выходами второго и третьего элементов ИЛИ, а выходы соединены с первым и вторым входами первого элемента ИЛИ, третий вход которого соединен с выходом переноса из предыдущего

703 8

"разряда сумматора; первые входы второго и третьего элементов ИЛИ каждого разряда сумматора соединены с шинами па раппепьного ввода соответствующих разрядов первого и второт о слагаемых, вторые, входы второго и третьего элементов ИЛИ

1 каждого разряда соединены с шинами по-:

I спедоватепьного ввода первого и второго слагаемых

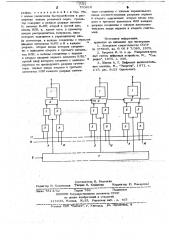

На чертеже представпена блок-схема 10 сумма тора;

Сумматор содержит счетные триггеры

1 со счетными входами, элементы И-HE, .

2, эпементы И 3, элементы ИЛИ 4,5, 6 распределитель импульсов 7, управпяющий вход 8, шины параппепьного ввода первого и второго слагаемых 9 и 10, шины поспедоватепьного ввода первого и второго слагаемых 1 1 и 12.

Первый импульс с распредепитепя импульсов 7 поступает на входы эпементов

И-Н Е 2 и И 3 первого разряда, а i -ый импульс с распределителя импульсов 7 поступает на входы элементов И-HE 2 и 2s

И 3 -го разряда.

Слагаемые числа, представпенные в параллельном коде, одновременно подаются на шины параппепьного ввода "спагаемых 9 и 10 всех разрядов сумматора, 30 после чего на управпяющий вход 8 посту пает сигнад запуска. Разряды слагаемых. через элементы ИЛИ 5 и 4 поступают на входы эпементов И-НЕ 2 и элементов И

3, на другие входы которых подаются 35 сдвинутые во времени стробирутощие импульсы распределитепя импульсов 7, причем дпитепьность стробимпупьсов больше времени перекпючения триггера 1.

В случае, когда значение разряда спа- о гаемого, поступающего на вход элемента

И-НЕ 2, соответствует ".1, передним рронтом стробирующего импульсе на выходе эпемента И-НЕ 2 формируется rie репад напряжения, поступающий на счет- 45 ный вход триггера 1, устанавпивая его в

/. состояние "1 .

Аналогично происходит формирование перепада напряжения на выходе элемента

И 3, при этом перепад формируется задним фронтом стробирующего импупьса.

Таким образом, при значениях (1-1)го разряда спагаемых, соответствующих логической единице, на счетный вход () -1)-го триггера 1 поатупают два сиг-,5> напа запуска, временнбй интервал меж"ду которыми определяется дпитепьностью

L стробирующего импупьса. При этом (-1) счетный триггер 1 последовательно прини10, 4 мает состояние "1" и "О, в результате чего на выходе (j--1 )-го счетного триггера формируется сигнал переноса, поступающий через элемент ИЛИ 4 на счетный вход т-1о триггера 1. Через промежуток времени, равный временному интервалу между импульсами распредепитепя импупьсов 7, начинается формирование сигналов запуска 1 -го триггера 1 на

1 выходах элементов И-HE 2 и И 3. Процесс формирования сигнапов запуска

1-го тригт ера 1 анапагичен описанным.

При суммировании слагаемых, предста- вленных в поспедоватепьном коде, а также .в случае, когда одно из спагаемых представпено в поспедоватепьном, а другое в паралпепьном коде, сигнал запуска поступает на вход 8 синхронно с начапом первой кодовой посылки слагаемого, представпейного в последовательном коде.

Длитепьность импульса распределителя импульсов 7 и временных интервалов между ними выбирается таким образом, чтобы первый импульс распределителя импульсов 7 совпадал по времени с первой кодовой посылкой последовательного кода слагаемого, второй — со второй кодовой посылкой и т.д.

Формирование сигналов запуска счетных триггеров 1 при этом происходит аналогично описанному ранее.

Сумма считывается с выходов счетных триггеров 1.

Испопьзование в сумматоре распредепителя импульсов, осуществляющего стробирование кодовых сигналов слагаемых и одновременно создающего временной ин тервап междупоступлением сигнала переноса и записью разрядов слагаемых в триггере соответствующих разрядов, выгодно отличает данный сумматор от прототипа, т.е, появляется возможность спожвния чисел, представленных как в паралпепьном, так и в последовательном коде без предварительного преобразования.

Кроме того, в данном сумматоре слагаемые подаются на входы сумматора одновременно, что позволяет увепичить быстродействие сумматора.

Формула изобретения

Накапливающий, сумматор, содержащий в каждом разряде счетный, триггер, счетный вход которого соединен с выходом первого эпемента ИЛИ, а выход подт пючен к выходу переноса в последующий

703810

11

Составитель В. Березкин

Редактор Н. Каменская Техред Н. Ковалева Корректор Ю. Макаренко

Заказ 781 4/42 Тираж 780 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж 35, Раушская наб., д, 4/5

Филиал ППП "Патент, г, Ужгород,,уп, Проектная, 4 разряд, о т п и ч а ю ш и и с я тем, -что, с целью увеличения быстродействия и расширения класса решаемых задач, сумметор содержит в каждом разряде элемент

И, эпемент И-НЕ, второй и третий элементы ИЛИ, и, кроме того, в сумматор введен распредепитель импульсов, вход которого подключен к управляющему вхо,бу сумматора, а выходы соединены с первыми входами элементов И-НЕ и И в каждом разряде, вторые входы которых соединены с выходами второго и третьего эпемен- тов ИЛИ, а выходы соединены с первым и вторым входами первого элемента ИЛИ, третий вхоп которого, соединен с выходом переноса из предыдущего разряда сумматора, первые входы второго и третьего элементов ИЛИ каждого разряда сумматора соединены с шинами параллельного ввода соответствующих разрядов первого и второго слагаемых, вторые входы второго и третьего эпементов ИЛИ каждого разряда соединены с шинами последова- . тельного ввода первого и второго слагаемых.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетепьство СССР

¹ 375645, кп. 6 06 Р 7/385, 1970.

2. Букреев И. Н. и др. Макроэпектрон-, ные схемы цифровых устройств, М., "Сов. радио, 1975, с. 330, 3, Шигин А. Г. цифровые нычиспитепьные машины, М., Энергия, 1971, с.

2 15, рис. 9-23 (прототип).