Контролируемый параллельный сумматор

Иллюстрации

Показать всеРеферат

(72) Авторы изобретения

Б.Г. Лысиков и A.A. Ыостак (71) Заявитель

Минский радиотехнический институт (5 4 ) КОНТРОЛИРУЕМЫЙ ПАРАЛЛЕЛЬНЫЙ СУММАТОР

Изобретение относится к области вычислительной техники и может быть применено при разработке арифметических устройств, контроль которых организован по четности, а в исполь-. зуемых сумматорах разрядные переносы формируются параллельным, параллельно-последовательным или параллельнопараллельным способом.

Известны сумматоры, .содержащие в каждом разряде элемент И или элемент ИЛИ, блок формирования параллельного переноса и блок формирования поразрядной суммы (1).

Разрядные суммы при этом формируются в соответствии с выражением

= a„gb„QCnгде а, Ь - разрядные слагаемые;

С, — перенос из предыдущего (n-l)-го разряда сумматора.

Недостатком известных сумматоров. является низкий процент обнаруживаемых ошибок, вызываемых одиночной 25 неисправностью сумматоров, при органиэации их контроля по четности, при этом ошибки, вызываемые неисправностью элементов И. или ИЛИ, а также неисправностью блоков формирования параллельных переносов, не обнаружи:ваются контролем по четности.

Наиболее близким по технической сущности к предложенному является контролируемый параллельный сумматор, содержащий в каждом разряде элемент И и элемент ИЛИ, блок формирования параллельного переноса и во всех разрядах, кроме старшего, блок формирования поразрядной суммы, причем первый, второй и третий входы блока формирования поразрядной суммы каждого разряда, кроме младшего, соединены соответственно с выходом элемента И, элемента ИЛИ своего разряда, блока формирования параллельного переноса предыдущего разряда, первый, второй и третий входы блока форйирования поразрядной суммы младшего разряда соединены соответственно с выходом элемента И, элемента ИЛИ своего разряда и со входом сумматора, первый и второй входы блока формирования параллельного переноса соединены соответственно с выходом элемента И и элемента ИЛИ данного разряда, выход блока формирования параллельного переноса старшего разряда является выходом сумматора (2).

703817

При формировании разряднйх сумм . в данном сумматоре используется выражение

8„= Й„ т„ „-, где Я„=й„Ь„и Т„=а„; „

- соответственно функции генерации и тран-. пере носа n-ro разряда.

Это позволяет наряду с контролем блоков формирования поразрядных сумм .организовать контроль элементов И или ИЛИ, формирующих функции генерации и транзита переноса в каждом разряде сумматора.

Недостатком известногО сумматора является относительно низкая эффективность контроля по четности, так как цолностью не охвачены контролеМ блоки формирования параллельных переносов, составляющие основной объем оборудования сумматора.

Целью изобретения является повышение эффективности контроля параллельного сумматора.

Поставленная цель достигается тем, что в старший разряд сумматора введен, блок формнрования поразрядной ЗО суммы с функциональной зависимостью от переноса, причем выход элемента

ИЛИ C éðøåãî разряда соединен соответственно с первым входом блока формирования поразрядной суммы с . 35 функциональной зависимостью от переноса, второй и третий входы котброго соединены соответственно с выходами блока формирования параллельного перайоса данногб и предыдущего разря- 4О дов.

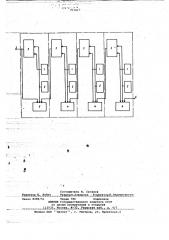

На чертеже приведена структурная схема и-разрядного"контролируемого параллельного сумматора для n=4.

Сумматор содержит в кайдом разряде, 5 элемент И 1, элемент ЙЛИ.2, блок 3 формированйя параллельного переноса и во всех разрядах, кроме старшего, блок 4 формирования поразрядной суммы, блок 5 формирования пораэряднойсуммы с функциональной зависимостью ов переноса B старшем разряде сумматора, причем первый второй и тре"тий входы блока 4 формирования по- .разрядной суммы каждого разряда, кроме младшего, соединены соответст.венно, c выходами элемента И 1, элемента ИЛИ 2 своего разряда, блока 3 формирования параллельного переноса предыдущего разряда. Первый, второй и третий входы блока 4 форми- 60 рования поразрядной суммы младшего разряда соединены соответственно с выходами элемента И 1, элемента ИЛИ

2 своего разряда и с входом б сумматора, на который поступает входной 6. перенос сумматора. Первый и второй входы блока 3 формирования параллельного переноса соединены соответственно с выходами элемента И 1 и элемента ИЛИ 2 своегоразряда.Выход элемента ИЛИ 2 старшего разряда соеди- нен соответственно с первым входом блока 5 формирования поразрядной суммы с функциональной зависимостью от перекоса, второй и третий входы которого соединены соответственно с выходами блоков 3 формирования параллельного переноса данного и предыдущего разрядов. Вход б сумматора предназначен для ввода входного переноса, а выход блока 3 формирования параллельного переноса старшего разряда является выходом 7 сумматора, с которого снимается выходной перенос сумматора.

Сумматор работает следующим образом.

Элементы И 1 и ИЛИ 2 формируют функции Qs - ©sg генерации, Т - Тж транзита и переноса в соответствующих разрядах сумматора. С помощью блоков 3 формируются параллельным способом разрядные переносы С, С, С > и С 4 определяемые следующим образом (возрастание индексов при буквенных обозначениях принято в.направлении старших разрядов):

C„=C„+T С „; с - +т +т т с где Сзу, — входной перенос, поступающий на вход б сумматора;

C р — выходной перенос, снимаемый с выхода 7 сумматора;

С„, С, С> и С - переносы соответственно иэ

1-го — 4- го разрядов сумматора.

Блок 4 формирования поразрядной суммы функционирует в соответствии с тем же выражением,что и известный сумматор (2). Блок 5 формирования поразрядной суьмы. с.функциональной зависимостью от,переноса может быть построен в соответствии с выражением 2

S у МС. а Ь С,+T СУа

-" „ь с ° <т +с ) vc Неисправность одного из блоков

4 чли 5 может вызвать только одиноч70381 7 ную ошибку в соответствующем разряде суммы, которая всегда будет обнаружена контролем по четности. Неисправность же одного из элементов И 1 илн ИЛИ 2 может прйвести к возникновению групповой ошибки, но она также . 5 всегда будет обнаружена контролем по четности, так как общее число ошибок в разрядах суммы и переноса нечетно. Например, неисправность элемента И 1 в первом разряде сумматора Может вызвать ошибки либо, только в 8 либо в S, S, C< либо в

8, S, 83, С,, С, и т.д. Что же касается блоков 3 формирования параллельных: переносов, то в сумматоре контролем охвачен наиболе сложный блок, формирующий параллельный перенос из старшего разряда, что и позволяет повысить эффективность контроля сумматора. Действительно, пусть ошибка в формирований перено- . са С вызвана неисправностью блока

3 формирования параллельного перено- са старшего разряда. Но тогда эта ошибка всегда вызовет ошибку в формировании разрядной суммы Я4 которая и будет обнаружена Контролем, так как значение переноса С4. не используется при предсказании четности ре-" зультата.

Контроль остальных блоков 3 формирования параллельных переносов может быть организован любым из известных методов с привлечением дополнительного контрольного оборудова- ., ния. 35

Наибольший эффект от применения " данного сумматора получается в том случае, когда рассмотренный п-раз-.. рядный сумматор служит составной частью быстродействующего m-разряд- 4О .ного сумматора, в котором переносы между группами (n-разрядными сумматорами) формируются параллельным способом, причем когда п = п,щь „ = 2, а Bl)pD ° 8 этом случае контролем по четности без Введения дополнительного оборудования будут охвачены не только блоки формирования параллельных переносов старших разрядов иразрядных сумматоров, но и блоки формирования параллельных переносов между r1-разрядными сумматорами,т .е. практически основная часть обору дования m-разрядного сумматора.

Таким образом, введение в.старший разряд контролируемого параллельного суМматора блока формирования поразрядной суммы с функциональной зависимостью or переноса позволяет повысить эффективность контроля сумматоров по четности.

Формула изобретения

Контролируемый параллельный сумматор, содержащий в каждом разряде элемент И и элемент ИЗТИ, блок формирования параллельного переноса и во всех разрядах кроме старшего, блок формирования поразрядной суммы,.причем первый, второй и третий входы блока формирования поразрядной суммы каждого разряда, кроме младшего, соединены соответственно с выходом элемента И, элемента ИЛИ своего разряда, блока формирования параллельного переноса предыдущего разряда, первый, второй и третий входы блока

:формирования поразрядной суммы младше:го разряда соединенй соответственно с выходом элемента И, элемента ИЛИ своего разряда и со входом сумматора, первый и второй входы блока формирования параллельного переноса соединены соответственно с выходом элемента И и элемента ИЛИ данного разряда, выход блока формирования параллельного переноса старшего разряда является выходом сумматора, отличающий с я . тем что, с целью повышения эффективности контроля, в старший разряд сумматора введен блок формирования поразрядной суммы с Функциональной зависимостью от переноса, причем выход элемента

ИЛИ старшего разряда соединен соответственно с первым входом блока формирования поразрядной суммы с функциональной зависимостью от переноса, второй и третий входы которого соединены соответственно с выходами блоков формирования параллельного переноса данного и предыдущего разрядов., Источники информации, .- принятые во внимание при экспертизе

1. Селлерс Ф. Методы обнаружения ошибок в работе ЭЦВМ, N., Мир, 1972, с. 108.

2. Селлерс Ф. Методы обнаружения ошибок в работе ЭЦВМ, М, Мир, 1972, с. 119,120 (прототип) .

Редактор Н. Лобач

Эаказ 8289/51

Составитель И. Сигалов

Техоед Л,Ag@epasa Корректор Н. Задерновская

Тираж 780 Подписное

ЦНИИПИ Государственного комитета СССР по делам иэобретений и открытий

113035 Иосква Ж-35 Рараская наб. д. 4/5

Филиал ППП Патент, и. Ужгород, ул. Проектная,4