Преобразователь угла поворота вала в код

Иллюстрации

Показать всеРеферат

— уф

О h И:-C А Н

Союз Советских

Социалистииеских

Республик ()703853

К АВТОе" СКОМУ СееИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 17.01.77 (21) 2444474/18-24 с присоединением заявки № (23) Приоритет— (5) ) „1 Кп2

G 08 С 9/00

Государственна!й номнтет

СССР по делам нзооретеннй н открытнй

Опубликовано 15.12.79. Бюллетень №46

Дата опубликования описания 25.12.79 (53) УДК 681.325 (088.8) (72) Автор и юбретения

A. К. Смирнов (71) 3,!я витс ль (54) ПРЕОБРАЗОВАТЕЛЬ УГЛА ПОВОРОТА

БАЛА В КОД

1)зобреге>1 и (>тш>сится к области автом(1 111.!! и и>числит", Il)IIoH техники, в частlIo(.ти к преобраз()вателям аналогoBosI величины в ho;(. и м(>ж T быть использовано.

ДЗЯ (ВЯЗ11 <)Н;1,1()ГОВ!>1Х >!СТОЧН!!КОВ ИифОРМации с цифровым вычислительным устройством.

Известны преобразователи у! !а поворота вала в код, содержащие датчик угла, подключенный к блоку формирования кода, в которых, итч ик l г, ьз работает в режиме пут!ьсирукпцего поля. Выход датчика учгла подключен к блоку формирования кода, содержащему несколько каскадно включенных ступеней, предназначенных для последовательного уменьшения зоны вычисляемого угла поворота. В каждой ступени используются элементы для вычитания из угла фиксированных опорных углов решением тригонометрических тождеств (1) .

Недостатком таких преобразователей является сложность и невысокая разрешаю-! цая способность.

Известны также преобразователи угла

1IoI>opoT

Недостатком этих 1>реобразователсй является отсутствие сигнализации об Ilзмс((снии кода llpll измс H(Hèè углового положения.

Изм(ре(ше каждого последх юшего значения угла производится независимо от пр(>д!>дхщи i. Перед каждым последующим измерс1(> нием код предыдущего измерения стирается.

Наиболее близким техническим реlll(íè(÷ к данному изобретеник> является преобразователь угла поворота вала в код, сo;1(ржа!ций последовательно включенные гснсратор импульсов, делитель частоты, блок гитания, синусно-косинусный датчик угл(1, фазосдвигающу>о цепочку, компаратор и формирователь импульсов приращения фазы, другие входы которого соединены с выходами разрядов делителя частоты, и реверсивный счетчик (3).

Недостатком этого преобразователя является низкая точность, вызванная погрешностями блока питания, сдвига по фазе вы70

3853 входных напряжений синусно-косйнусного датчика угла по сравнению с входными напряжениями, аддитивные погрешности фазосдвигающей цепочки и компаратора.

Целью изобретения является повышение точности преобразователя.

Поставленная цель достигается тем, что в преобразователь угла поворота вала в код введены блок синхронизации и дополнительные последовательно соединенные фазосдвигающая цепочка, компаратор и формирова тель импульсов приращения фазы, другие входы которого подключены к выходам разрядов делителя частоты, а выходы формирователей импульсов приращения фазы через блок синхронизации подключены к входам реверсивного счетчика.

В предложенном преобразователе полностью исключается фазовая нестабильность блока питания и входящих в него фильтров, а также фазовая нестабильность на частоте несущей выходных сигналов синусно-косинусного датчика по отношению к входным сигналам. Погрешности фазосдвигающих цепочек и компараторов значительно уменьшаются и определяются относительным изменением параметров фазосдвигающих цепочек и компараторов.

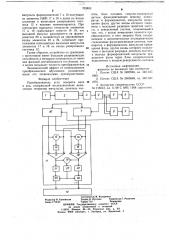

Структурная схема преобразователя пред ставлена на чертеже.

Преобразователь содержит последова-тельно включенные генератор импульсов 1, делитель частоты 2, блок питания 3, синусно-косинусный датчик 4, фазосдвигающую цепочку 5, компаратор 6 и формирователь 7 импульсов приращения фазы, вход которого соединен с выходом разрядов делителя 2 частоты. Выходы синусно-косинусного датчика 4 через последовательно включенные дополнительные фазосдвигающую цепочку 8 и компаратор 9 подключены к дополнитель-. ному формирователю 10 импульсов приращения фазы, другие входы которого соединены с выходами разрядов делителя 2 частоты. Выходы формирователей 7 и 10 через блок 11 синхронизации подключены к реверсивному счетчику 12.

Блок 11 синхронизации предназначен для разделения импульсов, поступающих одновременно на входы сложения (или вычитания) реверсивного счстчика и для вза<м< ого исключения импульс<>в, по<тупающих одновремсн«о иа разные входы реверсивного счетч и ка. Блок 1! синхронизации состоит из элементов И !3 и 14. элементов 15 и 16 задержки, элементов ИЛИ 17 и 18, элемента И 19, формирователя 20, элементов 21 и 22 задержки и элементов 23 и 24 запрета. !

1реобразователь работает следующим образом

Генератор 1 импульсов формирует непрерывную последовательность импульсов, поступающих через делитель 2 частоты в

Для исключения погрешности при совпадении входных импульсов элементов 17 и 18 введены элементы И 13 и 14 и элементы 15 и 16 задержки. Два совпадающих входных импульса элемент ИЛИ, например; элемент

17, воспринимает как один импульс, при этом срабатывает соответствующий элемент

И 13 и через элемент 15 задержки выходной импульс элемента И 13 поступает на третий вход элемента ИЛИ 17.

В результате предложенное устройство имеет вдвое большую разрешающую способ-ность по сравнению с прототипом.

При смещении выходных импульсов компаратора 6 и 9 в одном и том же направлении, что может быть вызвано фазовой -. нестабильностью блока 3 питания, синусно.. косинусного датчика 4, фазосдвигающих цепочек 5, 8 и компараторов 6, 9, выходные

2S

44 блок 3 пиТания, где вырабатывается синусоидальный сигнал для питания синуснокосинусного датчика 4. Модулированные по амплитуде в функции угла поворота выходные сигналы синусно-косинусного датчика 4 поступают на фазосдвигающие це почки 5 и 8, где вырабатываются постоянные по амплитуде синусоидальные сигналы, которые сдвигаются по фазе в разные стороны от начального положения пропорционально углу поворота датчика 4. В компараторах 6 и 9 вырабатываются импульсы ,"в моменты. перехода синусоидальных сигналов через нуль при положительном градиенте

При неизменном угле поворота датчика 4 ход делителя 2 частоты в моменты формирования импульсов компаратором 6 (или 9) будет также неизменен. При изменении угла поворота датчика 4 код делителя 2 частоты в моменты формирования импульсов одним из компараторов, например компаратором 6, будет увеличиваться, а в моменты формирования импульсом другим компаратором 9будет уменьшаться.

К формирователям 7 и 10 импульсов приращения фазы подключены младшие разряды делителя 2 частоты. При изменении угла поворота выходные импульсы компараторов 6 и 9 перемещаются в разные стороны относительно кода младших разрядов делителя 2 частоты. В формирователях 7 и 10 вырабатываются импульсы приращения сдвига фазы. При положительном изменении угла поворота выходные импульсы формирователей 7 и 10 поступают на входы элемента ИЛИ 17. На входе элемента ИЛИ 18 импульсы отсутствуют. Выходные импульсы элемента 17 через последовательно включенные элемент 21 задержки и элемент 23 запрета поступают на вход сложения реверсивного счетчика !2, а выходные импульсы элемента 18 через последовательно включенные элемент 22 задержки и элемент 24 запрета поступают на вход вычитания реверсивного счетчика 12.

703853

5 импульсы формирователей 7 и 10 поступают на элементы ИЛИ 17 и 18 и далее на входы сложения и вычитания реверсивного счетчика 12 и взаимно компенсируются. При совпадении выходных импульсов элементов

17 и 18 срабатывает элемент И 19, его выходной импульс расширяется на формирователе 20 и, воздействуя на управляющие входы элементов 23 и 24, запрещает прохождение совпадающих выходных импульсов элементов 17 и 18 на входы реверсивного счетчика 12.

Таким образом, устройство по сравнению с прототипом имеет большую разрешающую способность и меньшую погрешность от влияния фазовой нестабильности его блоков, что в целом повышает точность преобразователя. 45

Экономический эффект от использования преобразователя обусловлен указанными . выше его техническими преимуществами.

Формула изобретения

Преобразователь угла поворота вала зб в код, содержащий последовательно включенные генератор импульсов, делитель частоты, блок питания, синусно-косинусный датчик, фазосдвигающую цепочку, компаратор и формирователь импульсов приращения фазы, другие входы которого соединены с выходами разрядов делителя частоты, и реверсивный счетчик, отличающийся тем, что, с целью повышения точности преобразователя, в него введены блок синхронизации и дополнительные последовательно соединенные фазосдвигающая цепочка, компаратор и формирователь импульсов приращения фазы, другие входы которого подключены к выходам разрядов делителя частоты, а выходы формирователей импульсов приращения фазы через блок синхронизации подключены к входам реверсивного счетчика.

Источники информации, принятые во внимание при экспертизе

1. Патент США № 3480946, кл. 340-347, 1969.

2. Патент США № 3505669, кл. 340-347, 1970.

3. Авторское свидетельство СССР № 218543, кл. G 08 С 9/00, 1968 (прототип).

Составитель И. Назаркина

Редактор Н. Каменская Техред О. Луговая Корректор Г, Решетник

Заказ 7778/44 Тираж 710 Подписное

ЦН И И ПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, )K — 35, Раушская наб,, д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4