Запоминающее устройство

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

<»>703864 (61) Дополнительное к авт. сеид-ву (22) Завалено 140676 (21) 2372595/18- 24 (51)щ. Кл.2 с присоединением Заявки ¹ (23) Приоритет

G 11 С 21/00

Государствеииый монитет

СССР ао делам изобретений и открытий

Опубликовано 15.12.79, Бюллетень К© 46

Дата опубликования описания 15.1279 (53) УДК 681. 327. 66 (088. 8) Л.И.Ильченко и Ю.И.Кузьмин (71) ЗаяВитель (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к измери- тельной технике и может быть исполь. зовано для задержки во времени:случайного сигнала, представленного в виде дискретных цифровых отсчетов.

Для определения расстояний широко применяются приборы, измеряющие функцию взаимной корреляции между двумя случайными проЦессами, Наиболее важным и занимающим, как правило, большую часть такого прибора звеном является устройство, обеспечивающее задержку одного случайного сигнала относительно другого (1), Однако, если при построении полярных коррелометров применение этих устройств давало удовлетворительные результаты, то при построении цифровых коррелометров с их использованием схемам задержки присущи такие недостатки, как низкая надежность и громоздкость.

Наиболее близким техническим решением к предложенному является запоминающее устройство, содержащее блок памяти на элементах задержки, информационный вход которого является входом устройства, первые управляющие входы блока памяти соединены с выходами первого регистра, выход блока памяти является выходом устройства, и генератор тактовой частоты (2) .

К недостаткам известного устройства относятся громоздкость, так как для организации буферной памяти приходится использовать много дополнительных корпусов микросхем, и низкая надежность, обусловленная тем, что через триггеры буферной памяти проходит вся задерживаемая информация.

Цель изобретения — повышение надежности устройства, Поставленная цель достигается тем, что в устройство введены второй регистр и триггер, вход которого соединен с выходом генератора тактовой частоты, выходы триггера подключены ко входам первого и второго регистров и входам запись-считывание блока памяти, выходы второго регистра соединены со вторыми управляющими входами блока памяти.

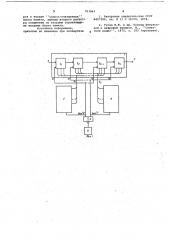

Сущность изобретения поясняется чертежами, где на фиг. 1 изображена схема предложенного устройства, на

703864 фиг. 2 — временные диаграммы его работы.

Запоминающее устройство содержит блок 1 памяти, выполненный на элементах задержки и состоящий из матриц 2 -2, информационный вход которого является входом 3 устройства, первые и вторые управляющие входы

4 и 4g соединены с выходами регистров 5 и 6, а выход является выходом

7 устройства, а также генератор 8 тактовой частоты, соединенный с триг гером 9, выходы которого связаны со входами 10 запись-считывание блока 1 памяти.

Устройство работает следующим об-: разом.

Тактовая частота с генератора 8 поступает на счетный вход триггера

9. С выхода 0 триггера 9 импуль сы пбступают на вход регистра 5 и на входы 10 запись-считывание нечетных матриц блока 1 памяти. С выхода 1 триггера 9 импульсы поступают на вход регистра 6 и на входы

10 запись-считывание четных"матриц блока 1 памяти. Выходы регистров

5 и 6 подключены к соответствующим матрицам блока 1 памяти.

Пусть на вход 3 устройства поступает комбинацйя чисел 1011. Все ячейки матриц блока 1 памяти пред- 30 варительно находятся в нулевой состоянии. В течение интервала времени на входе 10 матрицы 24 действует положительный потенциал (фиг.2,б),. Имеющаяся на входе 3 уст- 35 ройства 1 записывается в ячейку этой матрицы, имеющую адрес 00 (фиг.2,r и д). В течение этого же интервала времени происходит считывание информацйи с ячейки под адре- 4О сом 01 матрицы 2р .(фиг.2, е и ж), запись ее в ячейку 00 матрицы

2 3 и считывание с ячейки 01 матрицы 24. Так как предварительно все ячейки имели нулевое состояние, то по окончании интервала времени они oci àíóòñÿ в прежнем состояний,. кроме ячейки 00 матрицы 2, куда записана 1 .

В момент времени t< меняется сигнал на управляющих входах 4 и 4, блока 1 памяти (фиг.2, r и д), и считывание информации в течение интервала времени t -t Йроисхо)(ит уже с ячейки под адресом 01 (фиг.2,г и д), так как в течение этого интервала времени на входах

10 этих матриц действует нулевой потенциал (фиг.2,б}. В течение этого же интервала времени должна происходить запись считанной информа- 60 ции с ячейки 01 матрицы 2 в ячейку 01 матрицы 22 (фиг.2, е и ж} и с ячейки 01 матрицы 23 в ячейку 01 матрицы 24., так как в течение интервала времени tg -t g 65 на входах 10 матриц 2 и 24. дейст вует положительный потенциал (фиг.2,г).

Аналогично интервалу времени в течение интервалов времени

t3 4 р tg ty Й ty 1 происходит за пись информации соответственно в ячейки 01, 10 и 11 (фиг. 2, r и д) матрицы 24, . В течение интервала tS-tq происходит считывание (фиг.2б) информации с ячейки 00 (фиг.2,г и д) матрицы 2 .

Так как в ней записана 1 в течение интервала времени t< -1, то эта считанная в течение интервала времени tg-tj информация запишется в ячейку 00 матрицы 22 (фиг.2,в), на входе 10 которой в это время присутствует положительный потенциал, Аналогично в течение интервалов времени ttp tg t g t($ и t)y t($ происходит перезались информации иэ ячеек 01, 10 и ll матрицы

2g (фиг.2,г и д) соответственно в ячейки 01, 10 и l l матрицы 2 (фиг.2, е и ж}. В течение интервалов времени 1 -1,, 1((- р

t y-ting и д-122 происходит перезапись информации из ячеек 00, 01, 10 и 11 матрицы 2 соответci"âåHHo в ячейки 00, 01, 10 и 11 матрицы 29, а в течение интервалов времени +2-t g, t 4-tÌ, <26 <р7 и t2$ tä9 — из Ячеек 00, 01, 10 и 11 матрицы 23 в соответствующие ячейки матрицы 24 и т. д. как видно по выходным сигналам матриц 2 -2tj (фиг.2,и-м), устройство осуществляет сдвиг инФормации на фиксированные интервалы времени.

Через каждую ячейку памяти проходит лишь 1/k- ß "часть входной информации, где k - количество ячеек в одной матрице. Если одна ячейка выйдет из строя, то лишь 1/k-я часть информации будет ложной. Следовательно, предложенное устройство обладает повышенной надежностью.

Формула изобретения

Запоминающее устройство, содержащее блок памяти на элементах задержки, информацйонный вход которого является входом устройства, первые управляющие входы блока памяти соединены с выходами первого регистра, выход блока памяти является выходом устройства, и генератор тактовой частоты, о т л и ч а ю щ е е с я тем, что, с целью повышения надежности устройства, в него введены второй регистр и триггер, вход которого соединен с выходом генератора тактовой частоты, выходы триггера подключены ко входам первого и второго регист703864

pos и входам запись-считывание блока памяти, выходы второго регист ра соединены со вторыми управлянщи« ми входами блока памяти, Источники информации, принятые во внимание при экспертизе !

1. Авторское свидетельство СССР

9407396 кл, G 11 С 19/00, 1972.

2. Гусев В.В. и др. Основы импульсной и цифровой техники. M. Советское радио, 1975, с. 383 (прототип).

703864

Составитель А.Воронин

Техред О.Андрейко КорректорТ,Скворцова

Редактор Н.Лобач

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4

Заказ 7816/45 Тираж б 81 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5