Устройство для обмена информацией

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ, Союз Советских

Социалистических

Республик («)705440

1 с

1, oil

/ (61) Дополнительное к авт. саид-ву (22) Заявлено 02.12.77(21) 2550392/18-24 с присоединением заявки М (23) Приоритет (51)м. К .2

G 06 F 3/04

Государственный комитет

СССР но делам . изобретений н открытий (5З) НЖ 681. 327, . 21 (088. 8) Опубликовано 25.1279. Бюллетень Йо 47

Дата опубликования описания 25.1279 (72) Авторы

ИЗОбрЕтЕНИя А. A. Авдюхин, В. Н. Алексеев и В. Г. Колосов (71) Заявитель

Ленинградский ордена Ленина политехнический институт имени М. И. Калинина (54) устРОЙстВО для ОБменА инФОРмАцией

Изобретение относится к области вычислительной техники и может быть использовано при построении специализированных мини-ЦВМ для управления технологическим оборудованием, например, станками с программным управлением.

Известны устройства (1) для обмена данными,содержащие блок выбора приоритета, блок формирования признака обращения, коммутаторы, адресный регистр, дешифратор, регистр обмена и блок управления и осуществляющие обмен информации между периферийными устройствами и па- 15 мятью вычислительной машины.

Недостаток этих устройств состоит в.их сложности.

Наиболее близким к данному устройству по сущности техничекого реше- 20 ния является устройство (2) для обмена информацией, содержащее два блока памяти, регистр адреса, регистр регенерации, группу элементов И,коьму татор ввода, коммутатор вывода, узел согласования с объектом, узел синхронизации, узел усилителей, элементы И и ИЛИ, дешифратор и узел формирования адреса запроса на обмен, причем выход регистра адреса, соединенного входом через первый элемент И с первым выходом узла усили- телей, подключен к адресному входу первого блока памяти, информационные вход и выход которого соединен соответственно с выходом регистра регенерации и информационным входом второго блока памяти, информационный выход которого подключен ко входу узла усилителей, а группы адресных входов записи.и считывания соединены соответственно с первой и второй группой выходов узла формирования адреса запроса, первый, второй и третий выходы узла усилителей подключены соответственно к первому, второму и третьему входам группы элементов И, выход которой соединен с информационным входом регистра регенерации, управляющий вход которого соединен с первым выходом узла синхронизации и входом управления записью второго блока памяти, вход управления считыванием которого подключен ко второму выходу узла синхронизации, выходы и входы узла согласования с объектом подключены сооТветственно ко входам коммутатора

705440 ввода, соединенного выходом с чет вертым входом группы элементов И, и выходам коммутатора нынода, соединенного входам-со вторым .выходом " узла усилителей.

В этом устройстве функции регистров связи выполняют ячейки накопи теля. Обращение к ним производится через узел формирования адреса запроса, называемый блоком выборки, сигналом " c каждого из выходов ко торого возбуждается очередная ячейка иэ группы фиксированных ячеек, второго блока памяти, называемая регистровой частью накопителя. Вы сокая йомехоустайчивость прототипа достигается за счет использования внешнего устройства (ВУ) с дйнами " ческой памятью, информация в которой периодически обновляется пад управлением блока выборки, причем поступает информация непосредственно из ячеек регистровой части накопите ля.

Недостатком указанного устройства является бграниченность возможностей по варьированию количества и составом ВУ; обусловленная жесткостью соединейий выходов блока выборки фиксированных ячеек с элементами комму" "татора ввода"й"вывода, а "также тем", что количество Ву ограничено снерху объемом"регистровой части накопителя.

Последнее обстоятельство, а также то, что блок выборки фиксированных ячеек должен управлять последовательностью опроса этих ячеек, обуславливает глав ный недостаток прототипа - сложность устройства при большом количестве

Ву. Кроме того, в устройстве-прототипе" необходимо иметь в списке команд

ЦВМ специальную команду записи инфбрмации ив фйксированных ячейках: регистровой части накопителя, что:-" также является недостаткам извест---:-: ного устройства.

Целью изобретения является упрощение устройства. Это достигается

Ъ еМ;"-что выходй второй группы"ЙйМадов узла формираваййя адреса запроса-сое ддйнен c:t=îîòâåòñòâóíùèìè вхадайи эле мейта ИЛИ;"соедйненного через второй" элемент И со входом блокировки выхода узла- уСилителей, третий выход кото"""рого через третий элемент И подключен "ко входу дешифратора, соединенного" выходами "с" адреснйми входами соответственно коммутаторов ввода и вывода, первйй и второй йыходы узла . синхронизации йодключены соответствен но ка входу управления записью первого накопителя и упранляющеМу вхбду первого элемента И, третий выход узла синхронизации подключен ко входу управления считынанием первого блока

": паямти, управляющим входом группы элементов И,"управляющими входами втоаого и третьего элементов И.

Такая структура обеспечивает свободную адресацию регистров связи, в. качестве которых исполь зуютс я ячейки накопителя первого блока памяти. .В то же время, каждая ячейка регистровой части используется для хранения очередного адреса из поля адресов, соответствующего ей. Эта дает возможность задавать программно как размеры поля ячеек связи, так и расположение. его в накопителе, а объем регистровой части ограничинает количество полей, что оставляет широкое возможности для варьирования числом

ВУ при постоянном и небальшрм количестве выходов блока обращения к ре-, гистровой части, Поскольку функции регистров обмена выполняют ячейки

"хранящей части накопителя, обращение которым производится через общий ешифратар адреса, обновление ин20 формации н них осуществляется с IIo мощью обычной команды засылки, чта устраняет необходимость в специальной команде.

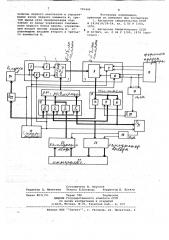

На чертеже представлена блок25 схема устройства.

Устройство содержит первый блок

l памяти, включающий накопитель 2, дешифраторы записи 3 и считывания 4, "элементы 5 .и 6 И, второй блок 7 па30 мяти, включающий накопитель 8, узел

9 записи 10 считывания, регистр 11 регЕнерации, группу 12 элементов И, узел 13 усилителей, объединяющий усилитель 1 4 первого адресного поля, -35 усилитель 15 информационного поля и усилитель 16 второго адресного поля, узел 17 синхронизации, элемент 18 ИЛИ, узел 19 формирования адреса запроса, элементы 20,21 и

40 22 И, коммутатор 23 ввода, регистр

24 адреса, коммутатор 25 нынода, дешйфратор 26 и узел 27 согласовайия с объектом.

Устройство работает следующим

45 образом.

Работа устройства происходит за два цикла обращения к накопителям под уйравлением импульсов, последовательно появляющихся на выходах узла 17 при условии существования сигнала на одном из выходов узла 19.

Допустим, имеется сигнал запроса на вывод информации, то есть возбужден один из выходов узла 19. Этот сиг- нал запросов готовит цепи узлов 9 . и 10 для обращения к одной из ячеек накопителя 8, а именно к той, котоФ рая соответствует данному запросу.

Си гнал са второго йьжода узла 17, постуйающий на управляющий вход

60 узла 10 считывания фиксированных ячеек, инициирует считывание упомянутой фиксированной ячейки, На выходах узла 13 усилителей появляются сигналы и информация перного адрес- .

65 ного паля слова, хранившегося в

705440 рации слова обмена, обновление адреса очередной ячейки обмена в фиксированной ячейке накопителя 8, Работа по приему информации от источников отличается от описанной выше тем, что в6збуждаются один иэ выходов узла 19 и присутствует сигнал на выходе элемента 18 ИЛИ, который через элемент 20 И на втором такте считывания блокирует выходы усилителей 16 информационного поля разрядов слова обмена. Тем самым производится обнуление этого поля. Одно- временно с выхода узла 27 информация через коммутатор 23 ввода и через отверстие на этом такте элементы И группы 12 поступает на регистр 11.

В остальных тактах работа по приему .информации не отличается от работы по выдаче.

5О бО опрашейной фиксированной ячейке, с выходов усилителя 14 записывается в. регистр 24 адреса, так как элемент 22 И открыт сигналом узла 17. B первом адресном поле слова обмена хранится очередной адрес ячейки из поля ячеек обмена, расположеннога в накопителе 2 и соответствующего данной ячейке накопителя

8 или,что то же самое, данному 3arlpoсу на обмен.На следующем такте работы устройства возбуждается третий выход узла 17, что приводит к чтению накопителя по адресу из регистра 24. На выходах узла 13 усилителей появляются сигналы, которые через группу 12 записываются в ре-гистр 11. Кроме того, информация иэ второго адресного поля слова обмена поступает через элемент 21

И на дешифратор 2б, в результате чего коммутируется соединение между одним из входов узла 27 и выходом усилителя 15 посредством коммутатора 25. На третьем такте работы устройства возбуждается первый выход узла 17. В результате этого 25 информация из регистра 11, то есть все слово обмена, считанное во втором такте считывания, записывается в накопитель 2 по своему адресу, по-.прежнему находящемуся в регистре

24, и в накопитель 8 с помцью узла 9, причем в ту же ячейку, которая опрашивалась на первом такте. В первом адресном поле слова записан адрес следующей ячейки из поля ячеек обмена накопителя 2, к которой будет произведено обраце" ние при повторн6м возбуждении того же выхода узла 19.

Так как на первом такте считывания используется только информация иэ первого адресного поля слова об" мена, хранящегося в фиксированной ячейке накопитлея 8, та можно ска зать, что на третьем такте (такте записи) производится, помимо регенеТаким образом, устройство обеспечивает обмен информацией между устройствами-источниками и приемниками ,информации, подключаемыми к узлу согласования с объектом, и накопителем первого блока памяти. С другой стороны, этот накопитель может быть связай с ЗВМ для оперативного анализа и изменения содержащихся в нем данных.

Формула изобретения

Устройство для обмена информацией, содержацее два блока памяти, регистр адреса, регистр регенерации, группу элементов И, коммутатор ввода, коммутатор вывода, узел согласования с объектом, узел синхронизации, узел усилителей, элементы И и ИЛИ, дешифратор и узел .формирования адреса запроса на обмен, причем выход регистра адреса, входом соединенного через первый элемент И с первым выходам узла усилителей, подключен к адресному входу первого блока памяти, информационные вход и выход которого . соединены соответс венно с выходом регистра регенерации и информационным входом второго блока памяти, информационный выход которого йодключен ко входу узла усилителей, а группы адресных входов записи и считывания соединены соответственно с первой и второй группой выходов узла формирования адреса запроса, первый, второй и третий выходы узла усили елей подключены соответс+венно к первому, второму и третьему входам группы элементов, выход которой соединен с информационным входом регистра регенерации, управляющий вход которого соединен с первым выходом узла синхронизации И входам

Управления записью второго блока памяти, вход управления считыванием которого подключен ко второму выхо-. ду узла синхрониз щии, выходы и входы узла согласования с объектом подключены соответственно ко входам коммутатора ввода, соединенного выходом с четвертым входом группы элементов H,ê выходам коммутатора вывода, соединенного входом со вторым вь|ходом узла усилителей, о т л и— ч а ю щ е е с я тем, что, с целью упроцения устройства, вторая группа выходов узла формирования адреса запроса соединена с соответствующими входами элемента ИЛИ, соединенного через второй элемент И со входом блокировки узла усилителей, третий выход которого через третий элемент

И подключен ко входу дешифратора, coeäèíåíHoão выходами с адресными входами соответственно коммутатора ввода и вывода, первый и второй выходы узла синхронизации подключены соответственно ко входу управления

705440

Составитель В. Вертлиб

Редактор Д. Милитеев Техред И.Асталош Корректор В. Бутяга

Заказ 8031/51

Тираж 780 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4 записью первого накопителя и управляющему входу первого элемента И, третий выход узла синхронизации подключен ко входу управления считыванием первого блока памяти, управляющим входом группы элемнтов И, управляющими входами второго и третьего элементов И.

Источники, информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9 2414618/18-24, кл. G 06 F 3/04, 1976.

2. Авторское свидетельсвто СССР

9 507865, кл. G 06 Р 3/00, 1974 (прототип) .