Многоканальное операционное устройство

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ.

Союз Советских

Сещиалистических

Республик

/ ч (22) Заяелеио 090376 (21) 23323 33/18-24 с присоединением заявки Мо

G 06 F 7/38

G 06 F 15/00

Государственный кон нтет

СССР но делан нзобретенаа и открытн1 (23) Приоритет (53) УДК 681Л25 (088.8) Опубликовано 25.1279 Бюллетень М 47

Дата опубликоааиия описания 281279. (72) Авторы

ИЗОбрЕтЕИИя В. H. Ãîðøòåéí, В.M . Ïèâíåíêo, Ю.Х.Сахин и Г.А. Бибик (71} Заявитель (54) МНОГОКАНАЛЬНОЕ ОПЕРАЦИОННОЕ УСТРОИСТВО

Устройство относится к области вычислительной техники и может быть использовано для построения уст- ройств с векторной обработкой информации.

Извес гно устройство, содержащее блок управления, арифметическое устройство., регистр адреса, регистр результата, коммутаторы (1).

Недостатком известного устройства является низкое .быстродействие, Наиболее близким к изобретению техническим решением является устройство, в котором первый, второй и третий входы каждого из каналов являются с первым, вторым и третьим входами устройства, первый выход каждого иэ каналов соединен с соответствующими входами других каналов, выходы всех каналов соединены с выходом устройства, каждый канал содержит блок управления, первыйвыход которого соединен с первым входом регистра адреса и череэ элемент задержки с первым входом регистра результата, второй вход которого соединен со вторым выходом блока управления и выходом первого коммутатора, первый вход которого .соеди нен с третьим выходом блока управления и. первым входом арифметического блока, первый выход которого через

5 сдвигатель соединен. со вторым входом первого коммутатора, третий вход которого соединен со вторым выходом арифметического блока и входом сдвигателя, третий выход арифметического блока соединен с первым входом блока управления, четвертый выход которого соединен с первым входом второго коммутатора, выход узла формирования адреса соединен со вторым входом регистра адреса, выходы которого и регистра результата соединены с первым выходом канала, первый вход которого соединен со вторым входом второго коммутатора, первый выход которого соединен

20 со вторым выходом кан,а, бл к схем сравнения, входы которого соединены со входами канала, второй вход канала соединен со вторым входом

25 блока управления (2) .

Это устройство имеет следующие недостатки: — выполняет операции только над однотипными и одноформатными операндами. для выполнения операций

705444

35 над числами различных типов и форматов в программы добавляются дополнительные команды преобразования типов и Форматов; — выполнение процедур прерывания (например, переполнение результата 5 сложения целочисленных операндов) производится программным методом. Это не только замедляет выполнение програМмы,но и значительно ее усложняет — для предварительного, точного указания времени выдачи результата необходимо рассчитывать операцию на самый сложный (длинный) случай, Потери времени из-за этого особенно значительны при коротких операциях. 15

Целью изобретения является повышение производительности устройства.

Поставленная цель достигается тем, что в каждый. канал введены коммутатор команд, коммутатор, операн- 20 дов, блок регистров, операндов, блок регистров команд, узел управления передачей операндов и команд, дешифратор, блок коммутаторов, второй элемент задержки, причем входы блока коммутаторов соединены со входами канала и выходом блока схем сравнения, выход блека коммутаторов соединен с первым входом блока регистров операндов, второй вход которого соединен с первым выходом узла управ-.

30 ления передачей операндов и команд, второй выход которого соединен с .первыми входами коммутаторов команд и операндов, выход блока регистров операндов соединен с первым входом узла управления передачей операндов и команд и вторым входом коммутатора операндов, выход которого соединен с третьим входом блока управления, вторым входом арифметического блока 40 и через дешифратор с третьим входом арифметического блока, входы блока регистров команд соединены с первым входом канала и вторым выходом второго коммутатора, выход блока регистров 45 команд соединен через коммутатор команд с входом узла формирования адреса и четвертым входом блока управления и через блок схем сравнения с вторым входом узла управления 50 передачей операндов и команд, третий вход которого через второй элемент задержки соединен с четвертым выходом блока управления.

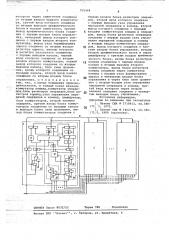

Блок-схема устройства приведена на чертеже.

Устройство содержит каналы 1, каждый из которых содержит блок 2 управления, арифметический блок 3., коммутаторы 4,5, регистр 6 адреса, регистр 7 результата, сдвигатель 8, коммутатор 9 операндов, коммутатор

10 коМанд, узел 11 формирования адреса, узел l2 управления передачей ,операндов и команд, блок 13 регистров команд, блок 14 коммутаторов, блок 15 схем сравнения, блок 16 регистров операндов, дешифратор 1.7, элементы 18,19 задержки, Устройство работает следующим образом.

Каждый канал 1 операционного устройства ориентирован на выполнение группы алгоритмически близких операций. Например, канал умножения выполняет..умножение, целочисленное умножение, умножение с удвоенной точностью и т,д

Устройство управления вычислительной машины (УУВМ) рассылает каждому каналу 1 команды, на выполнение которых он ориентирован. Команда содержит код операции, адреса операндов и адрес результата. Адреса относительные, в частности принято, что адрес— это номер регистра блока 16, в котором находится операнд, или если его там еще нет (является Результатомоперации, выполняемой каким-либо каналом 1 или УУВМ), то это номер регистра блока 16, назначенного для него. Для результатов всех операций назначаются разные регистры блока 16, в котором они находятся в течение всего времени выполнения данной программы. Блок 13 принимает команду на один из свободных регистров. Последовательность использования свободных регистров задается коммутатором 5. Количество Регистров может быть от одного до д и определяется в основном количеством и производительностью каналов операционного устройства. При этом увеличение числа регистров способствует как ускорению дешифрации команд, так и ускорению выполнения операций, Адреса операндов, содержащиеся в командах, из блока 13 подаются на соответствующие схемы сравнения блока 15, на которые поступают также адреса операндов. При совпадении адресов блок 15 вырабатывает сигнал сравнения> разрешающий соответствующему коммутатору блока 14 пропустить операнд на соответствующий регистр блока 16. Возможен одновременный прием операндов на разные-регистры .по различным направлениям. Таким образом каждая команда блока 13 собирает свои операнды.

Узел 12 вырабатывает и запоминает сигнал-комплект операндов для данной команды, когда ее операнды находятся в блоке 16 или пришли их адреса.

Приход адресов..определяется по сигналу сравнения, вырабатываемому блоком 15. Адрес опережает операнд на такт. Если комплект операндов выработан по адресам, а операнды в следующем такте не появились, то сигнал комплекта исчезает и команда продолжает собирать свои операнды, При наличии нескольких комплектов опе705444 рандрв узел 12 устанавливает очередность исполнения команд. Например, по порядку их прихода. По сигналу комплекта операндов коммутатор 9 подключает регистры блока 16, содержащие .операнды данной команды или подготовленные для нх приема, к входу блока 2, дешифратора 17, арифметического блока 3, а коммутатор

10 пропускает код операции на вход блока 2 и адрес результата — на вход узла 11. Так как адрес опережает операнд на такт, то подготовка регистров блока 16 к приему операндов и коммутаторов 9,10 и коммутаторов блока 14 происходит до появления операндов на входе блока 16 и тем самым операнд без лишних задержек проходит в дешифратор 17, арифметический блок 3, а его тег и признак наличия операнда в блок 2.

Каждый операнд кроме числовой или логической информации несет еще служебную информацию, определяющую тип-формат операнда и заключенную в разрядах тега операнда. По коду операции и тегам операндов блок 2 определяет алгоритм вычислений.

Так как, фактически, запуск операции начинается по сигналам сравнения адресов и выработанным по ним сигналам комплекта операндов, то решение о правильности запущенной операции определяется блоком 2 путем анализа признаков наличия операндов после их прихода. После приема команды каким-либо регистром блока

13 коммутатор 5 блокирует все последующие приемы на данный регистр, пока адрес результата не попадает на первую станцию поточной обработки узла 11. После этого блок 2 выда- 4р ет сигнал, снимающий блокировку коммутатором 5 регистра данной команды. Этот же сигнал, задержанный на такт элементом 19, снимает блокировку с регистров операндов данной ф5 команды (находящихся в блоке 16), которая устанавливается узлом 12 после приема операнда, и снимает сигнал наличия комплекта операндов данной команды. Дешифратор 17 опре-. 5p деляет, какие позиции операндов не имеют значащих разрядов. Поэиция— это число разрядов, на которое нужно сдвинуть операнд, чтобы изменить его порядок на единицу, 55

Для ускорения операций с разными тип-Форматами данных, кроме обработки операндов, предписанной командой, арифметический блок 3 по сигналу дешифратора 17 выдает сигналы количества операций обработки полей операндов, фиксирует переходы результата из оцного тип-формата в другой и на основании этого выдает соответствующий код сдвига сдвигателю 8.

:Сдвигатель 8 содержит регистр с разрядностью, достаточной для выдачи, числа удвоенной точности, и сдвнговую логику, позволяющую производить любой кратный. одной позиции сдвиг согласно коду сдвига, поступающему с арифметического блока 3. Коммутатор по управляквим сигналам блока 2 пропускает на регистр 7 со сдвигателя

8 или непосредственно с арифметического блока 3 число в необходимом представлении, Разная выдача обусловлена тем, что результат вычислений может выдаваться либо с фиксированным заранее известным сдвигом, либо с произвольным сдвигом. Например, если результат — целое число, то он выдается с арифметического блока, 3, а произведение целый на вещественный, разность вещественных чисел пропускается через сдвигатель 8. Узел 11 содержит столько станций поточной обработки, сколько их имеет арифметический блок 3. Передача адреса результата со станции на станцию производится так же, как и в арифметическом блоке 3, только с опережением на один такт, ло сигналам блока 2. Сигнал, управляющий приемом регистра 6, после задержки на такт элементом 18 поступает для управления приемом регистра 7.

Информация с регистров 6 и 7 поступает на выход устройства или

;на входы каналов для дальнейшей обработки.

Изобретение позволяет повысить производительность за счет уменьшения числа нормализаций полноформатных чисел, регулирования конфликтных ситуаций аппаратным способом, исключения необходимости предварительного указания времени выдачи

Результата для самого длинного случая, Формула изобретения

Многоканальное операционное устройство, в котором первый, второй и третий входы каждого из каналов являются первым, вторым и третьим входами устройства, первый выход каждого из каналов соединен с соответствующими входами других каналов, выходы всех каналов соединены с выходами устройства, каждый канал содержит блок управления, первый выход которого соединен с первым входом регистра адреса и через первый элемент задержки с первым входом регистра результата, второй вход которого соединен со вторым выходом блока управления и выходом первого коммутатора, первый вход которого соединен с третьим выходом блока управления и первым входом арифметического блока, первый выход

705444

° ° °

-Подписное

Тираж 780

ЦНИИПИ Заказ 8032/52 филиал ППП Патент, r. ужгород, ул, Проектная, 4 которого через сдвигатель соединен со вторым входом первого коммутатора, третий вход которого соединен со вторым выходом арифметического блока и входом сдвигателя, третий выход арифметического блока соединен с первым входом блока управления, четвертый выход которого соединен с первым входом второго коммутатора, выход узла формирования адреса соединен со вторым входом регистра адреса, выходы которого и регистра результата соединены с первым выходом канала, первый вход которого соединен со вторым входом второго коммутатора, первый выход которого соединен со вторым выходом канала, блок схем сравне-- ° ния, входы которого соединены со входами канала, второй вход канала соединен со вторым входом блока управления, о т л и ч а ю щ е е с я тем, что, с целью повышения производительности, в каждый канал введены коммутатор команд,,коммутатор операндов,блок .регистров операндов, блок регистров команд, узел управления передачей операндов и команд, дешифратор, блок коммутаторов, второй элемент задержки, причем входы блока коммутаторов соединены со входами канала и выходом блока схем сравнения, вы ход блока коммутаторов соединен с первым входом блока регистров операндов, второй вход которого соединен с первым выходом узла управления передачей операндов и команд, второй выход которого соединен с первыми входами коммутаторов команд и операндов, выход блока регистров операндов соединен с первым входом узла управления передачей операндов и команд и вторым входом коммутатора операндов, выход которого соединен с третьим входом блока управления, вторым входом арифметического блока и через дешифратор с третьим входом арифметического блока, входы блока регистров 5 команд соединены с первым входом канала и вторым выходом второго коммутатора, выход блока регистров команд соединен через коммутатор команд с входом узла формирования адреса и четвертым входом блока управления и через блок схем сравнения с вторым входом узла управления передачей операндов и команд, третий вход которого через второй

25 элемент задержки. соединен с четвертым выходом блока Управления.:

Источники информации, принятые во внимание при экспертизе

1. Патент CII1A Р 3718912, кл.34030

2 .. Патент США Р 3462744, кл. 340 172 ° 5, 1969 (прототип) .