Устройство для деления

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

«»705447

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. сеид-ву (22) Заявлено 090776 (21) 2382863/18-24 (51)М. Кл 2 с присоединением заявки 89

G 06 F 7/39

Госуаарственныа комитет

СССР по аелаи изобретеннЯ и открытиЯ (23) Приоритет

Опубликовано 251279, Бюллетень Й9 47 (53) УДК 681. 327 (088.8) Дата опубликования описания 281279 (72) Авторы изобретения

Н. В. Черкасский и В. В. Черкасская (7f) Заявитель (54) УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ

Изобретение относится к области вычислительной техники и может быть использовано в арифметических устройствах для деления большого массива многоразрядных чисел.

Известны устройства для делЕния ш — (з °

В этих устройствах при отрицательном остатке очередного вычитания не производится восстановление положительного остатка, а вместо вычитания делителя в следующем также осуществляется его сложение. Как правило, за один такт образуется один очередной остаток и одна цифра частного, поэтому при делении большого массива многоразрядных чисел эти устройства не обладают достаточным быстродействием.

Наиболее близким к изобретению является устройство для деленйя, содержащее вычислительный блок, состоящий из регистов делимого, делителя, частного, сумматора, группы элементов И и узла анализа знака сумматора, причем первый вход каждого разряда сумматора подключен к выходу соответствующего разряда регистлех.*нмОГ<), а в îpîA В ход — к Вы2 ходу соответствующего элемента И, первый вход которого соединен с инверсным выходом соответствующего раз ряда регистра делителя, входы узла анализа знака сумматора подключены к выходам знаковых разрядов сумматора, входы регистра делимого и делителя подключены ко входам устройства

f41

Недостаток данного устройства состоит в том, что при делении чисел, имеющих значительную разрядность, а также массивов из пар чисел, зна- чительно увеличивается время выполнения деления, что является результатом увеличения числа тактов данной операции.

Цель изобретения — увеличение быстродействия устройства при делении больших массивов п-разрядных чисел.

Данная цель достигается тем, что вычислительный блок содержит триггер, вход которого подключен к выходу узла анализа знака сумматора, а выход соединен со входом младшего разряда регистра частного и вторыми входами элементов И, кроме того, устройство дополнительно содержит (n — 1) вычислительных блоков, вы705447 полне««ых аналогично первому вычислительному блоку, причем вход i-го (i = 1, 2,, n — I ) разряда регистра делимого каждого вычислительного блока устройства соединен с выходом (i + 1) -ro разряда суммато- 5 ра предыдущего вычислительного блока, вход i-ro (i = 1, 2,, n) разряда регистра делителя каждого вычислительного блока соединен с выходом i-ro разряда регистра делителя предыдущего вычислительного блока, вход i ro (i = 1, 2, ..., n — I) разряда регистра частного каждого вычислительного блока соединен с выходом (i + 1) -го Разряд Р гистра частного предыдущего вычислительного блока, выходы регистра частного n-ro вычислительного блока подключен к выходам устройства.

Кроме того, с целью сокращения оборудования, регистр частного в

20 к-ом вычислительном блоке устройства (к = 1, 2. .. n) содержит к разрядов.

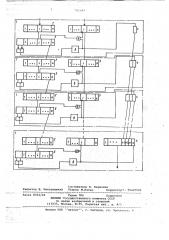

На чертеже представлена функциональная схема устройства для деления.

Устройство для деления содержит и вычислительных блоков 1, каждый из которых содержит регистры делимого 2., делителя 3 и частного 4, сум- З0 матор 5, группу элементов И 6, узел анализа знака сумматора 7,триггер 8.

Выходы регистра 2 соединены с первыми входами сумматора 5, вторые входы которого подключены к выходам 35 группы элементов И 6, первые входы коТорых подклниены к инверсным выходам регистра 3, а вторые входы — к выходу триггера 8, который подклннен также ко входу младшего разряда ре- 40 гистра частного 4.Выходы знаковых разрядов сумматора 5 соединены со входами узла анализа знака сумматора 7, выход которого подключен ко входу триггера 8.Входы 1-х разрядов (i = 45

1, 2, ..., n — I) регистра 2 каждого вычислительного блока 1, начиная со второго, подключены к выходам (i +

+ 1)-х разрядов сумматора 5 предыдущего вычислительного блока 1 . Выходы 1-х разрядов (i = 1, 2, ..., n) регистра 3 каждого вычислительного блока 1, начиная со второго, подключены к выходам i-х разрядов

Регистра 3 предыдущего вычислительного блока 1. ;Входы i — х разрядов (i = 1, 2, ..., n — Е) Регистра 4 каждого вычислительного блока 1, начиная со второго,,подкл;очены к выходам (i + 1) -х разрядов регистра

4 предыдущего вычислительного бло- б0 ка 1 ° Входы регистров 2 и 3 первого

-вычислительного блока 1 подклеены ко входам устройства, выходы регистра

4 n-ro вычислительного блока 1 подключены к выходам устройства. Регистр б5

4 к-го вычислительного блока 1 (к

1, 2, ..., n) содержит к разрядов.

Деление выполняется беэ восстановления остатка в два полутакта следующим образом.

В первом полутакте первого такта в регистр 2 первого вычислительного блока 1 записывают первое делимое, а в регистр 3 — первый делитель.

Из делимого вычитается делитель.

При этом триггер 8 сброшен и единица на его выходе не препятствует сложению в обратном коде. Одновременно содержимое регистра 3 переписывается в регистр 3 последующего вычислительного блока.

Во втором полутакте происходит анализ знака сумматора 5 узлом анализа знака сумматора 7 и запись перного разряда частного в младший разряд регистра 4. Если бстаток получился положительный, частное равно единице и элементы И 6 останутся открытыми. Если остаток отрицательный, разряд частного равен нулю, триггер

8 опрокинется и элементы И 6 закроются, вычита«ия не произойдет (на все входы сумматора 5 вместо делителя поступят нули) и на комбинационном сумматоре 5 восстановится первоначальное значе«ие делимого. Со сдвигом влево значения сумматора 5 перепишется в регистр 2 последующего вычислительного блока 1, а значение регистра 4 — в регистр 4 последующего вычислительного блока 1.

В первом полутакте второго такта в освободившиеся регистры 2 и

3 первого вычислительного блока 1 запишутся новые числа, которые вычитают в сумматоре 5 первого вычислительного блока 1 для получения первого остатка второй пары чисел.

Одновременно в сумматоре 5 второго вычислительного блока 1 получают второй остаток первой пары чисел.

Во втором полутакте второго такта получают первый разряд результата деления второй пары чисел в регистре 4 первого вычислительного блока 1 и второй разряд результата деления первой пары чисел в регистре 4 второго вычислительного блока

1. Затем содержимое предыдущих вычислительных блоков 1 переписывают

J в последующие, освобождая первый вычислительный блок для принятия следующей третьей пары чисел.

Результат деления каждой пары чисел образуется за п тактов, причем в каждом вычислительном блоке 1 образуется очередная цифра частного, аналогично тому» как это было описано выше.

705447

Пример. Разделить 625 на 25.

В двоичной системе эти числа представлены кодами 1001110001 и 11001

1001110001 P.2 0 P.4

11001 P.З переполнение См.5 5

01 P.4

1001110001 P.2 . 11001 P.З

+0011100001 См.5

011 P.4

0011100001 P.2

11001 P.3

+0000011001 См.5

0110 Р.4

0000011001 P.2

11001 P. 3 переполнение См.5

0000011001 P.2

11001 P. 3 переполнение См.5

0000011001 P.2 011 001 Р.4

11 001 Р.З

+0000000000 См.5

При обработке массива 2000 24-разрядных чисел (m =- 2000, п = 24) достигнутое увеличение быстродействия по сравнению с прототипом составит

25

2000-24

Л д 20 раэ. (m-I ) +п 1999+24 30

Однородность структуры устройства . можно использовать при проектировании больших интегральных схем.

Формула изобретения 35

1. Устройство для деления, содержащее первый вычислительный блок, состоящий из регистров делимого, делителя, частного, сумматора, группы элементов И и узла аналйза знака 40 сумматора, причем первый вход каждого разряда сумматора подклкнен к выходу соответствующего разряда регистра делимого, а второй вход — к выходу соответствующего элемента И, 45 первый вход которого соединен с инверсным выходом соответствующего разряда регистра делителя, входы узла анализа знака сумматора подключены к выходам знаковых разрядов сумматора,входы регистра делимого и делителя подклкчены ко входам устройства, о т л и ч а ю щ е е с я тем, что, с целью увелйчения, быстродействия устройства при делении больших массивов п ðàýðÿäíûõ чисел, вычислительный блок содержит триггер, вход которого подключен к выходу узла анализа знака сумматора, а вы" ход соединен со входом младшего разряда регистра частного и,вторыми входами элементов-И, кроме того, устройство дополнительно содержит (n — I) вычислительных блоков, выполненных аналогично первому вычислительному блоку, причем вход i-ro (i = 1, 2, ..., n — I) разряда регистра депимого каждого вычислительного блока устройства соединен с выходом (i + 1) -го разряда сумматора предыдущего вычислительного блока, вход i — ro (i = 1, 2, n) разряда регистра делителя каждого вычислительного блока соединен с выходом i-го разряда регистра делиТеля предыдущего вычис-. лительного блока, вход i-ro (i

1, 2, ..., n — I) разряда регистра частного каждого вычислительного блока соединен с выходом (i + 1) -ro разряда регистра частного предыдущего вычислительного блока, выходы регистра частного и-го вычислительного блока подключен к выходам устройства.

2. Устройство для деления по п. 1, о т л и ч а ю щ е е с я тем, что, с целью сокращения оборудования, регистр частного в к-ом вычислительном блоке устройства (к = 1 2, n) содержит к разрядов, Источники информации, принятые во внимание при экспертизе

1. Патент CttIA 9 3319057, кл. 235 164, 1967.

2. Патент CttIA tt 3492468, кл. 235164, 1970.

3. Патент Франции 9 1482854, кл. G 06 Fi 1968, 4. Авторское свидетельство СССР

Р 398948, кл. G06 F 7/39, 1971 (про- тотип) .

Тираж 780 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 8352/66

Филиал ППП Патент, r. Ужгород, ул. Проектнал, 4

Составитель В. Березкин

Редактор Д. Мепуришвили Техред М.Петко корректорГ. Решетник