Регистр сдвига

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОЬВЕТЕ Н ИЯ

К АВТОРСКОМУ СВИДИЕЛЬСТВУ

Союз Советскин

Социалистииескик

Республик

< "705522 (61) Дополнительное к авт. свид-ву— (22) Заявлено 07.07.77 (21) 2507716/18-24 (51) 1 К1 2

G11 С 19/00 с присоединением заявки №вЂ” (23) Приоритет — -

Гасударственный квинтет ссср не делам изобретений н открытий (53) УДК 681.327. . 66 (088.8) Опубликовано 25.12.79. Бюллетень № 47

Дата опубликования описания 10.01.80

Г. С. Брайловский, И. M. Лазер H Ю. С. Крылов

I (72) Авторы изобретения (7!) Заявитель (54) РЕГИСТР СДВИГА

Изобретение относится к области построения структур цифровой вычислительной техники и дискретной автоматики на потенциальных логических элементах.

Известен регистр сдвига (1), построенный на элементах И вЂ” ИЛИ вЂ” НЕ.

Наиболее близким из известных по технической сущности является регистр сдвига (2), содержащий в каждом разряде RSтриггер, причем управляющие входы RSтриггеров всех разрядов соединены с шиной синхроимпульсов.

Недостатки таких регистров сдвига заключаются в использовании большого количества логических элементов И вЂ” ИЛИ вЂ” ЙЕ (четыре логических элемента в каждом разряде) и большой потребляемой мощности.

Целью изобретения является упрощение регистра сдвига (уменьшение количества логических элементов) и снижение потребляемой мощности. Это достигается тем, что в регистр сдвига для каждого нечетного и четного разрядов введен двоично-троичный триггер, выходы которого подключены к соответствующим входам RS-триггеров нечетного и четного разрядов, первые входы двоич2 но-троичного триггера соединены с шиной синхроимпульсов, вторые входы двоичнотроичного триггера подключены к информационным шинам, третьи входы — к выходам RS-триггера нечетного разряда соответственно, выходы RS-триггеров нечетных разрядов соединены с первыми входами RSтриггеров четных разрядов, а выходы RSтриггеров четных разрядов — с информационными шинами.

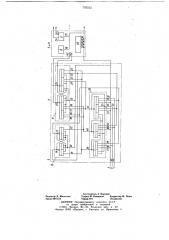

Сущность изобретения поясняется чертежом, где приведена функциональная схема регистра сдвига.

Регистр сдвига содержит пары соседних разрядов 1 и 2, 3 и 4, шину сихроимпульсов 5, информационные шины 6 и 7, каждый нечетный разряд 1, 3..., содержит RSтриггер 8, каждый четный разряд 2, 4..., содержит RS-триггер 9, входы 10, 11 и 12 триггера 8, выходы 13 и 14 триггера 8, входы 15 — 23 и выходы 24, 25 триггера 9, двоично-троичный триггер 26 входы 27—

38 триггера 26, выходы 39, 40, 41 триггера

26 информационные входы 42, 43.

Функционирование регистра сдвига происходит следующим образом.

705522

Формула изобретения

3s ае

so

Пусть в начальный момент времени на выходах 14 и 25триггеров 8 и 9 и на информационном входе 42 установлены сиг. налы логического нуля. При этом на выходах 39 и 40 триггера 26 устанавливаются сигналы логической единицы, а на выходе

41- сигнал логического нуля. Изменение сигналов на информационных шинах 6 (42), 7 (43) допускается только при сигнале логического нуля на входе 5 синхроимпульса.

После появления сигнала логи ческой единицы на входе 42 и логической единицы на входе 5 происходит переключение триггера

26, при этом сигнал логического нуля устанавливается на первом выходе 39 триггера 26. Переключение сигнала на входе 5 в состояние логического нуля вызовет переключение первого триггера 8, при этом на его выходе 14 устанавливается сигнал логической единицы. После появления сигнала логического нуля на входе 42 и логической единицы на входе 5 происходит переключение триггера 26, при этом сигнал логического нуля устанавливается на выходе 40.

Переключение сигнала 5 в состояние логического нуля вызовет переключение первого и второго триггеров 8 и 9, при этом на выходе 14 устанавливается сигнал логического нуля, а на выходе 25 — логической единицы. В следуюшем такте происходит установке на выходе 14 сигнала логической единицы, а на выходе 24 — сигнала логического нуля. Затем сигнал логической единицы на входе 5 вызывает переключение триггера 26 (на выходе 41 появляется сигнал логического нуля) . После чего сигнал логи-. ческого нуля на входе 5 вызывает переключение второго триггера 9 (на выходе 25 появляется сигнал логической единицы) и т. д. Сигнал логического нуля на первом выходе 39 триггера 26 подготавливает переключение первого триггера 8 в состояние логической единицы и второго триггера 9 в состояние логического нуля, если первоначально он находился в состоянии логической единицы. Сигнал логического нуля на втором выходе 40 триггера 26 подготавливает переключение первого триггера 8 в состояние логического нуля и второго триггера 9 в состояние логической единицы, если первоначально он находился в состоянии логического нуля. Сигнал логического нуля на третьем выходе 41 триггера 26 подготав IHBBpT переключение только второго триггера 9 четного разряда в состояние соответствуюшее состоянию первого триггера 8 нечетного разряда если первоначально их состояния не совпадают, при этом первый триггер 8 не переключается. Сдвиг информации от одной пары соседних разрядов к другой паре соседних разрядов происходит аналогично сдвигу информации в регистре прототипа. При этом сдвиг информации за один такт более, чем на один разряд исключаается, так как второй триггер 9 переключается при сигнале логического нуля на синхровходе 5, а триггер 26 при сигнале логической единицы на синхровходе 5.

Таким образом, предложение позволяет на 12,50 О уменьшить количество логических элементов И вЂ” ИЛИ вЂ” НЕ в схеме регистра сдвига. Кроме того, как видно из описания работы, каждая пара разрядов имеет три логических элемента И вЂ” ИЛИ вЂ” НЕ, находяшихся в состоянии логического нуля и четыре логических элемента И вЂ” ИЛИ вЂ” НЕ, находящихся в состоянии логической единицы. А у прототипа половина (четыре) логических элементов находится в состоянии логического нуля. Следовательно, выигрыш для каждой пары разрядов составляет один логический элемент, находящийся в состоянии логического нуля. Как известно, логические элементы ТТЛ в состоянии логического нуля потребляют мощность примерно вдвое большую чем в состоянии логической единицы. Поэтому выигрыш в снижении потребляемой мощности составит окол о 17%.

Регистр сдвига, содержащий в каждом разряде RS-триггер, причем управляющие входы RS-триггеров всех разрядов соединены с шиной синхроимпульсов, и информационные шины, отличающийся тем, что, с целью упрощения регистра и уменьшения потребляемой им энергии за счет установки триггеров в единичное состояние, в регистр сдвига для каждого нечетного и четного разрядов введен двоично-троичный триггер, выходы которого подключены к соответствующим входам RS — триггеров нечетного и четного разрядов, первые входы двоичнотроичного триггера соединены с шиной синхро-импульсов, вторые входы двоично-троичного триггера подключены к информационным шинам, третьи входы — к выходам

RS-триггера нечетного разряда соответственно, выходы RS-триггеров нечетных разрядов соединены с первыми входами RSтриггеров четных разрядов, а выходы RSтриггеров четных разрядов — с информационными шинами.

Источники информации, принятые во внимание при экспертизе

l. Авторское свидетельство СССР № 432602, кл. G 11 С 19/00, 19.02.72.

2. Букреев И. И. и др. Микроэлектронные схемы цифровых устройств. М, «Советское радио», 1976, с. 90, с. 142 (прототип).

705522

Составитель А. Воронин

Редактор Д. Милитеев Техред М, Левицкая Корректор М. Пожо

Заказ 8044/56 Тираж 681 Подписное

ЦН И И ПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, 5К вЂ” 35, Раушская наб., д. 4/5

Филиал П П П «Патент», г. Ужгород, ул. Проектная, 4