Ячейка памяти

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

Союз Советских

Социалистимескин

Республик («)705523 ((автоPCNOMV CBNgRTEllbCTBV (б! ) Дополнительное к авт. спид-ву(51 ),М. Кл. 2 (22) Заявлено 01.07.77 (21) 2503471/18-24 с присоединением заявки №-(23) Приоритет—

G 11 С 19/40

Государственный комитет

СССР по делам изобретений н открытий

Опубликовано 25.12.79. Бюллетень ¹ 47

Дата опубликования описания 10.01.80 (53) УДК 681.327. .66 (088.8) (72) A s Tàðû изобретения

Ь. Г. Коноплев и М. Ф; Пономарев

Таганрогский радиотехнический институт им. В. Д. Калмыкова (71) Заявитель (54) ЯЧЕЙКА ПАМЯТИ

Изобретение относится к области вычислительной техники и микроэлектроники, а более конкретно — к ячейкам памяти для микроэлектронных регистров сдвига.

Известны микроэлектронные регистры сдвига, которые полностью построены на 5 совмещенных транзисторных структурах и обеспечивают высокую степень интеграции элементов при выполнении их в составе БИС и низкую потребляемую мощность (I ) .

Наиболее близким к изобретению техническим решением является ячейка памяти, содержащая триггеры, выполненные на транзисторах, эмиттеры которых соединены с базой входного транзистора, базой опорного транзистора и шиной нулевого потенциала, коллекторы входного транзистора подключены соответственно к базам вторых транзисторов триггеров, эмиттер входного транзистора соединен с входной шиной, эмиттер опорного транзистора соединен с шиной питания, выходную и тактовую шины (21 .

Известные ячейки памяти обладают низким быстродействием.

Цель изобретения.— повышение быстродействия ячейки памяти.

Поставленная цель достигается тем, что в нее введены транзисторы связи, токозадающий транзистор, блокировочнь;и транзистор и выходные транзисторы, коллекторы которых соединены с выходной шиной, эм иттеры выходных транзисторов соединены с базами первых транзисторов триггеров и с первымиколлекторами токозадающего транзистора, а базы — с базами транзисторов связи, эмиттером блокировочного транзистора, базой токозадающего транзистора и шиной нулевого потенциала, эмиттеры транзисторов связи соединены с коллекторами опорного транзистора и коллекторами блокировочного транзистора, коллекторы транзисторов связи подключены к базам первых транзисторов триггеров, вторые коллекторы токозадающего транзистора соединены с базами вторых транзисторов триггеров, база блокировочного транзистора соединена с эмиттером токозадающего транзистора и тактовой шиной.

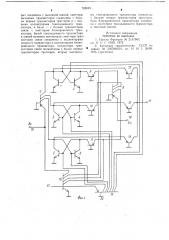

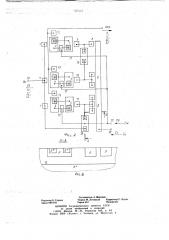

На фиг. 1 изображена принципиальная схема ячейки памяти; на фиг. 2 — вариант

705523 ее топологии; на фиг. 3 — разрез А — А на фиг. 2.

Ячейка памяти содержит три триггера на транзисторах 1 — 6, входной транзистор 7, опорный транзистор 8, транзисторы 9 — 11 связи, выходные транзисторы 12 — 14, токозадающий транзистор 15 и блокировочный транзистор 16.

Работает ячейка следующим образом.

Ячейка памяти реализует функцию

Д-триггера и может функционировать в режимах установки и хранения.

В режиме установки ток в тактовую шину 17 не подается. В шину 18 питания подается ток питания. Топология коллекторов транзистора 8 такова, что в базы левых транзисторов триггеров через транзисторы связи задается ток различной величины, что определяет разные пороги срабатывания триггеров. Для рассматриваемого примера надо задать величину тока коллектора опорного транзистора 8, соединенного с транзистором 9, 0(3„<10 мка, ток коллектора, соединенного с транзистором 10, должен быть 10 мка (3< 20 мка, а ток последнего коллектора должен быть 20 мка (1„30 мка.

Логический сигнал подается по входной шине 19 в эмиттер транзистора 7. При значении логического сигйала соответствующему нулю (ток равен нулю) ток коллектора транзистора 7 равен нулю. Так как в базы левых транзисторов триггеров от транзисторов 9 — 11 подается ток, то транзисторы 1,3 и 5 насьпцены и на их коллекторах фиксируются потенциал ы, близкие к потенциалу. шины 20 нулевого потенциала.

При подаче на вход логического сигнала соответствующего значениям один, два и три (токи 10, 20 и 30 мка для рассматриваемого примера), будет происходить сравнение токов в соответствующих триггерах и перек. почепие их в такие состояния, при которых транзисторы 2, 4 и 6 — включены, а транзисторы 1, 3 и 5 — выключены. Итак,, при входном сигнале, соответствующем значению ноль, транзисторы 2, 4 и 6 — выключены, при сигнале, соответствующем значению один, транзистор 2 включен, а 4 и 6 выключены, при сигнале соответствующем значению два, транзисторы 2 и 4 включены, а 6 выключен, при сигнале, соответствующем значению три, транзисторы 2, 4 и 6 вкл ючены.

После переключения триггеров в состояния, соответствующие входному логическому сигналу, процесс установки заканчивает-. ся и можно переходить к режиму хранения

В режиме хранения при подаче йМйульса тока по тактовой шине 17 через транзистор

15 во все базы трайзисторов триггеров задаются примерно равные токи. Транзистор

16 насыщается и блокирует эмиттерные цепи транзисторов 7 и 9 — 11, при этом входной ток логических сигналов и ток от опорного транзистора отводится через транзистор 16 в шину 20. Бистабильные состояния триггеров, заданные в режиме установки, поддерживаются в режиме хранения токами, поступающими от транзистора 15.

Если один из транзисторов 2, 4 или 6 включен, то часть тока, попадающего на его базу от транзистора 15, ответвляется через транзисторы соответственно 12, 13 или 14 в выходную шину 21, если же один из транзисторов 2, 4 или 6 выключен, то весь его базовый ток отводится в коллектор одного из включенных транзисторов 1, 3 или 5.

Таким образом, в зависимости от состояни и триггеров, которые определяются входным логическим сигналом во время t1, установки, в выходную шину будет ответвляться во время t „+ 1 (при подаче тактового импульса) ток определенной величины: при логическом сигнале, соответствующем значению ноль, нулевой, при логическом сигнале, соответствующем значению один, 1О

13 то один квант через транзистор 12 (!О мка), при логическом сигнале, соответствующем значению два, — два кванта, через транзисторы 12 и 13 и при логическом сигнале, соответствующем значению три, — три кванта через транзисторы 12, 13 и 14.

На фиг. 2 видно, что для увеличения степени интеграции и повышения быстродействия за счет снижения емкостей р — п переходов, эмиттерные области введенных транзисторов 12 — 14 конструктивно совмещены с базами транзисторов 2, 4 и 6, коллекторые области транзистора 15 совмещены с база- ми транзисторов 1 — 6, коллекторные области транзисторов 9 — 1! совмещены с базами транзисторов 1, 3 и 5, базы введенных р — п — р транзисторов и эмиттер п — р — п транзистора объединены в обложке в общей области п-типа.

Формула изобретения

Ячейка памяти, содержащая триггеры, выполненные на транзисторах, эмиттеры которых соединены с базой входного транзистора, базой опорного транзистора и шиной

Нулевого потенциала, коллекторы входного

so транзистора подключены соответственно к базам вторых транзисторов триггеров, эмиттер входного транзистора соединен с вход=-ной шиной, эмиттер опорного транзистора соединен с шиной питания, выходную и тактовую шинь1, отличающаяся тем, что, с целью повышения быстродействия ячейки, в нее введены транзисторы связи, токозадающий транзистор, блокировочный транзистор и выходные транзисторы, коллекторы кото70552, рых соединены с выходной шиной, эмиттеры выходных транзисторов соединены с базами первых транзисторов триггеров и с первыми коллекторами токозадающего транзистора, а базы — с базами транзисторов связи, с эмиттером блокировочного транзистора, базой токозадающего транзистора и шиной нулевого потенциала, эмиттеры транзисторов связи соединены с коллекторами опорного транзистора и коллекторами блокировочного транзистора, коллекторы транзисторов связи подключены к базам первых транзисторов триггеров, вторые коллекторы токозадаюгцего транзистора соединены с базами вторых транзисторов триггеров, база блокировочного транзистора соединена с эмиттером токозадающего транзистора и тактовой шиной.

Источники инормации, принятые во внимание

1. Патент Франции № 2131960, кл. G 11 С 19/00, 1972.

2. Авторское свидетел ьство СССР по за я в ке № 2365960/21, кл. Н 01 L 29/00, 1976 (прототип) ., 05:1?;)

О Hp/õ.

Составитель А. Воронин

Редактор Б. Герцен Техред М. Левицкая Корректор Е. Лукач

Заказ 8044/56 Тираж 681 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений н открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4