Формирователь ступенчатого напряжения

Иллюстрации

Показать всеРеферат

ОП ИКАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ 705654

Союз Советских

Социалистнческих

Республмк (6l ) Дополнительное к авт. свнд-ву— (22) Заявлено l7.03.78 (2l) 2590843/l8-2! (5!) М. Кл.е с присоединением заявки №

Н 03 К 4 02

Гесударствехньй хемктет

СССР ла делам хзабретекхй ю открытхх (23) Приоритет—

Опубликовано 25.l2.79. Бюллетень №47 (53) УДК 621.373 (088.8) Дата опубликования описания 26.!2.79

В. Г. Демидов и В. В, Нечаев (72) Авторы изобретения (7l) Заявитель (54) ФОРМИРОВАТЕЛЪ СТУПЕНЧАТОГО НАПРЯЖЕНИЯ

Изобретение относится к импульсной технике и может быть использовано при создании формирователей ступенчатого напряжения с высокой временной стабильностью параметров выходного сигнала, Извеетен формирователь ступенчатого напряжения, содержащий ключевые элементы, управляющие входы которых подключены к выходам управляющего генератора, резисторные матрицы, соединенные через ключи с источником напряжения f тI.

Недостатком устройства является его низкая надежность и ограниченные функциональные возможности.

Известен формирователь ступенчатого напряжения, содержащий входной ключ, вход которого соединен с источником входного напряжения, запоминающий элемент и тактовый генератор, первый и второй выходы которого соединены соответственно с управляющими входами запоминающего элемента и входного ключа (2).

Недостатком устройства является его низкая временная стабильность работы.

Цель изобретения — повышение временной стабильности.

Поставленная цель достигается тем, что в формирователь ступенчатого напряжения, содержащий входной ключ, вход которого соединен с источником входного напряжения запоминающий элемент и тактовый генератор, первый и второй выходы которого соединены соответственно с управляющими Uxoдами запоминающего элемента и входного ключа, введены сумматор, дополнительный запоминающий элемент, первый и второй выходные ключи, входы которых соединены соответственно с выходами запоминаюцтего элемента и дополнительного запоминающего элемента, выходы подключены к первому входу сумматора, второй вход которого соединен с выходом входного ключа, а выход сумматора соединен с входами запоминающего и дополнительного запоминающего элементов, причем управляющие входы первого и второго выходных ключей и дополнительного запоминающего элемента подключены соответственно к третьему, четвертому и пятому выходам тактового генератора.

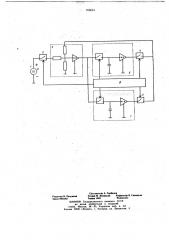

На чертеже дана принципиальная схема устройства.

5 - Ю Ф 1 4*à — АБМЛ I

705654

Устроиство содержит источник 1 входного напряжения, входной ключ 2, сумматор

3, первый и второй выходные ключи 4, 5,,запоминающий. элемент 6, дополнительный запоминающий элемент 7, тактовый генератор 8.

Устройство работает следующим образом.

Генератор 8 формирует два импуЛьсных напряжения, сдвинутых на 180 .

Первое напряжение управляет работой ключей 2, 4 и ключа элемента 7, а второе напряжение управляет работой ключа 5 и ключа элемента 8. При положительном импульсе ключи замыкаются, а при отрицательном — размыкаются.

Сумматор 3 имеет по каждому входу коэффициент передачи, равный единице. Конденсаторы перед включением схемы разряжены, При поступлении первого управляющего импуЛьса замыкаются ключи 2, 4 и ключ элемента 7. На выходе сумматора 3 устанавливается напряжение. При этом конденсатор запоминающего элемента ? заряжается через малое выходное сопротивление сумматора 3 до напряжения U. Параметры схемы выбраны так, чтобы выполнились соотношения

° К; С < < (1); RIa Ñ >> c, где К; — выходное сопротивление сумма- тора 3;

С вЂ” емкость запоминающего конденсатора;

V — длительность управляющего импульса;

Квх — входное сопротивление"согласующего усилителя.

При выполнении первого неравенства напряжение, до которого заряжается конденсатор не будет зависеть от изменения величины его емкости, а при выполнении второго неравенства напряжение на конденсаторе будет оставаться неизменным в течение вре1 мени с, когда ключ запоминающего устройства разомкнут. Таким образом, в течение первого периода управляющих импульсов напряжение на выходе запоминающего элемента 7 остается неизменным и равным U.

При открывании ключа 5 и ключа элемента 8 остальные ключи запираются. Напряжение, равное с выхода элемента 7 через ключ 5 поступает на вход сумматора 3, конденсатор элемента 6 заряжается до напряжения U. Напряжение на выходе устройства 4 остается неизменным в течение некоторого интервала времени. Далее вновь замыкаются ключи 2, 4, ключ элемента 7. При этом на выходе сумматора устанавливается напряжение, равное 2U, так как на каждый вход сумматора через ключи 2 и 4 подаются напряжения, равные U.

Напряжение с выхода сумматора запи сывается элементом 7 и на выходе усиля теля которого устанавливается напряжение

2U. Г1ри следующем такте это напряжение вновь переписывается в элемент 6. Далее процессы повторяются с периодом 2». В результате этого на выходах элементов 6, 7 формируются ступенчатые напряжения, сдвинутые на время г, Далее снимаются управляющие импуль-. сы и запираются ключи 2, 4 и 5. В результате этого на выходе сумматора устанавливается нулевой потенциал и при очередном замыкании ключей элементов 6 и 7 конденсаторы обнуляются. Начиная с этого момента времени формируется новый цикл ступенчатого напряжения.

Нестабильность приращения выходного напряжения в предложенном формирователе определяется суммарной нестабильностью коэффициентов передачи сумматора и согласующих усилителей запоминающих устройств.

При использовании высокоточных резисторов легко достижима суммарная нестабильность коэффициентов передачи к концу срока хранения, не превышающая 1%.

Таким образом, при использовании предложенной схемы формирователя исключена у временная нестабильность параметров схемы, обусловленная временной нестабильностью емкости конденсаторов, что позволило более чем на порядок повысить временную стабильность параметров выходного сигнала формирователя.

3О

Формула изобретения

Формирователь ступенчатого напряжения, содержащий входной ключ, вход которого соединен с источником входного напряжения, запоминающий элемент и тактовый генератор, первыл и второй выходы которого соединены соответственно с управляющими входами запоминающего элемента и входного ключа, отличающийся тем, что, с целью повышения временной стабильности, в него

4р введены сумматор, дополнительный запоминающий элемент, первый и второй выходные ключи, входы которых соединены соответственно с выходами запоминающего элемента, выходы подключены к первому входу сумматора, второй вход которого соединен с выходом входного ключа, а выход сумматора соединен с входами запоминающего и дополнительного запоминающего элементов, причем управляющие входы первого и второго выходных ключей и дополнительного зад поминающего элемента подключены соответственно к третьему, четвертому и пятому выходам тактового генератора.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельс1во СССР № 512572, кл. Н 03 К 4/02, 30.04.76.

2. Авторское свидетельство С(.СР № 549882, кл. Н 03 К 4/62, Or,()7.77. прототй и.

105654

СоставитеЛь А. Горбачев

Редактор Н. Разумова Тетерев М, Левицкав 3(орректор В. Сииивкав

Заказ 8053/62 Твра4к 3060 Поднисиое

ЦНИИ ПИ Государственного комитета СССР по делам изобретений и открытий

133035; Москва, )К вЂ” 35, Раушская наб., д. 4/5

Филиал OllA «Патент», r. Ужгород, ул, Проектнан, 4